Research

48 V to Point-of-Load Vertical Power Delivery for Next-Generation Ultra-High-Power Processors

High-performance processors (e.g., GPUs, CPUs, ASICs, etc.) serve as the engine of data center computing platforms and the foundation for technical progress in areas such as artificial intelligence, deep learning, autonomous vehicles, and numerous other applications. In recent years, the electric power consumption of processors has increased dramatically and is approaching 1000 W due to the fast-growing demand for greater computational power. For example, as shown in Fig. 1, the thermal design power (TDP) of NVIDIA data center GPUs has grown by 10 times in the past decade, from 106 W to 1000 W. And just in the past three years alone, the TDP has more than doubled.

As power levels increase, the 48-V bus architecture is gradually replacing the legacy 12-V dc bus in modern data centers since the power distribution losses (\(i^2R\) losses) decrease by sixteen-fold with the quadrupling of the bus voltage. This makes the design of the voltage regulation modules (VRMs) responsible for the 48 V to point-of-load (PoL) power conversion more challenging with a quadrupled voltage conversion burden. In addition to a large conversion ratio of 48-to-1 or higher, the VRMs for next-generation ultra-high power processors should be capable of sourcing ultra-high current (\(\geqslant 1000\) A) at low supply voltage (\(\leqslant 1.0\) V) and achieving high power density, high efficiency, and fast dynamic response.

The picture of the NVIDIA H100 tensor core GPU in Fig. 1 shows the existing two-stage lateral power delivery (LPD) architecture where the current flowing out of the VRMs needs to travel a long distance to the processor pins, leading to a large power distribution network (PDN). With a load current beyond 1000 A, the high PDN resistance can lead to a dramatic voltage drop and unacceptable conduction losses, which significantly limits processor performance, reduces system energy efficiency, and hinders data center decarbonization. Moreover, the resulting low efficiency necessitates a larger size of the thermal management solution, which is presently a bottleneck of system densification.

In pursuit of a more efficient and compact alternative to the existing two-stage LPD solution for next-generation ultra-high-power processors, this work focuses on an ultra-high-current 48-V-to-1-V hybrid SC voltage regulator, named the switching bus converter (SBC), to address the aforementioned challenges through single-stage vertical power delivery (VPD), as illustrated in Fig. 2. In this single-stage VPD solution, the proposed SBC is placed on the bottom side of the motherboard directly underneath the processor so that it can deliver the ultra-high current vertically to the top side through vias, which greatly reduces the PDN size and PDN losses and saves the valuable topside area on the motherboard for high-speed communication and memories. Moreover, merging two conversion stages into one single stage reduces power conversion losses and eliminates the need for dc bus capacitors, which effectively improves overall system efficiency and power density.

Selected publications: [Zhu TPEL’24a, Zhu TPEL’24b, Zhu OJPEL’24]

Modeling and Control of Pure and Resonant Switched-Capacitor Converters

Modeling and Analysis

In pre-existing analytical models of pure and resonant switched-capacitor (SC) converters, the input and output capacitances (\(C_{\mathrm{in}}\) and \(C_{\mathrm{out}}\)) have long been assumed to be infinitely large so that the input and output can be modeled as ideal voltage sources. However, in practice, the terminal capacitances can be insufficient to ensure ideal input and output behaviors due to space and cost constraints. This work reveals that finite terminal capacitances can have considerable effects on the output impedance (\(R_{\mathrm{out}}\)) and overall efficiency of SC converters.

Selected publications: [Zhu TPEL’23, Zhu COMPEL’21a, Zhu APEC’21]

Control

This work proposes a multi-resonant compensation control (MRCC) technique for resonant switched-capacitor (ReSC) converters that can adaptively compensate for the negative effects of finite terminal capacitances by ensuring multi-resonant and full zero current switching (ZCS) operation with adjusted duty ratio and switching frequency, demonstrating a more than 5x terminal capacitance reduction without harming the overall efficiency compared to the conventional control technique.

Selected publication: [Zhu COMPEL’21b]

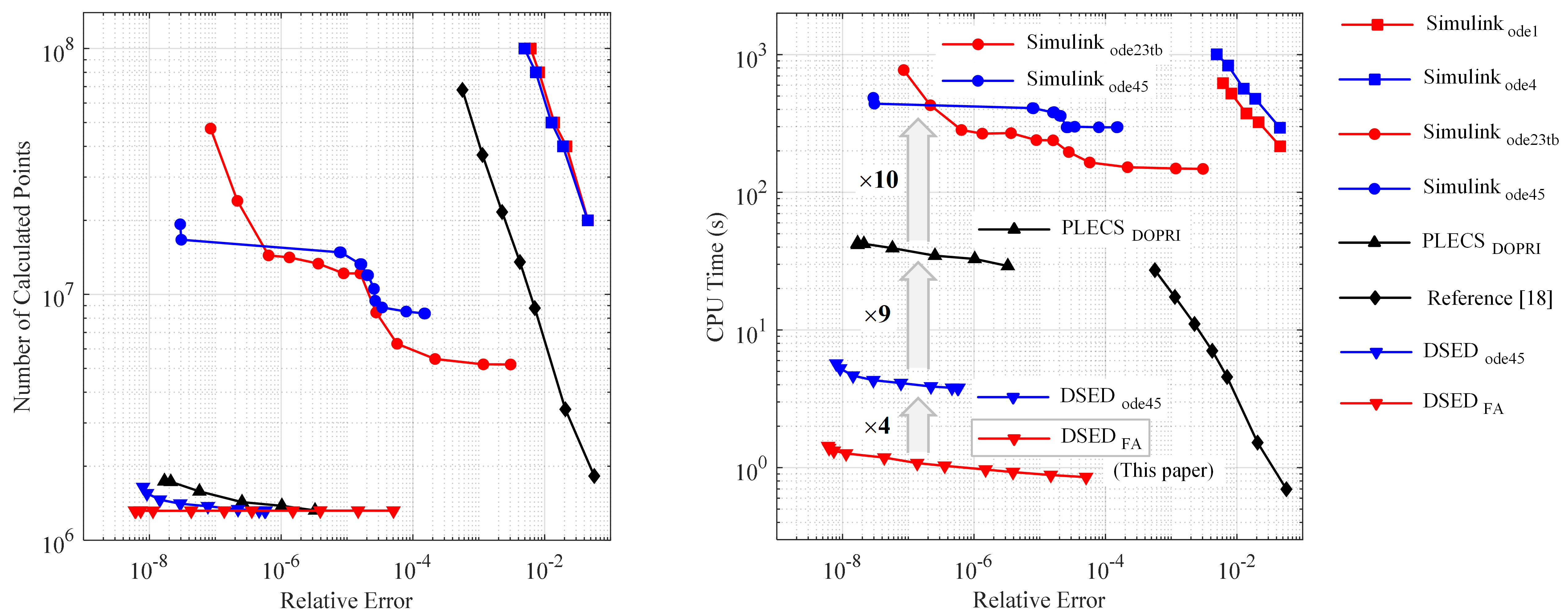

Discrete State Event-Driven (DSED) Simulation of Power Electronics Systems

The commercial simulation software DSIM is developed based on this work.

Selected publications: [Zhu TPEL’19, Zhao MPEL’20, Shi TIE’21, Yu TPEL’21]