LBNL-59999

# Software Roadmap to Plug and Play Petaflop/s

Editor: Bill Kramer (wtkramer@lbl.gov)

Contributions from: Jonathan Carter, David Skinner, Lenny Oliker, Parry Husbands, Paul Hargrove, John Shalf, Osni Marques, Esmond Ng, Tony Drummond, Kathy Yelick, Bill Kramer

> NERSC Center and Computational Research Divisions Ernest Orlando Lawrence Berkeley National Laboratory University of California Berkeley, California 94720

> > July 2006

This work was supported by the Director, Office of Science, Office of Advanced Scientific Computing Research of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

# Software Roadmap to Plug and Play Petaflop/s

In the next five years, the DOE expects to build systems that approach a petaflop in scale. In the near term (two years), DOE will have several "near-petaflops" systems that are 10% to 25% of a peraflop-scale system. A common feature of these precursors to petaflop systems (such as the Cray XT3 or the IBM BlueGene/L) is that they rely on an unprecedented degree of concurrency, which puts stress on every aspect of HPC system design. Such complex systems will likely break current "best practices" for fault resilience, I/O scaling, and debugging, and even raise fundamental questions about languages and application programming models. It is important that potential problems are anticipated far enough in advance that they can be addressed in time to prepare the way for petaflop-scale systems. DOE asked us to formulate our response by considering the following four questions:

- 1. What software is on a critical path to make the systems work?

- 2. What are the strengths/weaknesses of the vendors and of existing vendor solutions?

- 3. What are the local strengths at the labs? (list of areas of expertise and names of people)

- 4. Who are other key players who will play a role and can help? (other labs, e.g., efforts at Sandia for Red Storm)

Our response is organized as follows.

**Section 1** provides a high-level answer to question #1, "What software is on the critical path to make the systems work?" We broadened the response to include both hardware and software issues because the two are so intricately entwined on systems of this scale. We also differentiate near-term (2007) challenges from those that we anticipate in the long term (2008 and beyond).

**Section 2** addresses question #2, "Describe the strengths and weaknesses of the vendors and existing vendor solutions," using data collected from the NERSC-5 procurement.

Section 3 addresses question #3, "What are the local strengths at the labs? (list of areas of expertise and names of people)" by describing the local strengths at LBNL and NERSC for responding to the challenges of petascale computing described in the earlier sections.

Section 4 addresses question #4, "Who are other key players who will play a role and can help? (other labs, e.g., efforts at Sandia for Red Storm)" by identifying key players at other institutions who can be considered key partners for addressing the problems posed in earlier sections.

**Section 5** provides supplemental information regarding NERSC's effort to use non-invasive workload profiling to identify application requirements for future systems. The data collected by NERSC may be valuable for proactively identifying bottlenecks in current systems and anticipating future application requirements.

**Section 6** describes a set of codes that provide good representation of the application requirements of the broader DOE scientific community. The success of these codes is a bellwether for the overall success of these computing platforms for DOE scientific applications.

**Section** 7 is a comprehensive production software requirements checklist that was derived from the experience of the NERSC-3, NERSC-4, and NERSC-5 procurement teams. It presents an extremely detailed view of the software requirements for a fully functional petaflop-scale system environment. It also includes an assessment of how emerging near-petaflop systems (XT3, BG/L, Power SP) conform or fail to conform to these requirements.

# 1. Software Needs for Petascale and Near Petascale Computing

In the sections below we characterize the potential deficiencies in system and application software that will exist in the 2007 timeframe for the three high performance computing (HPC) architectures of interest to the Office of Science. Section 1.1 summarizes the major issues. Section 1.2 looks at longer-term issues that must be addressed before petaflop systems can reach a usable state.

## 1.1. Critical Issues for Near Petascale (circa 2007)

The following issues lie on the critical path for success of near-petaflops systems in the near term.

• Fault Tolerance: The emerging crop of near-petascale HPC systems contain an order of magnitude more components than current-generation systems. Current software and hardware approaches are inadequate to the task of managing and containing the failure modes that are likely to exist in such complex systems. Fault tolerance is primarily limited by the fragile software environment. For example, once an XT3 router chip fails, the torus cannot dynamically change routing; but more importantly, the router, once fixed, cannot be returned to service without a full reboot.<sup>1</sup> The BG/L has similar issues. Hence, the system resources slowly decay until enough nodes are offline that system managers shut down and reboot.

To address this issue, software reliability has to be improved. The majority of system-wide outages at NERSC are due to software failures. A fundamental review of system software is needed with the goal of reducing complexity and increasing reliability. Ways to proactively judge software reliability will be critical to deciding where resources should be deployed. Attention to fault tolerance in future software/hardware design must rise to a top priority in order to ensure the success of systems that are 10x larger than today's implementations.

- MPI and Support for Legacy Programming Models: Efficient MPI implementations0 are necessary at increased size. The workloads at NERSC and other Office of Science labs show that most codes can work effectively at the scale of 512 to 4096 processors using MPI. The systems in 2007 will have four times the number of CPUs. The current investment in science codes has to be preserved, so MPI will have to operate effectively at the scale of 10,000–40,000 tasks. Support for tools and optimizations of legacy programming models must continue even on petaflop-scale systems. Even if all new HPC software development were to shift exclusively to advanced parallel programming languages, it will still take more than a decade to shift the existing HPC software infrastructure over to the new programming methods.

- **Public Interfaces for Lightweight Communication:** As the number of processors grows and relative cost of the network increases, applications that are communication-intensive must be optimized to make effective use of network resources. Hardware support such as remote direct memory access (RDMA) offers opportunities to overlap communication with computation using lightweight one-sided communication, but interfaces below MPI are often kept proprietary. Hardware issues, such as lack of cache-coherence between network processors and compute processors within a node, also interfere with the ability to use RDMA. The use of unmodified commodity operating systems like Linux can also add overhead due to virtual memory management and other services. Benchmarking efforts (e.g., HPC Challenge GUPS [giga updates per second] benchmark) on the BlueGene/L machine have utilized non-public network interfaces. The LBNL/UC Berkeley Unified Parallel C (UPC) group and the PNNL Aggregate Remote Memory Copy Interface (ARMCI) group have demonstrated the value of RDMA-based benchmarks in both microbenchmarks and application-level algorithms.<sup>2</sup> *Public lightweight communication interfaces*.

<sup>&</sup>lt;sup>1</sup> Note that the XT3 cannot do hot swaps either, so an entire rack needs to be powered down, losing 96 nodes.

<sup>&</sup>lt;sup>2</sup> See <u>http://gasnet.cs.berkeley.edu/performance</u> for microbenchmark numbers and "Optimizing Bandwidth Limited Problems Using One-Sided Communication and Overlap," C. Bell, D. Bonachea, R. Nishtala, K. Yelick, 20th International Parallel and Distributed Processing Symposium (IPDPS), 2006.

are needed to optimize public domain implementations of MPI as well as global address space models (below) in order to expose the best available network performance on each machine.

- Global Address Space Models: While we believe support for legacy programming models such as MPI and OpenMP is important, efficient implementations of current-generation global address space models like UPC, Co-Array Fortran (CAF), and Global Arrays (GA) provide a user-level programming abstraction for the efficient one-sided communication described above. The language-based models offer an advantage over libraries, because they expose parallel constructs to automated optimization and reorganization by the compiler. Otherwise, the semantic meanings of application program interface (API) calls (such as MPI) are opaque to the compiler's optimizer and therefore cannot be optimized in any fashion by the compiler. *Global memory languages are poised to play an important role now (in the near-petascale time range) for enabling effective use of petaflop-scale systems. UPC compilers are available on every major HPC system architecture, from PC clusters to the X1e, including prototypes for the XT3 and BG/L. LBNL is partnering with Cray and Intrepid to provide optimized UPC support for the XT3; and IBM has an internal research compiler for UPC on BG/L. CAF has a portable open-source compiler from Rice, and GA is available from PNNL. These languages have nearly achieved the level of ubiquity necessary to change the software ecosystem.*

- Stable Parallel Filesystems: Current global, parallel filesystems are demonstrated to run effectively at the scale of 2,000 clients. There are no other practical solutions in the near term aside from GPFS and Lustre. Lustre has shown significant scaling and reliability issues. GPFS, while showing good scaling, excellent performance, and excellent reliability for concurrencies up to 2,000 clients, is just now starting to move onto some of the near-petascale architectures. However, GPFS performance and reliability remains relatively unexplored at concurrencies in excess of 2,000 clients. If the current implementations are just scaled to the number of compute nodes in the prepetaflop systems, it is likely that significant scaling issues will be encountered, even show-stopping problems. Several solutions need to be explored, including redesign of the filesystems and implementation of lightweight interfaces on compute nodes. *The filesystem problems identified in this section cannot be solved by the DOE Labs, even if the software is open-sourced. Any credible solution requires close collaboration between the labs and the two primary vendors who have developed scalable parallel I/O system technologies collaboration that is supported by funding to proactively target these issues.*

- Numerical Libraries: Additional focus is required to ensure the scalability of parallel libraries. Much of the current activity in tuning performance focuses on single processor performance, which will continue to be important; but higher-level performance issues such as communication performance, load imbalance, and synchronization overhead need to be addressed. The level of sophistication required for parallel libraries on petascale systems will be dramatically larger than on current lower-parallelism and flat interconnect topologies. Funding of advanced library development that *leads* rather than lags the deployment of these systems will be essential to ensure the systems are used effectively for scientific applications once they come online. HPC centers will need to work with library and tool developers to assemble software testbeds to test new platforms, document the results, and systematically accumulate a list of requirements and expertise on the software and platforms where it runs. Library and tool developers should be among the community of early pre-production users on the near-petascale systems, along with application-focused early users, and should aggressively use this access to port and test their libraries and tools and to identify problems at the level of the tools (such as numerical tool implementations, precision, etc.) and applications codes. Early detection and resolution of problems through consistent validations can make the science community more confident in petascale systems. Both users and library developers have underscored the need for robust software testbeds that allow them to proactively port their software to new platforms using smaller-scale early-release versions of candidate HPC system hardware. A program that enables centers to purchase non-production early/prototype hardware could play an important role in establishing advanced software testbeds to prepare our software infrastructure for eventual full-scale implementations based on the same system architecture.

- **Debugging:** There is no debugging solution for petascale systems. Totalview does not work for users above 1,000 tasks, and only works on one near-HPC system beyond 1,000 nodes. Furthermore, the Etnus cost model is extremely expensive at scale. Continuing in the current direction for development for this software technology is untenable. *In the short term, it will be necessary to push vendors such as Etnus to extend the capabilities of Totalview to support larger-scale platforms, but the costs may be impractical. Ultimately this issue requires renewed exploration of alternative approaches to debugging at massive concurrency. Targeted funding is required to reinvigorate the research pipeline in order to spawn new ideas in this area. This point is explored in more depth in section 1.2 as a long-term issue.*

- Checkpoint/Restart: Operationally, C/R provides many advantages that make large systems more effective. By implementing C/R on both the Cray T3E and the IBM SP, NERSC increased its ability to run the right job at the right time, allowing long-running jobs while still providing fair throughput and reducing the impact of system shutdowns. C/R is feasible at scale on all the systems, but the necessary software is only available for the IBM Power architecture at this time. Linux C/R, developed through the DOE FastOS effort, may find its way into the XT3 and BG/L compute nodes if and when they move from microkernels to stripped-down Linux kernels. Meiosys is another possible implementation of C/R being considered by at least one vendor. *While this move presents an opportunity for the Linux C/R efforts, it will require software integration and support to ensure production-quality services at this scale. It will require renewed support for vendor/laboratory collaborations to bring this work to fruition.*

The following problems are lower priority. They will greatly affect the usability and efficiency of the system, but will not necessarily be show-stoppers to making systems work for production-quality science. Systems without these functions merely waste DOE effort invested in these architectures.

- Changing Memory Balance: Memory is one of the most expensive and power-hungry components of systems. For the past 15 years, systems have consistently hovered around a byte-per-flop (B/F) ratio of 0.5 byte per peak flop delivered by the system, despite the lack of firm scientific grounding for this ratio. Historically it has been associated with Amdahl's heuristic design point for mainframes that called for one byte of memory per instruction/sec<sup>3</sup> processing performance. As systems move to having thousands to tens of thousands of nodes, it may not be practical to continue the current memory balances on future systems and still have enough funding to reach the computational goals. It is unclear to what extent this design trade-off would impact the design of future applications and numerical algorithms. The scientific computing community needs to develop the appropriate framework to address this issue in a rational and scientific manner. The process can be informed by the kind of in-depth analysis of algorithms being performed by groups such as Oliker's benchmarking team at LBNL; Worley, Dunigan and Vetter at ORNL; and the SciDAC PERC collaboration. These efforts can provide the ultimate answer to this question if it is identified as an important issue, but must be chartered explicitly to investigate the B/F ratio for the Office of Science workload.

- Efficient Job Migration and Torus Packing: In order to reduce performance variability on architectures with a 3D torus topology, jobs must be given topologically contiguous sections of the torus. As jobs are scheduled and retired, gaps develop in the torus that must be removed by migrating running jobs to repack the torus. Such migrations require many of the same capabilities as OS-initiated checkpoint/restart, but the job state need not be written to and from disk. Integrating efficient job migration and job packing algorithms with the batch subsystem will be important for efficient utilization of these system architectures. NERSC implemented such capabilities for the T3E/900 system (mcurie). Recreating this capability requires much of the C/R capabilities as a minimum requirement, and must be complemented by an open/modular resource management system that can be modified to direct the job suspension and process migration facilities to effect job migration in response to current job scheduling conditions. The XT3 will present a problem in this regard due to lack of explicit control of job layout in the current system software implementation.

<sup>&</sup>lt;sup>3</sup> This is a non-floating-point measure.

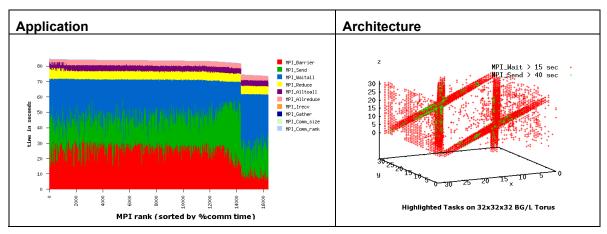

- Job Mapping: BG/L and the XT3 require very complex job mappings for anything except the simplest of problems.<sup>4</sup> Currently users have little information to select job mappings other than the canonical mapping. There are few tools to assist with selecting a better mapping, much less automatically generating map files for the user (who is left to write scripts to generate the map files, if possible). Currently available monitoring tools do not provide useful advice on how to improve the job mapping or are not practical for full-scale utilization. *Funding to develop lightweight, non-invasive systems for collecting communication and performance data from the jobs while they run at production scale will be essential to make more efficient use of these resources. Such performance monitoring frameworks must be non-invasive enough that they can be used for all jobs run on the system rather than as an offline performance optimization/tuning step (a key example is described in section 5 of this document). Combining these capabilities with the facilities to re-pack jobs on the interconnection network will greatly improve resource utilization efficiency.*

- **Parallel I/O:** MPI I/O may be insufficient at this scale unless POSIX<sup>5</sup> semantics can be relaxed. Some form of asynchronous I/O or other support for relaxed POSIX compliance will be critical to scalable I/O performance. This capability must be exposed efficiently via mainstream I/O libraries like Parallel NetCDF or parallelHDF5. This is not a show-stopper because users will continue to follow current practice of writing one file per processor. The result of such user behavior is overblown storage system performance requirements (such as the 30k file creates/sec required by DARPA HPCS) that will otherwise increase costs and reduce the efficiency of archival storage systems such as HPSS. *DOE labs can help by continuing R&D of parallel file formats and libraries such as MPI-I/O, more efficient parallel-I/O alternatives such as server-directed I/O, expanding the effectiveness and portability of parallel global filesystems that allow parallel writes to single files in an efficient manner, and refining a strategy for relaxed POSIX I/O. The latter requires close collaboration with industry and some organized effort to promote standardization of the approach across multiple platforms. Refinements in the lower-level parallel I/O strategy must be complemented by comparable funding for the incorporation of those advances into high-level file storage organization such as pHDF5 and Parallel NetCDF.*

- Visualization and Data Analysis Infrastructure: The ASC VIEWS program has provided a good set of baseline tools to attack this problem, such as LLNL VisIT. However, scientists require constant evolution in these baseline tools, tailoring their capabilities to meet the specialized visualization and data analysis requirements of their scientific domain. Tool development for data analysis and visualization is a continuous optimization process, requiring close collaboration with the domain scientists. VisIT offers a substrate to build upon that meets baseline needs, but such tools do not fix or extend themselves. Failure to consider the requirements of data analysis (both hardware and software resources) together with the large-scale system procurement will render any such system ineffective. DOE needs to preserve the investment in data analysis software infrastructure by continuing to fund collaborations between the providers of tools such as VisIT and Paraview, and the application stakeholders.

## 1.2. Critical Software Issues for Petascale (circa 2010)

#### 1.2.1. Fault Tolerance

The emerging set of near-petascale systems present a two-orders-of-magnitude leap in scale over typical systems today, in terms of hardware components (total number of disks, processors, and DRAM sticks),

<sup>&</sup>lt;sup>4</sup>Almasi, Bhanot, Gara, Gupta, Sexton, Walkup, Bulatov, Cook, de Supinski, Glosli, Grennough, Gygi, Kubota, Louis, Spelce, Streitz, Williams, Yates, Archer, Moreira, Rendelman, "Scaling physics and material science applications on a massively parallel Blue Gene/L system," Proceedings of the 19th Annual International Conference on Supercomputing, ICS 2005, Cambridge, Massachusetts, June 20–22, 2005, pp. 246–252.

<sup>&</sup>lt;sup>5</sup> Portable Operating System Interface for UNIX: a set of standards from IEEE and ISO that define how programs and operating systems interface with each other.

which is causing a critical gap to open up in fault management of these systems. Most of the systems have hardware designs that include many features that improve fault tolerance, but critical failure modes persist. Currently, systems software components for large-scale machines remain largely independent in their fault awareness and notification strategies. Software implementations remain fragile and do not support many of the hardware RAS (Reliability Availability Serviceability) features, so operationally, there is limited benefit for the hardware features. Faults can arise not just from the hardware but also from the OS, middleware, and application levels. Failures typically get reported using rudimentary error conditions such as "job failed," that provide little indication of the root cause of the failure. Given the overwhelming complexity of emerging petascale HPC applications, such opaque failure modes may well render the system unusable. Moreover, the multiple layers of software between application and computer have little to no opportunity to report, avoid, or correct the issue.

As mentioned above, the work in hardware fault tolerance is being limited by the fragile software. For example, once an XT3 router chip fails, the torus cannot dynamically change routing; but more importantly, the router, once fixed, cannot be returned to service without a full reboot.<sup>6</sup> The BG/L has similar issues. Hence, the system resources slowly decay until enough nodes are offline that system managers shut down and reboot.

To address this, software reliability has to be improved. The majority of system-wide outages at NERSC are due to software failures. A fundamental review of system software is needed with the goal of reducing complexity and increasing reliability. Ways to proactively judge software reliability will be critical to deciding where resources should be deployed.

Checkpoint/restart is a primary approach for fault-tolerance. It helps preserve application work and also helps system effectiveness when system shutdowns are needed. System-wide checkpoint becomes increasingly important because any solution that attempts to improve on fault-tolerance over C/R is likely to creep into the programming model. For instance, even in the most likely case of moving to application-initiated C/R, there is a need to annotate the minimum amount of state that must be preserved. Entire system C/R is feasible at scale.

However, the time to do a checkpoint is dominated by the size of memory and the I/O bandwidth. Since bandwidth increases more slowly than memory capacity, the time for checkpoints will continue to increase. Hence, it will become important to have incremental/journaled checkpoints. This is analogous to full and incremental checkpoints. You only do a full checkpoint for an application occasionally, and you do incremental checkpoints that reduce the amount of I/O needed. Restart would be longer, having to read in both the full and incremental checkpoints, but that may be more effective.

It is necessary for the batch system to handle the restart, but it is not possible to explain to a batch system in a concise manner where to locate the restart files and how to invoke the application to perform the restart unless there are some common guidelines to enforce uniformity. If you expect one processor failure every 10 minutes, it is a non-solution if the user must intervene in the restart process. Uniform software frameworks must be developed to support uniform application-level C/R if this approach is ever to be workable.

The problems with extending C/R to future systems suggest a need to build an infrastructure that enables systems to adapt to faults in a *holistic* manner. Such a system would provide common uniform event handling and notification mechanisms for fault-aware libraries and middleware. Applications would need to interface with these capabilities in a more seamless manner.

Attention to fault tolerance in future software/hardware design must rise to a top priority in order to ensure the success of systems that are 10x larger than today's implementations. The focus should be on detecting deviant behavior in addition to catastrophic failure. Whereas current system software error detection mechanisms remain largely independent of the error handling at system and hardware level, a more integrated approach to the detection, propagation, notification, recovery, and even prediction of errors conditions is necessary. Given the realities of component failure rates, applications and underlying system services will increasingly need to adapt to fault conditions and take defensive action to recover from faults

<sup>&</sup>lt;sup>6</sup> Note that the XT3 cannot do hot swaps either, so an entire rack needs to be powered down, losing 96 nodes.

rather than die with a cryptic error when any fault is detected. Methods like statistical learning theory should be explored to provide very early warning indicators from user behavior and application results.

More work on alternatives to C/R needs to be launched in the research community. Developing methods to proactively measure and predict reliability, particularly for software, is another research area. A holistic view of reliability demands that fault detection, notification, and recovery mechanisms be integrated across both the OS and application domain in a uniform manner in order to enable a more holistic and comprehensive approach to fault resilience.

#### 1.2.2. Application Coupling and Multiphysics Applications

Petascale computing platforms enable physical processes to be simulated with much higher fidelity. The structure of such computations will likely increase the number of applications requiring complex couplers to join simulation components that employ incompatible domain decompositions or underlying numerical algorithms to simulate a broader array of physical processes. There are many aspects of this problem that are now of interest. As the coupling of models becomes more complex, it becomes more prohibitive to simply combine two different codes into one; but rather the trend has been to develop software paradigms to make them interoperate (like MCT, DCT, CCA or other more specific software frameworks). However, the execution control part of the problem has not been optimally addressed by vendors or the middleware, given the complexity of the problem. So, we need to develop more robust versions of existing coupling toolkits and ways that one can control the launching of multi-executables that need to exchange model variables, fields, or data online, ensuring that these coupled models run scalably and reliably on massively concurrent systems. The capabilities of such systems are likely to make multi-physics couplers more common in the future.

#### 1.2.3. Analytics, Visualization, and Data Management

As we move towards larger-scale systems, the issue of data management (data storage and movement to different data storage resources) will become intimately entwined with every aspect of the data analysis and visualization process. There is a tendency to separate the concerns of data analysis from those of the core computing system, but this approach cannot be sustained on the largest-scale systems. The ASC program took pains to ensure that visualization and analysis requirements were intimately linked to each new system by suggesting the data analysis resources be provisioned as at least 10% of the scale of the primary computing system. Anecdotal evidence from the scientists served by the ASC program indicates this metric has served them well. The ASC metric for scaling data analysis resources as a fraction of the size of the primary computing platform should be examined to determine if the ratio makes sense for petaflop-scale systems. Likewise, investments in advanced and scalable visualization technology must be preserved through funding of joint development efforts between science groups and visualization technology providers. Otherwise, the current rewards system of these respective groups makes the natural emergence of effective data analysis solutions unlikely.

#### 1.2.4. Massively Parallel Programming Models

Most applications remain unprepared for the level of concurrency exposed in petascale systems and their precursors such as the XT3 and BG/L. Advanced programming languages will likely play an essential role in exposing/expressing enough concurrency to take advantage of the myriad of processors. The path to scalability is increasing the number of user-visible threads, because hardware techniques such as pipelining and instruction level parallelism have reached their practical limits.

Some significant issues are:

• Load Imbalance: Problems with any degree of irregularity or load imbalance such as unstructured grids (e.g., UMT2K), block-structured AMR (e.g., Chombo and SAMRAI), and sparse linear algebra (e.g., SuperLU, MUMPS) exhibit lower scalability with current methods. Application-level load imbalance will be exacerbated on petascale systems, as all processes must wait for the slowest to arrive at synchronization points, and the dynamic load balancing required

for some applications require asynchronous background communication or other techniques to hide their cost. Advanced dynamic partitioning software such as Zoltan and graph partitioners such as Metis can play a role in a software strategy to detect and react to load imbalance

- Small Messages: Increasing the number of processors in a system, especially in an environment with small memory per processor, will lead to smaller messages. The 3D FFT is an example where message sizes get smaller (send nprocs messages to each processor in 1/nprocs) as concurrency scales up. To do better at spreading communication over a longer period of time to reduce bisection bandwidth requirements, one must employ even smaller messages. The overhead associated with sending each message has a significant impact for small messages that are required to spread out the communication costs, as described in the Chen/Iancu/Yelick paper on fine-grained communication optimizations for UPC.<sup>7</sup> Current best practice is to aggregate messages into larger buffers, but that approach increases software complexity and cannot be extrapolated to systems with such massive concurrency. *Hardware that provides fast communication with low CPU overhead will allow for more effective use of networking hardware. In addition, these facilities must be exposed to user-level software, ideally in a common communication interface.*

- **Topology:** Codes with large global communication, like 3D FFT and particle-in-cell methods, require extra attention to communication locality and the topology of the underlying interconnection network. Experience with BG/L has already highlighted the important of topology optimizing communication performance, and this is likely to become more significant as machines scale. MPI libraries need to optimize for topology, and machines should expose information to allow application programmers to optimize as well.

- **Multithreading:** The primary path to exploiting hardware threading currently involves mixedmode OpenMP + MPI programming (OpenMP to exploit threading on each node and MPI to span the distributed memory domains). However, OpenMP offers a rather limited approach to expressing threading concepts that are completely disjoint from the considerations of the messagepassing model. Few programmers are willing to take the additional step of employing two-level parallelism in this manner. Languages that offer a more natural/readable approach to exposing parallelism are required. Vendors can implement Unified Parallel C (UPC) and Co-Array Fortran (CAF) in this time frame, but they offer only an interim solution to exposing the necessary degree of parallelism required to make petaflop-scale systems even marginally useable.

Recommendation: Continued development of advanced programming models in close collaboration with vendors and application scientists is essential to ensure that the hardware/software architecture for messaging on future systems will meet the needs of advanced programming models, and that the programming models meet the needs of the users. Cross-agency and vendor coordination is also essential to ensure ubiquity of emerging programming models.

#### 1.2.5. Libraries

Efficient libraries are essential for large-scale systems. There is too much software complexity for each individual application group to take on alone (unless their application is exceedingly simple). The community must leverage the numerical algorithm development and performance tuning work that goes in to library solutions.

The increasing sophistication of computer models together with the complexity of algorithms and computer architectures greatly inhibits progress towards optimized version of an application. In addition, a development team may already be faced with software intricacies that cannot be undertaken by the team alone. Together, all these issues may be even more challenging on large-scale systems.

Libraries can provide a convenient way for incorporating state-of-the-art computational technology into development efforts, with the additional benefit of alleviating many aspects of the development process and enabling testing of different techniques or implementations.

<sup>&</sup>lt;sup>7</sup> Wei-Yu Chen, Costin Iancu, Katherine A. Yelick, "Communication Optimizations for Fine-Grained UPC Applications," IEEE PACT 2005: 267–278.

While some users have been able to exploit serial libraries, e.g., calling non-parallel libraries such as FFTW within parallel applications, the degree of sophistication required to achieve scalable performance on mesh interconnects (such as the torus networks on BG/L and the XT3) far exceeds current requirements. This will necessitate more focus on the largest scale.

While library autotuning might be viable in some cases, overall it is likely to be impractical on large-scale systems since it may require increased validation and testing to make sure the libraries are functioning properly. The search space for autotuning is greatly expanded if parallelism is admitted into the search space on the same level with scalar optimizations. This may require a hierarchical approach to autotuning of parallel applications or it may require limiting the range of autotuning.

To identify the main libraries used in simulation codes, provide the resources for early porting of such libraries to emerging large-scale architectures; identify eventual bottlenecks in the libraries and recommend alternative solutions.

We reiterate the importance of providing targeted funding for massively concurrent system libraries and programming abstractions. The development of such libraries must anticipate the arrival of the systems (using smaller-scale proxies or early prototypes to assist in development) rather than spin up after such systems have been delivered. The lead time required for software development is considerable, so a close interaction between the research, evaluation, and prototype program and developers of advanced software technology is essential for the success of future systems.

#### 1.2.6. Debugging

Although some tools like Umpire<sup>8</sup> and MARMOT<sup>9</sup> have been developed to detect faulty use of MPI functionalities, it is fair to state that there is no practical debugging solution for problems scaled beyond thousands of processors. Although users do want to employ debugging functionalities on more than 512 processors, existing solutions such as Totalview are inadequate. To the best of our knowledge, there is currently is no effort underway to replace Totalview and there is little motivation for Etnus to invent and test for higher scales. At the same time, there are no responsive solutions in the pipeline from the research community. An alternative approach to debugging large-scale codes may be higher-level toolkits that go beyond stepping through code with interactive debuggers, print statements, and time stamps that are cumbersome to look at when running on hundreds of processors. There is a need for tools that can replicate scenarios and program failures with user-friendly interfaces.

#### 1.2.7. Operating System

OS interference is a well documented problem on systems such as ASCI White and NERSC-3. The microkernel approach on the XT3 and BG/L mitigates OS interference problems. However, XT3 and possibly BG/L will be moving to stripped-down Linux kernels. This has ramifications on reliability/uptime and possibly OS interference on large-scale systems, and requires additional planning and attention as we lead up to production system deployment. OS interference is potentially *very* dangerous, with show-stopping consequences if we do not proceed with deliberate caution and preparation.

While considered solid for desktop systems, the reliability of Linux on a massive scale remains questionable. Furthermore, the complex web of hardware/driver dependencies makes any OS upgrade or modification challenging for systems that use a Linux or UNIX base. The planned move of the XT3 and BG/L compute nodes from microkernels to Linux implementations presents a high degree of risk, particularly if the Linux community refuses (as they have done many times in the past) to adopt extensions that might improve the reliability and effectiveness of Linux on large-scale systems.

<sup>&</sup>lt;sup>8</sup> J. S. Vetter and B. R. de Supinski, "Dynamic Software Testing of MPI Applications with Umpire," Proc. SC2000: High Performance Networking and Computing Conf. (electronic publication), ACM/IEEE, 2000.

<sup>&</sup>lt;sup>9</sup> B. Krammer, M. S. Muller and M. M. Resch, "Runtime Checking of MPI Applications with MARMOT," ParCo 2005, minisymposium on Tools Support for Parallel Programming, Malaga, Spain, Sep. 12–16, 2005.

#### 1.2.8. Profiling and Performance Analysis

There are tools that have been used successfully to analyze performance data on thousands of processors. In particular, TAU has been used to generate and analyze profiling information of a CFD code on 16 K nodes on LLNL's BG/L. That same data was later replicated four times in order to simulate the profiling of the application on 64 K processors and test the scalability of TAU. The last version of Paraprof, TAU's visualizer, offers 3D view functionalities (such as triangle mesh plot and scatter plot) that can help users look into performance data obtained on a large number of processors.

Another solution for performance analysis is IPM (Integrated Performance Monitoring), which is discussed in detail in section 5. The primary contribution of IPM is that it presents a lightweight approach to application monitoring. The overheads (< 3% typically) are low enough to enable continuous monitoring and data collection for a system workload. This has enormous benefits for better characterizing the workload at a given center in order to feed back into the design requirements for future systems.

It remains to be investigated, however, how tools such as these behave on a wide set of large applications, the overhead resulting from their use, their performance, and their capability in helping the user understand enormous collections of profiling and tracing data.

#### 1.2.9. Parallel I/O

Parallel I/O for petascale systems raises several software issues:

- **Bandwidth:** In hardware, bandwidth is a factor of the number of I/O servers, the number and capabilities of the controllers, the number of storage units, and the number of connections from disk devices. Bandwidth also depends on the ability of the software to manage the control of operations. The software control is the primary area to attack, since the other constraints are a matter of buying more hardware.

- Reliability of the Underlying Storage Medium: High performance disk systems have a price point well above commodity disks. Much of the cost is in the controller, which has embedded software. Trying to use disks, such as SCSI, that have lower duty cycle design points raises reliability issues. Current filesystem software stacks will be unable to cope with the move to less reliable storage devices, so fault recovery and resilience pathways must be reexamined in the light of this impending hardware constraint.

- **Metadata Performance:** Standard operations such as simply running a cron job that purges old files (clean scratch) will be impractical on a filesystem with hundreds of millions of files.

- File Create Performance: HPCS 30 K file creates/sec is considered unreasonable, but may be a practical requirement for these systems unless concurrent file I/O performance problems are addressed.

Facility-Wide File Systems (FWFS)<sup>10</sup> provide consolidated storage for online user data, replacing traditional system-local parallel filesystems for home directories, scratch storage, and project storage. While an FWFS is external to all computational systems, it is mounted natively and at high performance. FWFS grow and evolve over time, serving several generations of computational systems.

The benefits of FWFS to scientific productivity are manifold. By providing a single unified namespace, FWFS will make it easier for users to manage their data across multiple systems. Users will no longer need to keep track of multiple copies of programs and data; they will no longer need to copy data between NERSC systems for pre- and post-processing. Storage utilization will become more efficient through decreased fragmentation. Computational resource utilization will become more efficient as users can more easily run jobs on an appropriate resource. Storage allocations (quotas) will become larger, because they will no longer be fragmented among several systems. FWFS will also provide improved methods of backing up user data that can mitigate disturbance to users when block backups are run.

<sup>&</sup>lt;sup>10</sup> In FY2005, NERSC began deployment of a Facility-Wide File System (FWFS)

Anticipated developments in filesystem technology will provide further benefits. It is expected that FWFS will provide Hierarchical Storage Management (HSM) functionality, in which data can be automatically migrated to and retrieved from tertiary storage. This will further improve scientific productivity by enabling the user perception of extremely large online disk (very large quotas) and making it unnecessary for users to manually transfer data to and from HPSS. Other possible technology enhancements include enhanced security, wide area access, and tighter integration with grid technologies.

GPFS is the leading candidate because it has performance, scalability, reliability, better security, can be geographically distributed, and is interfaced to two different archive systems. Unfortunately, GPFS is not ported to all potential petascale systems. Lustre is an evolving candidate that currently has no plans for archive integration and presents security concerns and reliability issues.

In the petascale domain, there will be tens to hundreds of terabytes of data files. Moving them between systems in a facility will be difficult and time consuming. Indeed, some project teams currently devote 0.5 to 1 FTE just to move files to the right place. *Hence it is essential that petascale vendors support filesystems that integrate well, and at high performance, into facility-wide filesystems. However, it is important to encourage some level of competition in this area as well, so DOE should fund work in at least two global, parallel filesystems.*

Alternatives to MPI/IO such as Server Directed I/O that were developed for the database community should be reconsidered. These approaches were more effective than the imperative approach of MPI-I/O because the data was committed to disk using fences that offer a greater opportunities to overlap computation with communication. It is unfortunate that the techniques were overlooked by the HPC community.

#### 1.2.10. Network I/O

Computational switches are based on very large frame (packet) sizes, typically 64 KB, and suffer performance degradation at lower sizes. Local-area networks based on Gigabit Ethernet can run up to 9 KB jumbo frames reliably for onsite mass storage and backups. The 9 KB frame size increases performance compared to standard Ethernet by reducing overhead and CPU load; but compared to 64 KB frames, it has lower performance and higher latency than computational switches. Wide-area networks typically are restricted to 1,500-byte frames because of the need to support millions of simultaneous connections, even though the main protocols — 10 Gigabit Ethernet, SONET, and ATM — will pass frames up to 9 KB.

This mismatch in maximum transfer unit (MTU) sizes, and more importantly the performance degradation that is associated with running small MTUs, makes it difficult to effectively integrate a massively parallel computer system into any networked environment. Furthermore, internal interconnects do not run IP but instead use switch-specific protocols such as LAPI and Portals. The two major approaches used to date have been to add an external interface into each node or to turn one or more computational nodes into gateway routers and have external traffic flow across the internal switch to these gateways.

Both of these approaches have major weaknesses. Petascale computing will require thousands to tens of thousands of nodes.<sup>11</sup> Adding an external gigabit interface to every compute node for external connectivity to data storage systems and other computational resources is not practical, nor will it allow single stream performance to increase above current levels, even though this has the best chance for meeting large aggregate bandwidth requirements. Using a compute node that has a connection to the internal switch fabric as well as multiple bonded Gigabit Ethernet interfaces or 10 Gb/s Ethernet as a router is logistically easier and potentially has better single stream performance, but aggregate performance will suffer, especially coupled with small MTU traffic on the computational switch. Further, not all systems have nodes that can drive 10 Gigabits at near optimal rates. Also, a compute node that has to run packets through its IP stack to divide the traffic into packets, generate packet headers, and perform flow and congestion control

<sup>&</sup>lt;sup>11</sup> C. William McCurdy, Rick Stevens, Horst Simon, et al., "Creating Science-Driven Computer Architecture: A New Path to Scientific Leadership," Lawrence Berkeley National Laboratory report LBNL/PUB-5483 (2002), http://www.nersc.gov/news/ArchDevProposal.5.01.pdf.

will never be able to keep up with the fastest switches and routers that just store and forward with all decisions in application-specific integrated circuit (ASIC).

One possible solution would be a Layer-7 router with a computational switch interface that could do the bridging, MTU repackaging, and load balancing. This would be directly connected onto the vendor's internal interconnect. No potential petascale vendor has this in plan. A more workable solution would be to modify a compute node to act like a high performance router. Most of the hardware components for modifying a compute node already exist or would be simple to create. A computational switch, such as a Federation SMA3 adapter, and a 10 Gigabit Ethernet card, both with sufficient field-programmable gate array (FPGA) space to offload the IP protocol, would limit the compute nodes duties to setting up remote direct memory access (RDMA) between the two interfaces. Frame fragmentation and coalescing are often done through TCP proxies but should be programmable in a reasonable amount of FPGA space, thus reducing the adverse impact of widely disparate MTUs.

#### 1.2.11. Transport Protocols

TCP's congestion control algorithm aims to fully utilize the network path yet be fair to other traffic. There are two types of losses in the network: random and congestion. If network traffic arrives at a router or network interface and there is not enough capacity left to buffer the packet, then the packet is discarded (congestion loss). In TCP, the receiver acknowledges data as it is received. When a sender receives three duplicate acknowledgements, it assumes that data has been lost, cuts its sending rate in half, and retransmits the data just above the duplicate acknowledgement. It then increases the sending rate by one each round-trip time until the next loss, and the cycle repeats. This algorithm is called additive increase, multiplicative decrease (AIMD). TCP also includes a slow start algorithm, which is used at the beginning of a TCP connection to double the sending rate each round-trip time until the first loss is detected. TCP uses a congestion window to track the sending rate that is allowed. If the buffer size for sockets is not sized appropriately for the network connection, the congestion window might be artificially limited or the receiver might be overrun. Ideally the buffer size is continually tuned to the optimal size. The Net100 project has created a workaround daemon to perform this dynamic tuning<sup>12</sup>.

Network gateway nodes are often the limiting factor in network performance from large systems. It is tempting to assume that the host throughput to and from the network is simply the slower of the I/O bus speed or the memory bus speed, but the reality is more complex. The real throughput that can be achieved in transferring data from the user memory on the machine to the network interface card is defined by adding (1) the time to copy data from user memory to the kernel memory across the memory bus and (2) the time to copy from the kernel memory to the network interface card. Typically it takes two memory bus cycles to copy data from the user memory to the kernel memory, and one I/O bus cycle to copy from the kernel memory to the network interface card. The number of memory bus cycles required to transfer a word from the kernel memory to the I/O bus is determined by dividing the memory bus speed by the I/O bus speed. So, the typical throughput between the user memory and the network interface of a typical PC is defined by the following equation:

Throughput =  $\frac{\text{MemoryBandwidth}}{2 + \frac{\text{MemoryClock}}{\text{IOBusClock}}}$  (1)

The analysis can be found in [<sup>13</sup>] but the bottom line is that most x86 systems with the fastest available memory and PCI bus are not able to provide enough I/O power to drive 10 Gb NIC at full speed. PCI Express systems will do better, but will still be insufficient in the petascale domain.

<sup>&</sup>lt;sup>12</sup> T. Dunigan, M. Mathis and B. Tierney, "A TCP Tuning Daemon," *Proceedings of SC2002*, November 2002; http://www-didc.lbl.gov/papers/net100.sc02.final.pdf.

<sup>&</sup>lt;sup>13</sup> William Kramer, Deborah A Agarwal, Arie Shoshani, Brent Draney, Guojin Jin, Gregory Butler and John Hules, "Deep Scientific Computing Requires Deep Data," IBM Journal on Research and Development, Volume 48, Number 2, March 2004.

Several mechanisms have been created to allow applications requiring high bandwidth to have priority access to the bandwidth. The most aggressive of these is to create a dedicated path for the traffic by reserving a dedicated link/circuit/channel. The best-known mechanisms for this include virtual circuits and RSVP. Another mechanism is to mark the traffic as priority; then each router in the path expedites the traffic. The standard method for this is to use a bandwidth broker to arbitrate the access to the bandwidth on a pair-wise basis. If the intervening routers agree to the priority path, then the packets get marked as priority as they enter the network, and each router in the path forward gives the packets preference over all other traffic. An alternative approach that has been proposed is use of priority ratings on traffic or reserving virtual circuits. Although prioritizing traffic has received a lot of attention, it has generally been impractical. It is likely that traffic requiring guaranteed bandwidth will need to reserve virtual circuits through the network. This does not, however, remove the need to find a transport protocol that can effectively make use of the dedicated bandwidth.

These mechanisms are not supported on the software roadmaps of petascale systems.

# 2. What Are the Strengths and Weaknesses of the Vendors and of Existing Vendor Solutions?

# 2.1. Cray XT3

| Issue                                                                                                                                                                                                                               | Mitigation                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The XT3 interconnect shows quite high latency<br>differences for very large installations. This is a<br>potential problem for parallel applications writers.                                                                        | It is not clear how much can be done with software<br>or communication libraries. It would seem ANL,<br>with their experience in MPI, might be best suited to<br>address this. NERSC/LBNL are best posed to offer<br>programming and algorithm expertise to science<br>projects.                                                                                                                          |  |

| The XT3 interconnect is quite fragile, with little<br>ability for software recovery. Once a node/router<br>goes out of service, it is not possible to return to<br>service without a full system boot.                              | This takes low-level system and interconnect<br>software work to improve. LBNL and ANL have<br>expertise in these areas                                                                                                                                                                                                                                                                                   |  |

| Lustre may have issues with stability, performance,<br>scaling, and interoperability as compared with other<br>high performance global parallel filesystem.                                                                         | NERSC/LBNL have several years of experience<br>with Lustre, GPFS, and other filesystems due to our<br>Global Unified Parallel File System (GUPFS) and<br>NERSC Global Filesystem (NGF) efforts. While<br>Lustre will be made reliable eventually, GPFS<br>appears to be a very feasible option and Cray is<br>open to it.                                                                                 |  |

| Cray lags behind in compliance for the latest Fortran standard.                                                                                                                                                                     | This is more complicated now that Pathscale has been purchased.                                                                                                                                                                                                                                                                                                                                           |  |

| Interconnect latency lags behind commodity<br>interconnect in this timeframe. While this is<br>software, it is very low-level software.                                                                                             | It is not clear how much can be done with software<br>or communication libraries. It would seem ANL,<br>with their experience in MPI, might be best suited to<br>address this. NERSC/LBNL are best posed to offer<br>programming and algorithm expertise to science<br>projects. LBNL's Berkeley Institute for<br>Performance Studies (BIPS) effort would be crucial<br>to understanding the limitations. |  |

| Memory available per MPI process is low compared<br>with other architectures. This may cause some<br>applications to have to be redone, and certainly puts<br>pressure on any system-level efforts.                                 | This is basically a programming and testing effort.                                                                                                                                                                                                                                                                                                                                                       |  |

| The successor to Catamount, Compute Node Linux (CNL), has an almost non-existent roadmap at this time. In particular, there are no requirements regarding memory and cpu cycle consumption.                                         | Cray has only general goals and plans for CNL.<br>LBNL, ANL, and ORNL all have expertise that<br>could help with implementing CNL. NERSC has<br>expertise in identifying and dealing with memory<br>and CPU intrusion of operating systems.                                                                                                                                                               |  |

| Basic user and job resource management controls<br>are very limited (quota, resource limits, etc.).<br>Advanced workload management features such as<br>checkpoint/restart, job migration, and preemption<br>have no clear roadmap. | NERSC implemented the first highly parallel<br>checkpoint/restart, and was the first site to use it on<br>IBM systems at scale, as well as implementing<br>excellent workload management methods. This<br>experience, combined with LBNL's Berkeley Lab<br>C/R (Hargrove and Duell), makes LBNL/NERSC<br>the best place to address this.                                                                  |  |

| Tools for large-scale debugging, analyzing, and      | Large-scale debugging has to be rethought from    |

|------------------------------------------------------|---------------------------------------------------|

| tuning are lacking. E.g., Totalview only scales to   | scratch. Totalview is a very expensive monopoly   |

| 512 CPUs at this time and will at best be at 1024 in | that is not really effective. ANL, ORNL, and LBNL |

| the 2007 timeframe, ~5–10% of the maximum job        | have expertise here                               |

| size.                                                |                                                   |

## 2.2. IBM Blue Gene

Note: BG/L is the system that NERSC/LBNL knows the least about. There are probably a lot more issues than listed here.

| Issue                                                                                                                                                                                           | Mitigation                                                                                                                                                                                                                                                                                                                               |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| With a choice of NPFS, Lustre, and GPFS, there is a<br>variety of high performance global parallel<br>filesystems available. The very large number of<br>processors could cause scaling issues. | NERSC/LBNL has several years of experience with<br>Lustre, GPFS, and other filesystems due to our<br>GUPFS and NGF effort.                                                                                                                                                                                                               |  |

| Specialized chip architecture requires compiler tuning not relevant to mainstream products.                                                                                                     | ANL and ORNL have expertise here                                                                                                                                                                                                                                                                                                         |  |

| Workload management software immature for<br>providing high utilization and throughput under a<br>workload with a wide range of concurrencies.                                                  | NERSC implemented the first highly parallel<br>checkpoint/restart, and was the first site to use it on<br>IBM systems at scale, as well as implementing<br>excellent workload management methods. This<br>experience, combined with LBNL's Berkeley Lab<br>C/R (Hargrove and Duell), makes LBNL/NERSC<br>the best place to address this. |  |

| Memory available per MPI process is low compared with other architectures.                                                                                                                      | This is basically a programming and testing effort.                                                                                                                                                                                                                                                                                      |  |

| Tools for large scale debugging, analyzing, and tuning are lacking.                                                                                                                             | Large-scale debugging has to be rethought from<br>scratch. Totalview is a very expensive monopoly<br>that is not really effective. ANL, ORNL, and LBNL<br>have expertise here.                                                                                                                                                           |  |

## 2.3. IBM Power

| Issue                                                                                                                                                                                                                                                                                        | Mitigation                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power5 architecture has high power, cooling, and<br>space requirements compared with other systems.<br>Power6 will probably be an improvement, but will<br>likely lag behind other systems.                                                                                                  | This is hardware design and not really addressable<br>in this time frame. ORNL and LBNL have expertise<br>designing advanced buildings for computers. |

| IBM Federation interconnect will be at the end of its<br>lifetime in this timeframe. Its fat-tree topology also<br>has higher costs than networks with a 3D torus<br>connectivity. The latency of the Federation<br>interconnect will not be any better than commodity<br>in this timeframe. | Not much to do here.                                                                                                                                  |

| AIX is known to be a heavyweight operating system both in terms of memory and cpu cycles consumed.                                                                                                                                                                                           | ANL's OS experience might help to implement a lightweight AIX.                                                                                        |

| Intrinsic barriers to application scaling exist in the<br>AIX operating system, such as system daemons,<br>lack of synchronization in OS images. | LBNL, ANL, and ORNL all have expertise that<br>could help with implementing CNL. NERSC has<br>expertise in identifying and dealing with memory<br>and CPU intrusion of operating systems. |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tools for large scale debugging, analyzing and tuning are lacking.                                                                               | Large scale debugging has to be rethought from<br>scratch. Totalview is a very expensive monopoly<br>that is not really effective. ANL, ORNL, and LBNL<br>have expertise here             |

## 2.4. General Issues

| Issue                                                                                                                                                                                                                                                              | Mitigation                                                                                                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| System administration and resource management.                                                                                                                                                                                                                     | NERSC and ORNL have experience in making large systems work with effective system administration.                                                                 |  |

| High performance MPI collective operations and support for overlapped computation and communication activity.                                                                                                                                                      | ANL would be a national place to work on this.<br>LBNL's BIPS also has expertise that could be<br>applied.                                                        |  |

| Security: None of the systems provide anything new<br>in security beyond standard Linux/UNIX. AIX has<br>some advanced features, but some are not<br>compatible with open standards (e.g., OpenLDAP).<br>BG/L and the XT3 have given little effort to<br>security. | LBNL and NERSC have expertise in both providing<br>open access to systems without advanced security<br>features, as well as working to implement new<br>features. |  |

| Advanced languages: Cray and IBM are interested<br>in UPC but not willing to completely support it.                                                                                                                                                                | LBNL has extensive expertise in UPC.                                                                                                                              |  |

# 3. What Are the Local Strengths at the Labs?

## 3.1. LBNL Strengths

#### 3.1.1. Large-Scale System Management

Nick Cardo, Tina Butler, Jim Craw, Bill Kramer: NERSC has demonstrated the ability manage large-scale systems to achieve a variety of goals, from high utilization to high levels of time going to large jobs. NERSC has a history of fielding early production systems and making them highly effective for science.

#### 3.1.2. Large-Scale Data Management

Greg Butler, Brent Draney, Cary Whitney, Will Baird, Damian Hazen, Howard Walter: NERSC is one of the development sites for HPSS and operates one of the largest data repositories. NERSC is also the first site to implement a facility-wide global filesystem across multiple architectures. This is complemented by NERSC's ability for end-to-end network tuning.

#### 3.1.3. Large-Scale Application Improvement

Jonathan Carter, David Skinner, Richard Gerber, Francesca Verdier: NERSC's expertise in scalability and optimization has enabled a number of applications to reach and exceed the 1,000-processor scale.

#### 3.1.4. Languages

Kathy Yelick, Parry Husbands, Costin Iancu: UPC and Titanium language development. Evaluation of advanced HPC languages (with Rusty Lusk at ANL) as part of the High Performance Languages effort.

#### 3.1.5. Analytics and Data Management

Wes Bethel: Leads visualization and analytics for NERSC and LBNL.

Arie Shoshani: Leads the SciDAC Scientific Data Management Center and focuses on data management for the scientific community running on the largest-scale computing systems.

#### 3.1.6. Interconnect Architecture and Software

Jason Duell, Michael Welcome, Parry Husbands, etc.: GASNet. Experience with developing efficient runtime layers for single-sided messaging for UPC on a wide array of systems. Development of very efficient runtime layer and software for one-sided communication.

David Skinner, Leonid Oliker, John Shalf, Ali Pinar: Analysis of HPC interconnect performance on largescale systems using Skinner's IPM. HFAST interconnect architecture.

#### 3.1.7. Libraries

Esmond Ng, Sherry Li, Osni Marques, Tony Drummond, James Demmel, Kathy Yelick: Sparse linear algebra. OSKI/SPARSITY auto-tuners. SuperLU.

Osni Marques, Tony Drummond: The DOE ACTS Collection — a collection of robust and scalable software libraries and toolkits that implement a variety of numerical algorithms, and facilitate code development, tuning and portability.

#### 3.1.8. Algorithms

John Bell, Phil Colella: Adaptive multiscale methods (AMR). Chombo.

Sherry Li, Osni Marques, Juan Meza, Esmond Ng, Ali Pinar, and Chao Yang: High performance algorithms on sparse matrices, combinatorial problems, and optimization.

Andrew Canning, Lin-Wang Wang: Materials science algorithms and applications. PARATEC, PeSCAN (density functional theory). Efficient parallel 3D FFTs.

Julian Borrill and Peter Nugent: Algorithms in the area of cosmology.

Chris Ding, Ali Pinar: Algorithms in data mining, graph theory, and bioinformatics.

#### 3.1.9. Benchmarking, Performance Modeling, and Analysis

Leonid Oliker: Benchmarking and analysis of ultrascale applications on the largest systems in the world. Broad application experience and contacts with many software groups.

David Skinner: Performance analysis tools for parallel applications (IPM and related tools for visualizing performance data).

Costin Iancu: Communications analysis for UPC and global memory languages.

Erich Strohmaier: Benchmarking and performance modeling for large-scale systems. (APEX Map).

David Bailey: NAS Parallel Benchmarks, leader of Performance Engineering Research Center (PERC).

Bill Kramer: The Sustained System Performance (SSP) and Effective System Performance (ESP) Tests.

Greg Butler, Rei Lee, David Skinner, Hongzhang Shan : I/O benchmarks for large scale I/O.

#### 3.1.10. Operating Systems

Paul Hargrove, Jason Duell, Tom Davis: Linux checkpoint/restart. MVIA, FastOS.

#### 3.1.11. Computer Architecture

Kathy Yelick, Leonid Oliker, John Shalf: Collaborations with David Patterson and Krste Asanovic at UC Berkeley and with Christos Kozyrakis at Stanford. Research into opportunities for emerging architectures such as Cell and ViVA. Development of new architectures such as IRAM and VIRAM (processor in memory architecture).

#### 3.1.12. Distributed and Grid Computing

Deb Agarwal, Bill Johnston, Keith Jackson, Steve Chan, Bill Kramer: LBNL is a leader in grid computing and currently is supporting a dozen virtual organizations and grids in production.

#### 3.1.13. Network Research

Deb Agarwal, Bill Johnston, Mary Thompson, Howard Walter, Brent Draney: LBNL is the home of ESnet, an organization that takes a global, end-to-end view of networking requirements. LBNL's history in network research goes back to the early days of the Internet. It currently focuses on understanding network bottlenecks.

#### 3.1.14. CyberSecurity

Vern Paxson, Brent Draney, Scott Campbell, Nick Cardo, Howard Walter, Bill Kramer: Bro is a flexible and proven instruction detection system. NERSC has been a leader in large-scale cyber security, both with its track record, and through conferences, IT system administration practices, tutorials, and improving software.

#### 3.1.15. Computer Science

Strong connections to computer science and computational science disciplines. There include reliable and adaptive distributed systems (Dave Patterson), sensor networks and reconfigurable systems (David Culler), math algorithms (James Demmel), Center for Information Technology Research in the Interest of Society (CITRIS) (James Demmel), storage (John Kubitowiz), theory, security (David Wagner), etc.

# 4. Who Are Other Key Players Who Will Play a Role and Can Help?

## 4.1. Argonne National Laboratory

- Experience in MPI, might be best suited to address the high interconnect latency.

- Experience in operating systems that could be lightweight OS for these systems.

- Large-scale debugging.

- BG/L and fault-tolerant software: Pete Beckman, Susan Coughlan.

## 4.2. Lawrence Livermore National Laboratory

- Experience in MPI, might be best suited to address the high interconnect latency.

- Experience in operating systems that could be lightweight OS for these systems.

- Large-scale debugging.

- Large-scale visualization and data analysis: Hank Childs's VisIT software infrastructure is an important substrate for visualization of massive datasets. Valerio Pascucci's space filling curves and data streaming technology is essential for reorganizing data for efficient analysis and retrieval.

- Large-scale system assessment: Mark Seager has a long track record of identifying the weaknesses in vendor roadmaps and architectural plans for the largest-scale ASC systems. LLNL contributes valuable experience on risk assessment and mitigation for complex systems at all levels of the effort.