# **ExaScale Computing Study:** Technology Challenges in Achieving Exascale Systems

Peter Kogge, Editor & Study Lead Keren Bergman Shekhar Borkar **Dan Campbell** William Carlson William Dally **Monty Denneau Paul Franzon** William Harrod Kerry Hill Jon Hiller Sherman Karp Stephen Keckler Dean Klein Robert Lucas Mark Richards Al Scarpelli **Steven Scott Allan Snavely Thomas Sterling** R. Stanley Williams **Katherine Yelick**

#### **September 28, 2008**

This work was sponsored by DARPA IPTO in the ExaScale Computing Study with Dr. William Harrod as Program Manager; AFRL contract number **FA8650-07-C-7724.** This report is published in the interest of scientific and technical information exchange and its publication does not constitute the Government's approval or disapproval of its ideas or findings

#### **NOTICE**

Using Government drawings, specifications, or other data included in this document for any purpose other than Government procurement does not in any way obligate the U.S. Government. The fact that the Government formulated or supplied the drawings, specifications, or other data does not license the holder or any other person or corporation; or convey any rights or permission to manufacture, use, or sell any patented invention that may relate to them.

APPROVED FOR PUBLIC RELEASE, DISTRIBUTION UNLIMITED.

#### **DISCLAIMER**

The following disclaimer was signed by all members of the Exascale Study Group (listed below):

I agree that the material in this document reflects the collective views, ideas, opinions and findings of the study participants only, and not those of any of the universities, corporations, or other institutions with which they are affiliated. Furthermore, the material in this document does not reflect the official views, ideas, opinions and/or findings of DARPA, the Department of Defense, or of the United States government.

Keren Bergman

Shekhar Borkar

Dan Campbell

William Carlson

William Dally

Monty Denneau

Paul Franzon

William Harrod

Kerry Hill

Jon Hiller

Sherman Karp

Stephen Keckler

Dean Klein

Peter Kogge

Robert Lucas

Mark Richards

Al Scarpelli

Steven Scott

Allan Snavely

Thomas Sterling

R. Stanley Williams

Katherine Yelick

This page intentionally left blank.

#### **FOREWORD**

This document reflects the thoughts of a group of highly talented individuals from universities, industry, and research labs on what might be the challenges in advancing computing by a thousand-fold by 2015. The work was sponsored by DARPA IPTO with Dr. William Harrod as Program Manager, under AFRL contract #FA8650-07-C-7724. The report itself was drawn from the results of a series of meetings over the second half of 2007, and as such reflects a snapshot in time.

The goal of the study was to assay the state of the art, and not to either propose a potential system or prepare and propose a detailed roadmap for its development. Further, the report itself was assembled in just a few months at the beginning of 2008 from input by the participants. As such, all inconsistencies reflect either areas where there really are significant open research questions, or misunderstandings by the editor. There was, however, virtually complete agreement about the key challenges that surfaced from the study, and the potential value that solving them may have towards advancing the field of high performance computing.

I am honored to have been part of this study, and wish to thank the study members for their passion for the subject, and for contributing far more of their precious time than they expected.

Peter M. Kogge, Editor and Study Lead University of Notre Dame May 1, 2008.

This page intentionally left blank.

# Contents

| 1        | Exe | ecutive Overview                                                | 1   |

|----------|-----|-----------------------------------------------------------------|-----|

| <b>2</b> | Def | ining an Exascale System                                        | 5   |

|          | 2.1 | Attributes                                                      | 5   |

|          |     | 2.1.1 Functional Metrics                                        | 5   |

|          |     | 2.1.2 Physical Attributes                                       | 6   |

|          |     | 2.1.3 Balanced Designs                                          | 6   |

|          |     | 2.1.4 Application Performance                                   | 7   |

|          | 2.2 | Classes of Exascale Systems                                     | 8   |

|          |     | 2.2.1 Data Center System                                        | 8   |

|          |     | 2.2.2 Exascale and HPC                                          | 9   |

|          |     | 2.2.3 Departmental Systems                                      | 9   |

|          |     |                                                                 | 10  |

|          |     | 2.2.5 Cross-class Applications                                  | 11  |

|          | 2.3 |                                                                 | 12  |

|          |     |                                                                 | 12  |

|          |     | 2.3.2 Capability Data Center-sized Exa Systems                  | 13  |

|          |     | 2.3.3 Departmental Peta Systems                                 | 14  |

|          |     | 2.3.4 Embedded Tera Systems                                     | 14  |

|          | 2.4 | Prioritizing the Attributes                                     | 14  |

| 0        | ъ.  | 1 1                                                             | 1 🗖 |

| 3        |     | 9                                                               | 17  |

|          | 3.1 |                                                                 | 17  |

|          | 3.2 |                                                                 | 18  |

|          | 3.3 |                                                                 | 19  |

|          | 3.4 |                                                                 | 19  |

|          | 3.5 |                                                                 | 20  |

|          | 3.6 | *                                                               | 20  |

|          | 3.7 |                                                                 | 21  |

|          |     | •                                                               | 21  |

|          |     | 1 1 5                                                           | 21  |

|          |     |                                                                 | 21  |

|          |     |                                                                 | 22  |

|          |     | 3.7.5 2002 HPC for the National Security Community              |     |

|          |     | 3.7.6 2003 Jason Study on Requirements for ASCI                 |     |

|          |     | 3.7.7 2003 Roadmap for the Revitalization of High-End Computing |     |

|          |     | 3.7.8 2004 Getting Up to Speed: The Future of Supercomputing    | 24  |

|   |     | 3.7.9  | 2005 Revitalizing Computer Architecture Research     |

|---|-----|--------|------------------------------------------------------|

|   |     | 3.7.10 | 2006 DSB Task Force on Defense Critical Technologies |

|   |     | 3.7.11 | 2006 The Landscape of Parallel Computing Research    |

|   | ~   |        |                                                      |

| 4 |     | _      | g as We Know It                                      |

|   | 4.1 |        | 's Architectures and Execution Models                |

|   |     | 4.1.1  | Today's Microarchitectural Trends                    |

|   |     |        | 4.1.1.1 Conventional Microprocessors                 |

|   |     |        | 4.1.1.2 Graphics Processors                          |

|   |     |        | 4.1.1.3 Multi-core Microprocessors                   |

|   |     | 4.1.2  | Today's Memory Systems                               |

|   |     | 4.1.3  | Unconventional Architectures                         |

|   |     | 4.1.4  | Data Center/Supercomputing Systems                   |

|   |     |        | 4.1.4.1 Data Center Architectures                    |

|   |     |        | 4.1.4.2 Data Center Power                            |

|   |     |        | 4.1.4.2.1 Mitigation                                 |

|   |     |        | 4.1.4.3 Other Data Center Challenges                 |

|   |     | 4.1.5  | Departmental Systems                                 |

|   |     | 4.1.6  | Embedded Systems                                     |

|   |     | 4.1.7  | Summary of the State of the Art                      |

|   | 4.2 | Today  | 's Operating Environments                            |

|   |     | 4.2.1  | Unix                                                 |

|   |     | 4.2.2  | Windows NT Kernel                                    |

|   |     | 4.2.3  | Microkernels                                         |

|   |     | 4.2.4  | Middleware                                           |

|   |     | 4.2.5  | Summary of the State of the Art                      |

|   | 4.3 | Today  | 's Programming Models                                |

|   |     | 4.3.1  | Automatic Parallelization                            |

|   |     | 4.3.2  | Data Parallel Languages                              |

|   |     | 4.3.3  | Shared Memory                                        |

|   |     | 1.0.0  | 4.3.3.1 OpenMP                                       |

|   |     |        | 4.3.3.2 Threads                                      |

|   |     | 4.3.4  | Message Passing                                      |

|   |     | 4.3.5  | PGAS Languages                                       |

|   |     | 4.3.6  | The HPCS Languages                                   |

|   | 4.4 |        | 's Microprocessors                                   |

|   | 1.1 | 4.4.1  | Basic Technology Parameters                          |

|   |     | 4.4.2  | Overall Chip Parameters                              |

|   |     | 4.4.3  | Summary of the State of the Art                      |

|   | 4.5 |        | 's Top 500 Supercomputers                            |

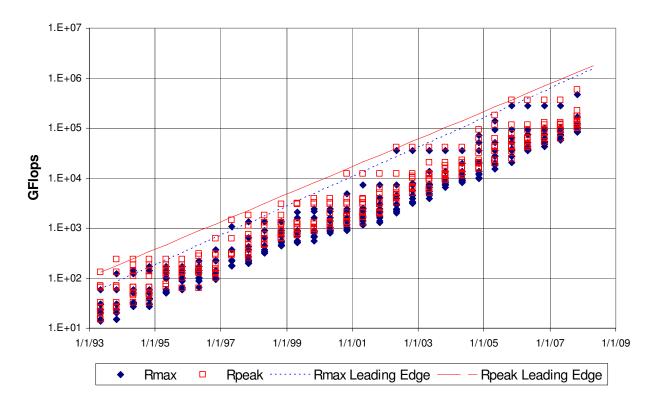

|   | 4.0 | 4.5.1  | Aggregate Performance                                |

|   |     |        |                                                      |

|   |     | 4.5.2  | v .                                                  |

|   |     | 4.5.3  | Performance Components                               |

|   |     |        | 4.5.3.1 Processor Parallelism                        |

|   |     |        | 4.5.3.2 Clock                                        |

|   |     |        | 4.5.3.3 Thread Level Concurrency                     |

|   |     |        | 4.5.3.4 Total Concurrency                            |

|   |     | 454    | Main Memory Capacity                                 |

| 5 | Exa |        | pplication Characteristics 65                                                 | Ĺ |

|---|-----|--------|-------------------------------------------------------------------------------|---|

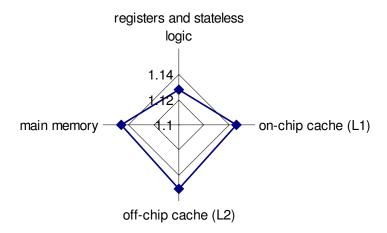

|   | 5.1 | Kiviat | Diagrams                                                                      | l |

|   | 5.2 | Balan  | e and the von Neumann Bottleneck                                              | 2 |

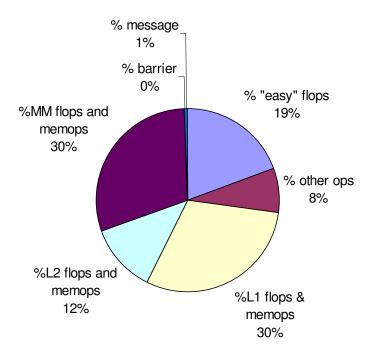

|   | 5.3 | A Typ  | cal Application                                                               | 3 |

|   | 5.4 | Exasca | e Application Characteristics                                                 | 5 |

|   | 5.5 | Memo   | y Intensive Applications of Today                                             | 3 |

|   |     | 5.5.1  | Latency-Sensitive Applications                                                | 3 |

|   |     | 5.5.2  | Locality Sensitive Applications                                               | 3 |

|   |     | 5.5.3  | Communication Costs - Bisection Bandwidth                                     | 9 |

|   | 5.6 | Exasca | e Applications Scaling                                                        | 1 |

|   |     | 5.6.1  | Application Categories                                                        | 1 |

|   |     | 5.6.2  | Memory Requirements                                                           | 2 |

|   |     | 5.6.3  | Increasing Non-Main Memory Storage Capacity                                   | 3 |

|   |     |        | 5.6.3.1 Scratch Storage                                                       |   |

|   |     |        | 5.6.3.2 File Storage                                                          |   |

|   |     |        | 5.6.3.3 Archival Storage                                                      |   |

|   |     | 5.6.4  | Increasing Memory Bandwidth                                                   |   |

|   |     | 5.6.5  | Increasing Bisection Bandwidth                                                |   |

|   |     | 5.6.6  | Increasing Processor Count                                                    |   |

|   | 5.7 |        | ation Concurrency Growth and Scalability                                      |   |

|   | 0.1 | 5.7.1  | Projections Based on Current Implementations                                  |   |

|   |     | 5.7.2  | Projections Based on Theoretical Algorithm Analysis                           |   |

|   |     | 5.7.3  | Scaling to Departmental or Embedded Systems                                   |   |

|   | 5.8 |        | ations Assessments                                                            |   |

|   | 0.0 | 5.8.1  | Summary Observations                                                          |   |

|   |     | 5.8.2  | Implications for Future Research                                              |   |

|   |     | 0.0.2  | implications for ruture research                                              | _ |

| 6 | Tec | hnolog | Roadmaps 88                                                                   | 5 |

|   | 6.1 | Techn  | logical Maturity                                                              | 3 |

|   | 6.2 | Logic  | 'oday                                                                         | 7 |

|   |     | 6.2.1  | ITRS Logic Projections                                                        | 7 |

|   |     |        | 6.2.1.1 Power and Energy                                                      | 3 |

|   |     |        | 6.2.1.2 Area                                                                  | 3 |

|   |     |        | 6.2.1.3 High Performance Devices                                              | 9 |

|   |     |        | 6.2.1.4 Low Operating Voltage Devices                                         | 9 |

|   |     |        | 6.2.1.5 Limitations of Power Density and Its Effect on Operating Frequency 90 | ) |

|   |     | 6.2.2  | Silicon Logic Technology                                                      | 2 |

|   |     |        | 6.2.2.1 Technology Scaling Challenges                                         | 2 |

|   |     |        | 6.2.2.2 Silicon on Insulator                                                  | 3 |

|   |     |        | 6.2.2.3 Supply Voltage Scaling                                                | 1 |

|   |     |        | 6.2.2.4 Interaction with Key Circuits                                         |   |

|   |     | 6.2.3  | Hybrid Logic                                                                  |   |

|   |     | 6.2.4  | Superconducting Logic                                                         |   |

|   |     | 0      | 6.2.4.1 Logic Power and Density Comparison                                    |   |

|   |     |        | 6.2.4.1.1 Cooling Costs                                                       |   |

|   |     |        | 6.2.4.2 The Memory Challenge                                                  |   |

|   |     |        | 6.2.4.3 The Latency Challenge                                                 |   |

|   |     |        | 6.2.4.4 The Cross-Cryo Bandwidth Challenge                                    |   |

|   |     |        | v                                                                             |   |

| 6.3 | Main  | Memory Today                                     | 03 |

|-----|-------|--------------------------------------------------|----|

|     | 6.3.1 | The Memory/Storage Hierarchy                     | 03 |

|     | 6.3.2 | Memory Types                                     | 04 |

|     |       | 6.3.2.1 SRAM Attributes                          |    |

|     |       | 6.3.2.2 DRAM Attributes and Operation            |    |

|     |       | 6.3.2.3 NAND Attributes and Operation            |    |

|     |       | 6.3.2.4 Alternative Memory Types                 |    |

|     |       | 6.3.2.4.1 Phase Change Memory                    |    |

|     |       | 6.3.2.4.2 SONOS Memory                           |    |

|     |       | 6.3.2.4.3 MRAM                                   |    |

|     | 6.3.3 | Main Memory Reliability - Good News              |    |

|     |       | 6.3.3.1 Trends in FIT Rates                      |    |

|     |       | 6.3.3.2 Immunity to SER                          |    |

|     |       | 6.3.3.3 Possible Issue: Variable Retention Time  |    |

|     |       | 6.3.3.3.1 Causes                                 |    |

|     |       | 6.3.3.3.2 Effects                                |    |

|     |       | 6.3.3.3 Mitigation                               |    |

|     | 6.3.4 | The Main Memory Scaling Challenges               |    |

|     | 0.0.1 | 6.3.4.1 The Performance Challenge                |    |

|     |       | 6.3.4.1.1 Bandwidth and Latency                  |    |

|     |       | 6.3.4.1.2 Tradeoffs                              |    |

|     |       | 6.3.4.1.3 Per-pin Limitations                    |    |

|     |       | 6.3.4.2 The Packaging Challenge                  |    |

|     |       | 6.3.4.3 The Power Challenge                      |    |

|     |       | 6.3.4.3.1 Module Power Efficiency                |    |

|     |       | 6.3.4.3.2 Cell Power                             |    |

|     |       | 6.3.4.4 Major Elements of DRAM Power Consumption |    |

|     |       | 6.3.4.4.1 DRAM Operating Modes                   |    |

|     |       | 6.3.4.4.2 DRAM Architecture                      |    |

|     |       | 6.3.4.4.3 Power Consumption Calculations         |    |

|     | 6.3.5 | Emerging Memory Technology                       |    |

| 6.4 | 0.0.0 | e Memory Today                                   |    |

| 0.4 | 6.4.1 | Disk Technology                                  |    |

|     | 0.4.1 | 6.4.1.1 Capacity                                 |    |

|     |       | 6.4.1.2 Power                                    |    |

|     |       | 6.4.1.3 Transfer Rate and Seek Time              |    |

|     |       |                                                  |    |

|     |       | v                                                |    |

|     | 6 4 9 | 6.4.1.5 Cost                                     |    |

|     | 6.4.2 | Holographic Memory Technology                    |    |

| e r | 6.4.3 | Archival Storage Technology                      |    |

| 6.5 |       | onnect Technologies                              |    |

|     | 6.5.1 | Strawman Interconnect                            |    |

|     |       | 6.5.1.1 Local Core-level On-chip Interconnect    |    |

|     |       | 6.5.1.2 Switched Long-range On-chip Interconnect |    |

|     |       | 6.5.1.3 Supporting DRAM and CPU Bandwidth        |    |

|     |       | 6.5.1.4 Intramodule Bandwidth                    |    |

|     |       | 6.5.1.5 Intermodule Bandwidth                    |    |

|     |       | 6.5.1.6 Rack to Rack Bandwidth                   | 29 |

|   |      | 6.5.2           | Signaling on Wire                             | 0   |

|---|------|-----------------|-----------------------------------------------|-----|

|   |      |                 | 6.5.2.1 Point-to-Point Links                  | 60  |

|   |      |                 | 6.5.2.1.1 On-Chip Wired Interconnect          | 60  |

|   |      |                 | 6.5.2.1.2 Off-chip Wired Interconnect         | 60  |

|   |      |                 | 6.5.2.1.3 Direct Chip-Chip Interconnect       |     |

|   |      |                 | 6.5.2.2 Switches and Routers                  |     |

|   |      | 6.5.3           | Optical Interconnects                         |     |

|   |      | 0.0.0           | 6.5.3.1 Optical Point to Point Communications |     |

|   |      |                 | 6.5.3.2 Optical Routed Communications         |     |

|   |      | 6.5.4           | Other Interconnect                            |     |

|   |      | 6.5.5           | Implications                                  |     |

|   | 6.6  |                 | ging and Cooling                              |     |

|   | 0.0  | 6.6.1           | Packaging                                     |     |

|   |      | 0.0.1           | 6.6.1.1 Level 1 Packaging                     |     |

|   |      |                 | 6.6.1.2 Level 2 Packaging                     |     |

|   |      | 669             | 5 6                                           |     |

|   |      | 6.6.2           | Cooling                                       |     |

|   |      |                 | 6.6.2.1 Module Level Cooling                  |     |

|   | 0.7  | <b>C</b>        | 6.6.2.2 Cooling at Higher Levels              |     |

|   | 6.7  | -               | n Resiliency                                  |     |

|   |      | 6.7.1           | Resiliency in Large Scale Systems             |     |

|   |      | 6.7.2           | Device Resiliency Scaling                     |     |

|   |      | 6.7.3           | Resiliency Techniques                         |     |

|   | 0.0  | 6.7.4           | Checkpoint/Rollback                           |     |

|   | 6.8  |                 | cion of Operating Environments                |     |

|   | 6.9  | _               | amming Models and Languages                   |     |

|   |      | 6.9.1           | The Evolution of Languages and Models         |     |

|   |      | 6.9.2           | Road map                                      | 12  |

| 7 | Stra | wmen            | : Where Evolution Is and Is Not Enough 15     | 3   |

|   | 7.1  | Subsys          | stem Projections                              | 3   |

|   |      | $7.1.1^{\circ}$ | Measurement Units                             |     |

|   |      | 7.1.2           | FPU Power Alone                               |     |

|   |      | 7.1.3           | Core Energy                                   |     |

|   |      | 7.1.4           | Main Memory from DRAM                         |     |

|   |      |                 | 7.1.4.1 Number of Chips                       |     |

|   |      |                 | 7.1.4.2 Off-chip Bandwidth                    |     |

|   |      |                 | 7.1.4.3 On-chip Concurrency                   |     |

|   |      | 7.1.5           | Packaging and Cooling                         |     |

|   |      | 7.1.6           | Non-Main Memory Storage                       |     |

|   |      | 7.1.7           | Summary Observations                          |     |

|   | 7.2  |                 | ionary Data Center Class Strawmen             |     |

|   | ,    | 7.2.1           | Heavy Node Strawmen                           |     |

|   |      |                 | 7.2.1.1 A Baseline                            |     |

|   |      |                 | 7.2.1.2 Scaling Assumptions                   |     |

|   |      |                 | 7.2.1.3 Power Models                          |     |

|   |      |                 | 7.2.1.4 Projections                           |     |

|   |      |                 |                                               | _   |

|   |      | 7.2.2           | Light Node Strawmen                           | "() |

|   |     |           | 7.2.2.2 Scaling Assumptions                                   |

|---|-----|-----------|---------------------------------------------------------------|

|   |     |           | 7.2.2.3 Power Models                                          |

|   |     |           | 7.2.2.4 Projections                                           |

|   | 7.3 | Aggres    | ssive Silicon System Strawman                                 |

|   |     | 7.3.1     | FPUs                                                          |

|   |     | 7.3.2     | Single Processor Core                                         |

|   |     | 7.3.3     | On-Chip Accesses                                              |

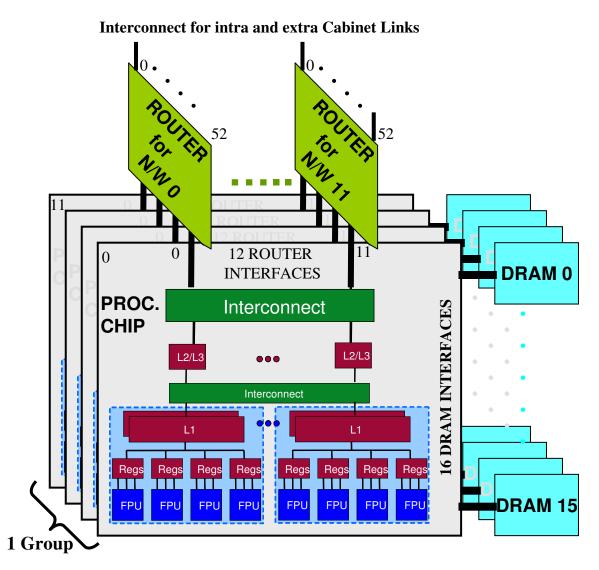

|   |     | 7.3.4     | Processing Node                                               |

|   |     | 7.3.5     | Rack and System                                               |

|   |     |           | 7.3.5.1 System Interconnect Topology                          |

|   |     |           | 7.3.5.2 Router Chips                                          |

|   |     |           | 7.3.5.3 Packaging within a rack                               |

|   |     | 7.3.6     | Secondary Storage                                             |

|   |     | 7.3.7     | An Adaptively Balanced Node                                   |

|   |     | 7.3.8     | Overall Analysis                                              |

|   |     | 7.3.9     | Other Considerations                                          |

|   |     | 7.3.10    | Summary and Translation to Other Exascale System Classes 187  |

|   |     |           | 7.3.10.1 Summary: Embedded                                    |

|   |     |           | 7.3.10.2 Summary: Departmental                                |

|   |     |           | 7.3.10.3 Summary: Data Center                                 |

|   | 7.4 |           | ale Resiliency                                                |

|   | 7.5 | Optica    | al Interconnection Networks for Exascale Systems              |

|   |     | 7.5.1     | On-Chip Optical Interconnect                                  |

|   |     | 7.5.2     | Off-chip Optical Interconnect                                 |

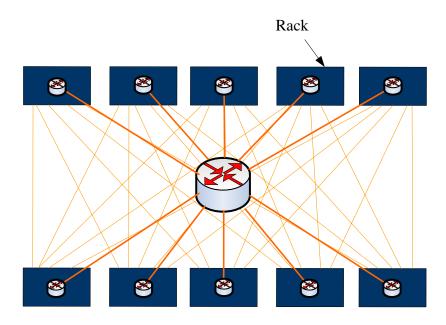

|   |     | 7.5.3     | Rack to Rack Optical Interconnect                             |

|   |     | 7.5.4     | Alternative Optically-connected Memory and Storage System 196 |

|   | 7.6 |           | ssive Operating Environments                                  |

|   |     | 7.6.1     | Summary of Requirements                                       |

|   |     | 7.6.2     | Phase Change in Operating Environments                        |

|   |     | 7.6.3     | An Aggressive Strategy                                        |

|   |     | 7.6.4     | Open Questions                                                |

|   | 7.7 | _         | amming Model                                                  |

|   | 7.8 |           | ale Applications                                              |

|   |     | 7.8.1     | WRF                                                           |

|   |     | 7.8.2     | AVUS                                                          |

|   |     | 7.8.3     | HPL                                                           |

|   | 7.9 | Strawı    | man Assessments                                               |

| 8 | Exa | scale (   | Challenges and Key Research Areas 207                         |

| Ü | 8.1 |           | Challenges                                                    |

|   | 0.1 | 8.1.1     | The Energy and Power Challenge                                |

|   |     | 0.1.1     | 8.1.1.1 Functional Power                                      |

|   |     |           | 8.1.1.2 DRAM Main Memory Power                                |

|   |     |           | 8.1.1.3 Interconnect Power                                    |

|   |     |           | 8.1.1.4 Secondary Storage Power                               |

|   |     | 8.1.2     | The Memory and Storage Challenge                              |

|   |     | ~ <b></b> | 8.1.2.1 Main Memory                                           |

|   |     |           | 8.1.2.2 Secondary Storage                                     |

|   |     |           |                                                               |

|              |      | 8.1.3   | The Concurrency and Locality Challenge                                   |     |

|--------------|------|---------|--------------------------------------------------------------------------|-----|

|              |      |         | 8.1.3.1 Extraordinary Concurrency as the Only Game in Town               | 214 |

|              |      |         | 8.1.3.2 Applications Aren't Going in the Same Direction                  | 216 |

|              |      | 8.1.4   | The Resiliency Challenge                                                 | 217 |

|              | 8.2  | Resear  | ch Thrust Areas                                                          | 218 |

|              |      | 8.2.1   | Thrust Area: Exascale Hardware Technologies and Architecture             | 219 |

|              |      |         | 8.2.1.1 Energy-efficient Circuits and Architecture In Silicon            | 220 |

|              |      |         | 8.2.1.2 Alternative Low-energy Devices and Circuits for Logic and Memory | 222 |

|              |      |         | 8.2.1.3 Alternative Low-energy Systems for Memory and Storage            |     |

|              |      |         | 8.2.1.4 3D Interconnect, Packaging, and Cooling                          |     |

|              |      |         | 8.2.1.5 Photonic Interconnect Research Opportunities and Goals           |     |

|              |      | 8.2.2   | Thrust Area: Exascale Architectures and Programming Models               | 225 |

|              |      |         | 8.2.2.1 Systems Architectures and Programming Models to Reduce Com-      |     |

|              |      |         | munication                                                               |     |

|              |      |         | 8.2.2.2 Locality-aware Architectures                                     |     |

|              |      | 8.2.3   | Thrust Area: Exascale Algorithm and Application Development              |     |

|              |      |         | 8.2.3.1 Power and Resiliency Models in Application Models                |     |

|              |      |         | 8.2.3.2 Understanding and Adapting Old Algorithms                        |     |

|              |      |         | 8.2.3.3 Inventing New Algorithms                                         |     |

|              |      |         | 8.2.3.4 Inventing New Applications                                       |     |

|              |      | 0.0.4   | 8.2.3.5 Making Applications Resiliency-Aware                             |     |

|              |      | 8.2.4   | Thrust Area: Resilient Exascale Systems                                  |     |

|              |      |         | 8.2.4.1 Energy-efficient Error Detection and Correction Architectures    |     |

|              |      |         | 8.2.4.2 Fail-in-place and Self-Healing Systems                           |     |

|              |      |         | 8.2.4.3 Checkpoint Rollback and Recovery                                 |     |

|              |      |         | 8.2.4.4 Algorithmic-level Fault Checking and Fault Resiliency            |     |

|              | 0.9  | 1 / L . | 8.2.4.5 Vertically-Integrated Resilient Systems                          |     |

|              | 8.3  | _       | phase Technology Development                                             |     |

|              |      | 8.3.1   | Phase 1: Systems Architecture Explorations                               |     |

|              |      | 8.3.2   | Phase 2: Technology Demonstrators                                        |     |

|              |      | 8.3.3   | Phase 3: Scalability Slice Prototype                                     | 232 |

| A            | Exa  | scale S | tudy Group Members                                                       | 235 |

|              |      |         |                                                                          | 235 |

|              |      |         | phies                                                                    |     |

|              |      | J       | •                                                                        |     |

| В            |      |         | 1 0 0                                                                    | 245 |

|              | B.1  |         | g #1: Study Kickoff                                                      |     |

|              | B.2  |         | ng #2: Roadmaps and Nanotechnology                                       |     |

|              | B.3  | _       | l Topics Meeting #1: Packaging                                           |     |

|              | B.4  |         | ng #3: Logic                                                             |     |

|              | B.5  |         | ng #4: Memory Roadmap and Issues                                         |     |

|              | B.6  | -       | Topics Meeting #2: Architectures and Programming Environments            |     |

|              | B.7  | _       | l Topics Meeting #3: Applications, Storage, and I/O                      |     |

|              | B.8  | _       | Topics Meeting #4: Optical Interconnects                                 |     |

|              | B.9  | Meetin  | g #5: Report Conclusions and Finalization Plans                          | 251 |

| $\mathbf{C}$ | Glos | ssarv a | nd Abbreviations                                                         | 253 |

# List of Figures

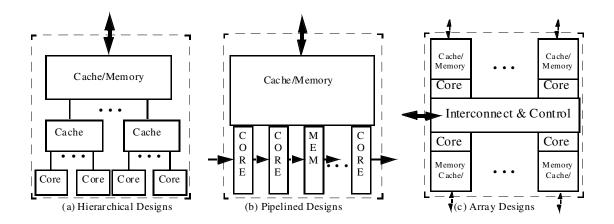

| 4.1  | Three classes of multi-core die microarchitectures                |

|------|-------------------------------------------------------------------|

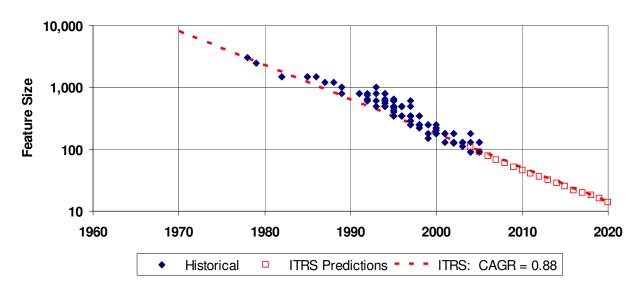

| 4.2  | Microprocessor feature size                                       |

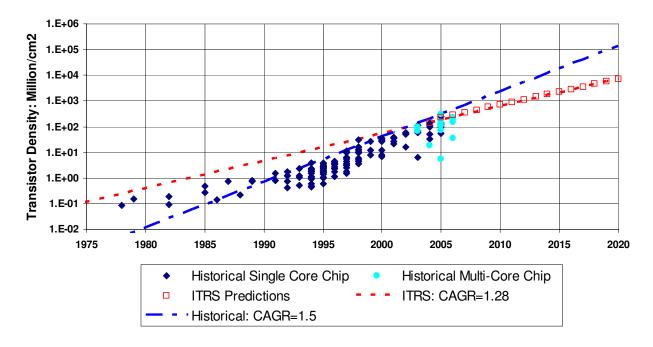

| 4.3  | Microprocessor transistor density                                 |

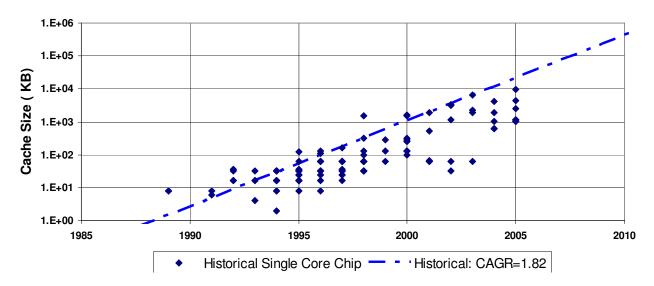

| 4.4  | Microprocessor cache capacity                                     |

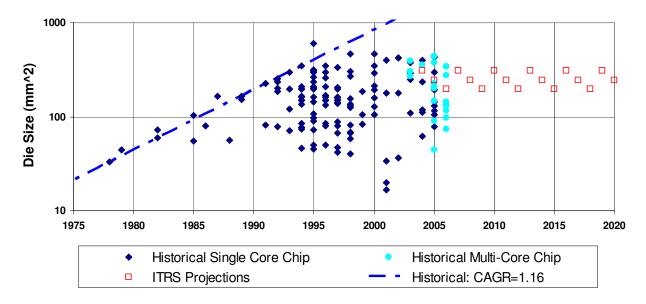

| 4.5  | Microprocessor die size                                           |

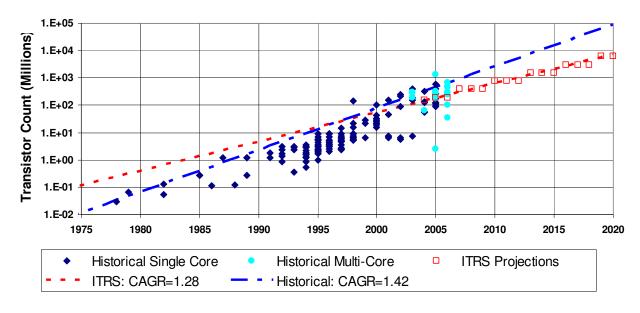

| 4.6  | Microprocessor transistor count                                   |

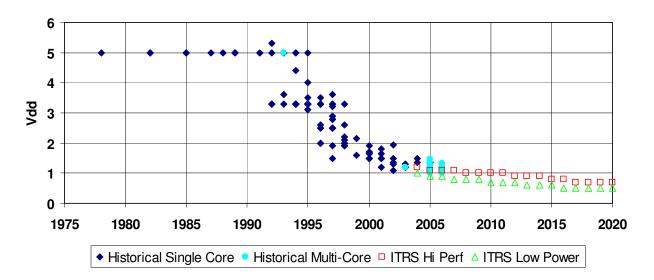

| 4.7  | Microprocessor $V_{dd}$                                           |

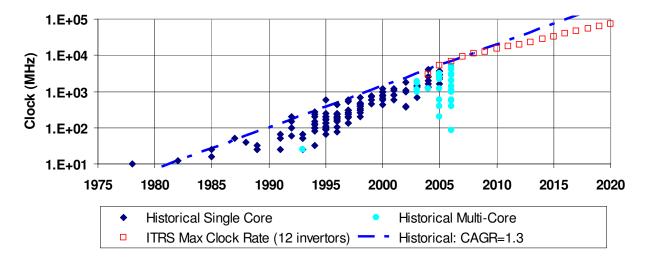

| 4.8  | Microprocessor clock                                              |

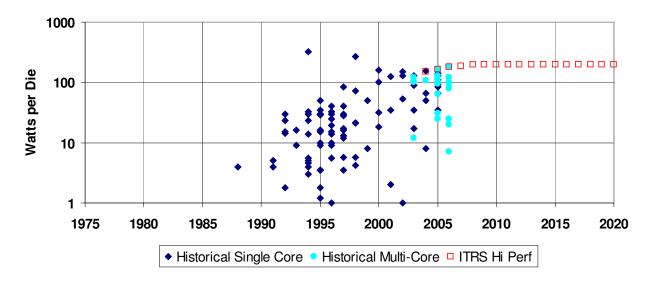

| 4.9  | Microprocessor chip power                                         |

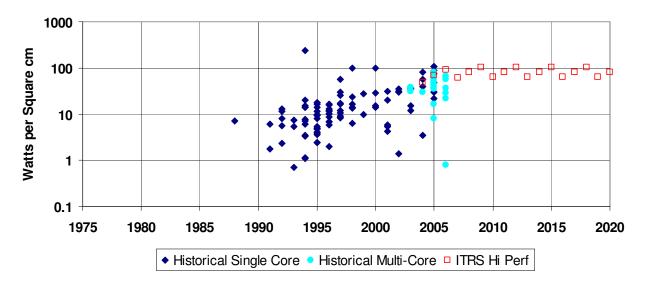

| 4.10 | Microprocessor chip power density                                 |

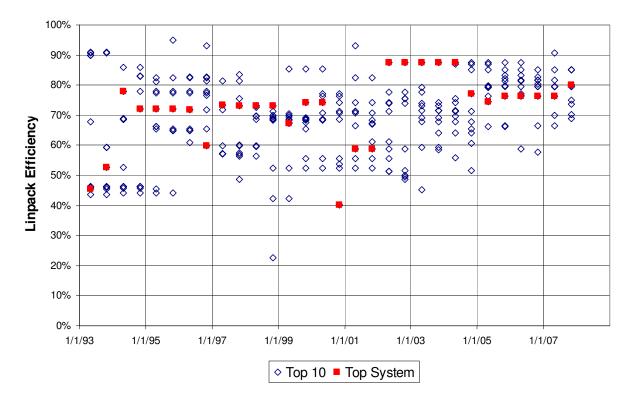

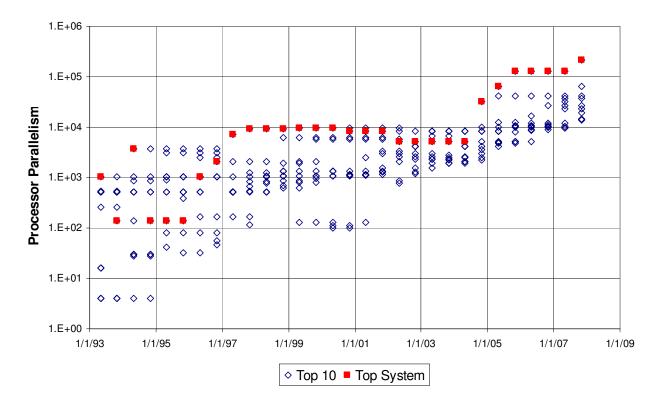

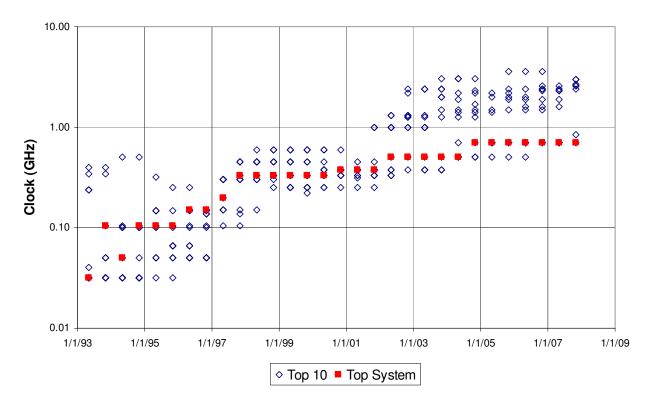

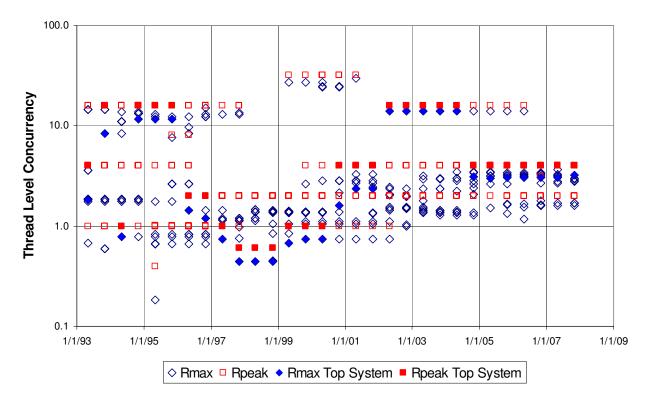

| 4.11 | Performance metrics for the Top 10 supercomputers over time       |

| 4.12 | Efficiency for the Top 10 supercomputers while running Linpack 54 |

| 4.13 | Processor parallelism in the Top 10 supercomputers                |

| 4.14 | Clock rate in the Top 10 supercomputers                           |

| 4.15 | Thread level concurrency in the Top 10 supercomputers             |

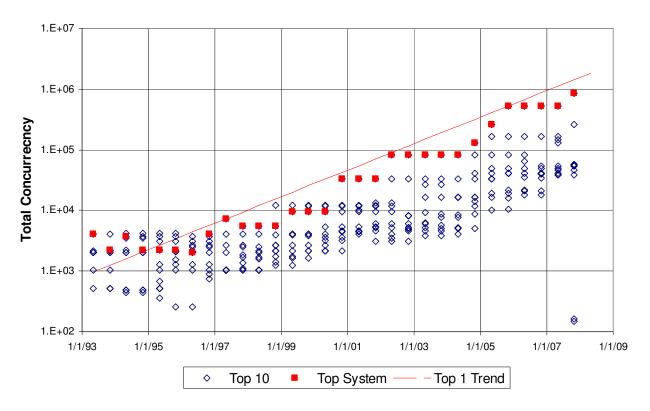

| 4.16 | Total hardware concurrency in the Top 10 supercomputers           |

| 4.17 | Memory capacity in the Top 10 supercomputers                      |

| 5.1  | Predicted speedup of WRF "Large"                                  |

| 5.2  | Time breakdown of WRF by operation category                       |

| 5.3  | Application functionalities                                       |

| 5.4  | Predicted speedup of AVUS to latency halving                      |

| 5.5  | Predicted speedup of WRF to latency halving 6                     |

| 5.6  | Predicted speedup of AMR to latency halving 6                     |

| 5.7  | Predicted speedup of Hycom to latency halving                     |

| 5.8  | Spatial and temporal locality of strategic applications           |

| 5.9  | Performance strategic applications as a function of locality      |

| 5.10 | Growth of communications overhead                                 |

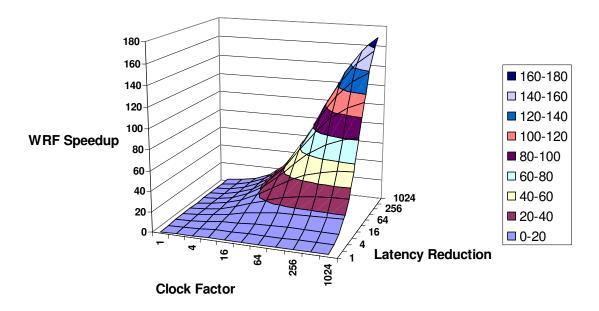

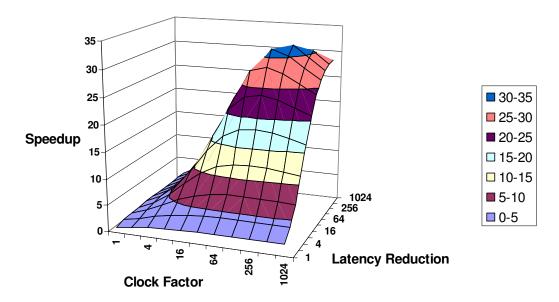

| 5.11 | WRF performance response                                          |

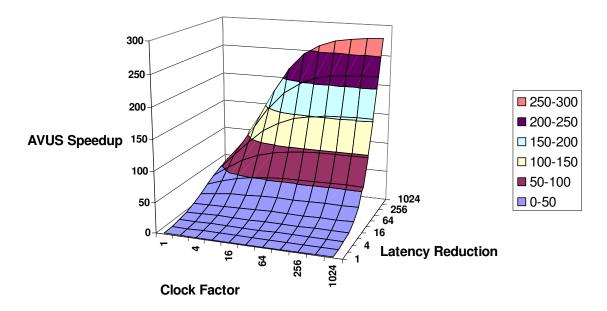

|      | AVUS performance response                                         |

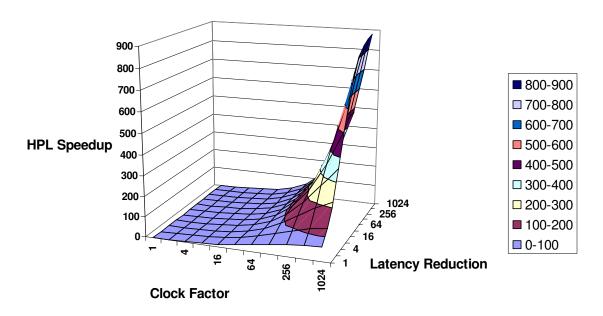

|      | HPL performance response                                          |

| 5.14 | WRF with log(n) communications growth                             |

| 5.15 | AVUS with log(n) communications growth                            |

|      | Future scaling trends                                             |

| 6.1  | ITRS roadmap logic device projections                             |

| 6.2  | Relative change in key power parameters                           |

| 6.3  | Power-constrained clock rate                                      |

| -    |                                                                   |

| 6.4  | Technology outlook                                                                   | 92  |

|------|--------------------------------------------------------------------------------------|-----|

| 6.5  | Simple transport model                                                               | 93  |

| 6.6  | Transistor sub-threshold leakage current and leakage power in recent microprocessors | 93  |

| 6.7  | Technology outlook and estimates                                                     | 94  |

| 6.8  | Frequency and power scaling with supply voltage                                      | 95  |

| 6.9  | Sensitivities to changing $V_{dd}$                                                   |     |

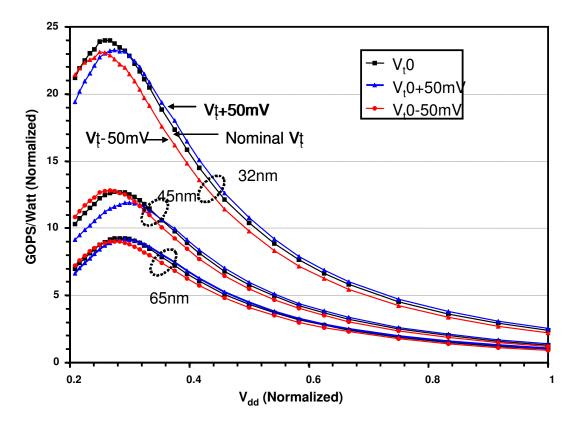

| 6.10 | Technology scaling, $V_t$ variations, and energy efficiency                          | 97  |

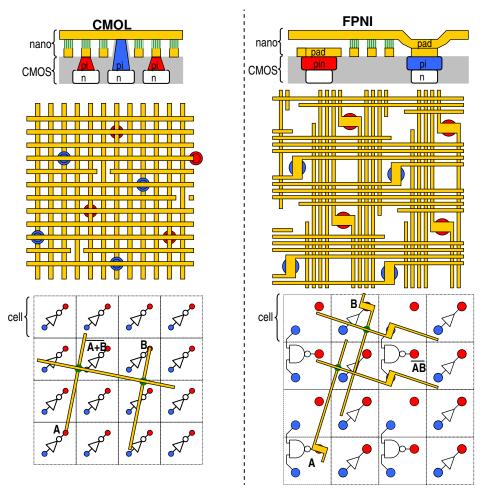

| 6.11 | Hybrid logic circuits                                                                |     |

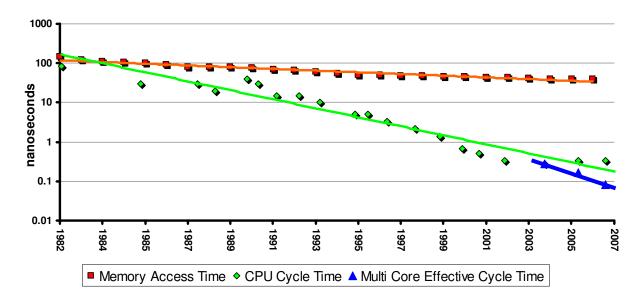

| 6.12 | CPU and memory cycle time trends                                                     | 103 |

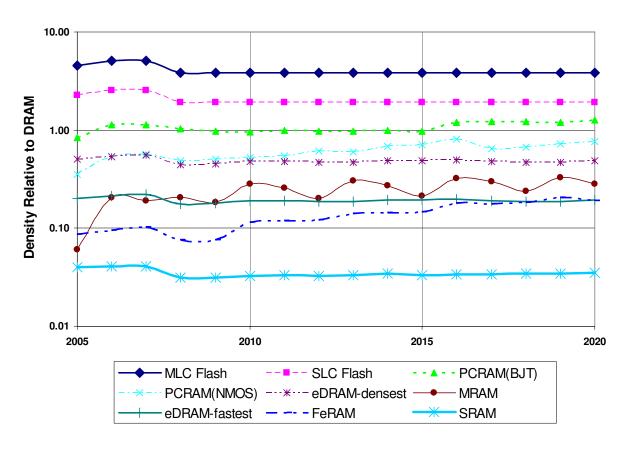

|      | ITRS roadmap memory density projections                                              |     |

| 6.14 | DRAM cross section                                                                   | 106 |

|      | Programmed and un-programmed NAND cells                                              |     |

|      | DRAM retention time distribution                                                     |     |

| 6.17 | Memory module RMA results                                                            | 110 |

|      | Variable retention time as it affects refresh distribution                           |     |

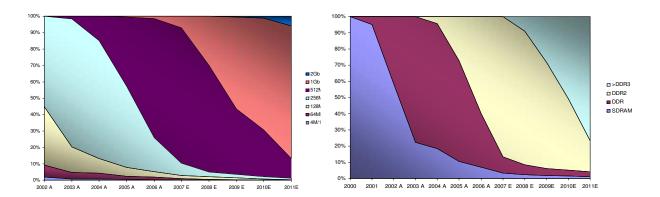

|      | Industry memory projections                                                          |     |

|      | Reduced latency DRAM                                                                 |     |

|      | Center-bonded DRAM package                                                           |     |

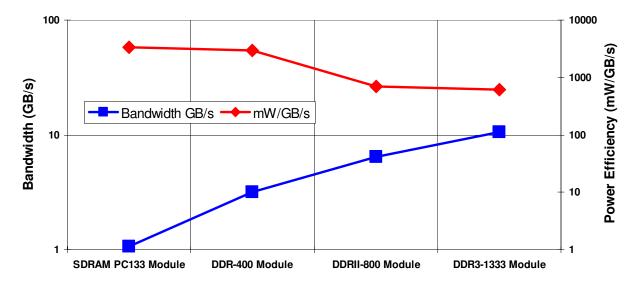

|      | Commodity DRAM module power efficiency as a function of bandwidth                    |     |

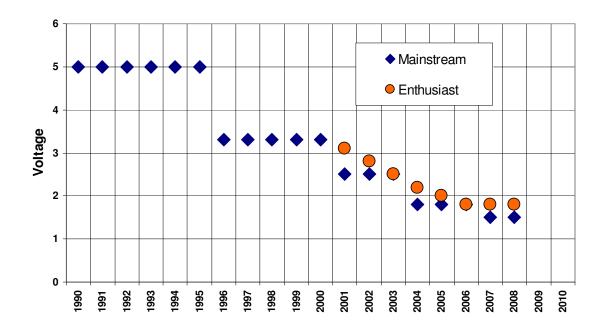

|      | Commodity DRAM voltage scaling.                                                      |     |

|      | Block diagram of 1Gbit, X8 DDR2 device                                               |     |

|      | DDR3 current breakdown for Idle, Active, Read and Write                              |     |

|      | Nanoscale memory addressing.                                                         |     |

|      | Nanoscale memory via imprint lithography                                             |     |

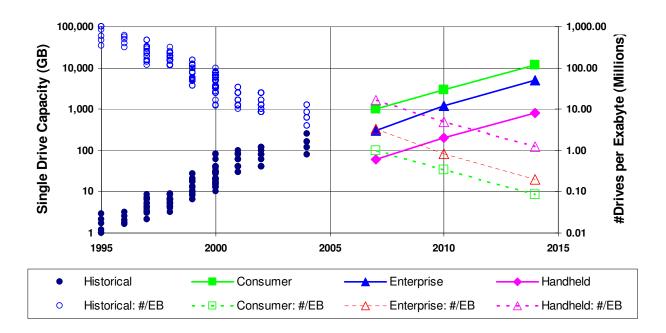

|      | Disk capacity properties                                                             |     |

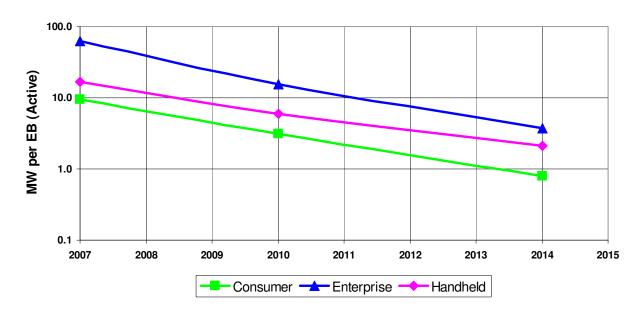

|      | Disk power per Exabyte                                                               |     |

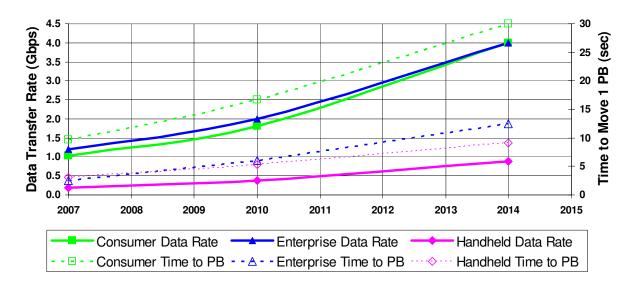

|      | Disk transfer rate properties                                                        |     |

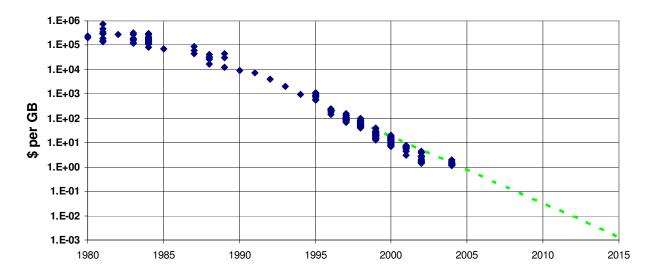

|      | Disk price per GB                                                                    |     |

|      | Interconnect bandwidth requirements for an Exascale system                           |     |

|      | Comparison of 3D chip stacking communications schemes                                |     |

|      | Entire optical communication path                                                    |     |

|      | Modulator approach to integrated optics                                              |     |

|      | Representative current and future high-end level 1 packaging                         |     |

|      | Estimated chip counts in recent HPC systems                                          |     |

|      | Scaling trends for environmental factors that affect resiliency                      |     |

|      | Increase in vulnerability as a function of per-socket failure rates                  |     |

|      | Projected application utilization when accounting for checkpoint overheads           |     |

| 00   |                                                                                      |     |

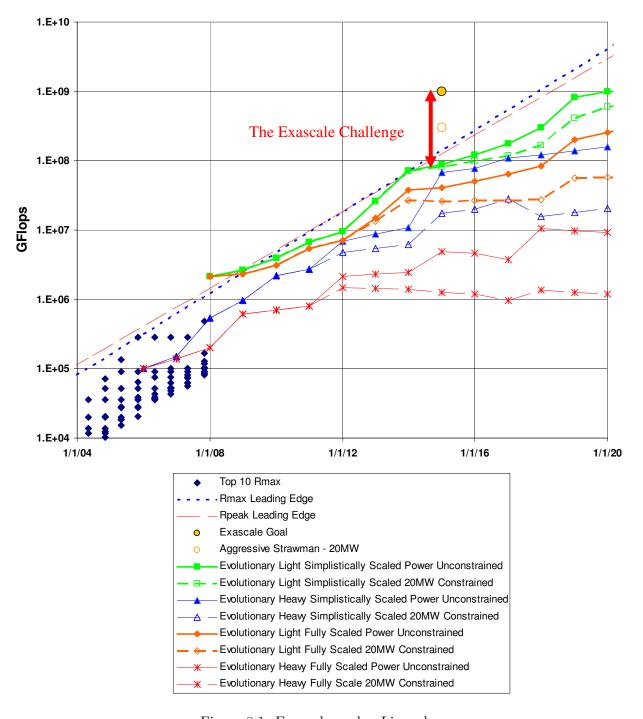

| 7.1  | Projections to reach an Exaflop per second                                           | 154 |

| 7.2  | Energy per cycle for several cores                                                   | 155 |

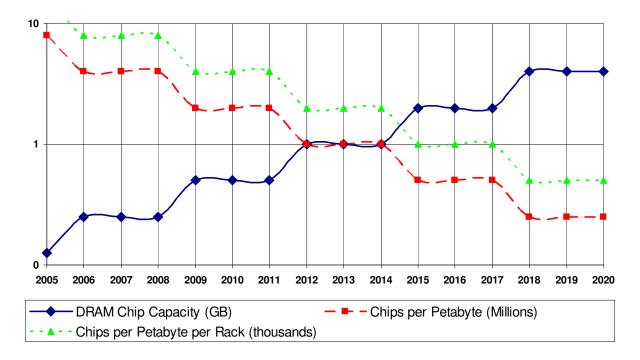

| 7.3  | DRAM as main memory for data center class systems                                    | 156 |

| 7.4  | Memory access rates in DRAM main memory                                              | 158 |

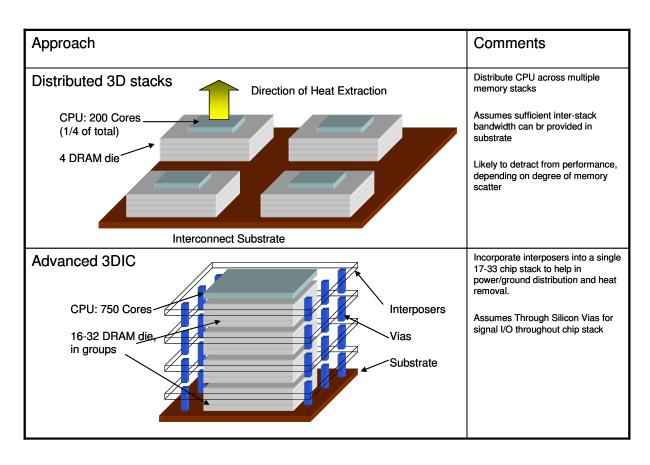

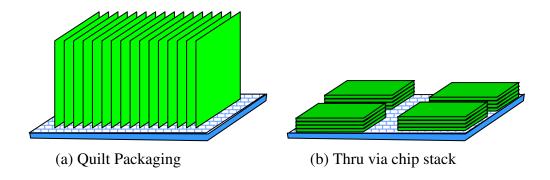

| 7.5  | Potential directions for 3D packaging (A)                                            | 160 |

| 7.6  | Potential directions for 3D packaging (B)                                            | 161 |

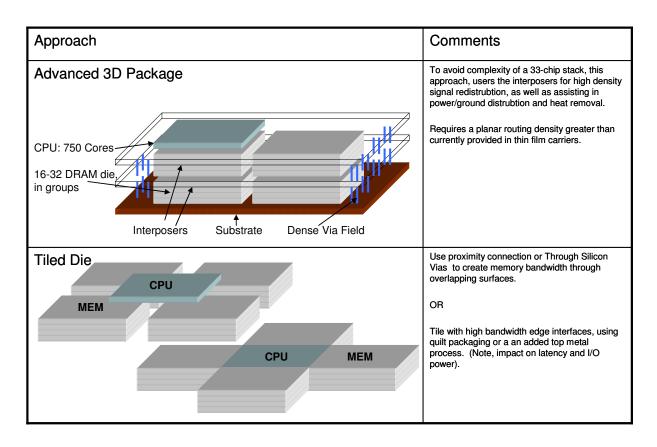

| 7.7  | Potential directions for 3D packaging (C)                                            | 161 |

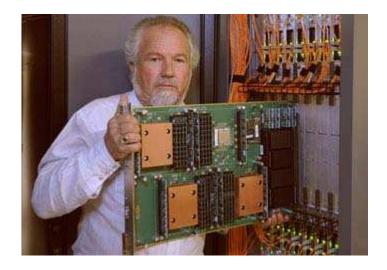

| 7.8  | A typical heavy node reference board                                                 | 164 |

| 7.9  | Characteristics of a typical board today                                             | 165 |

| 7.10 | Heavy node strawman projections                                                      | 167 |

| 7.11 | Heavy node performance projections                         |

|------|------------------------------------------------------------|

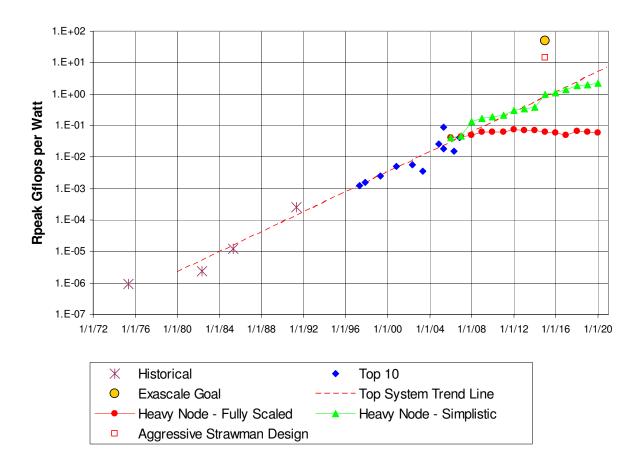

| 7.12 | Heavy node GFlops per Watt                                 |

| 7.13 | Power distribution in the light node strawman              |

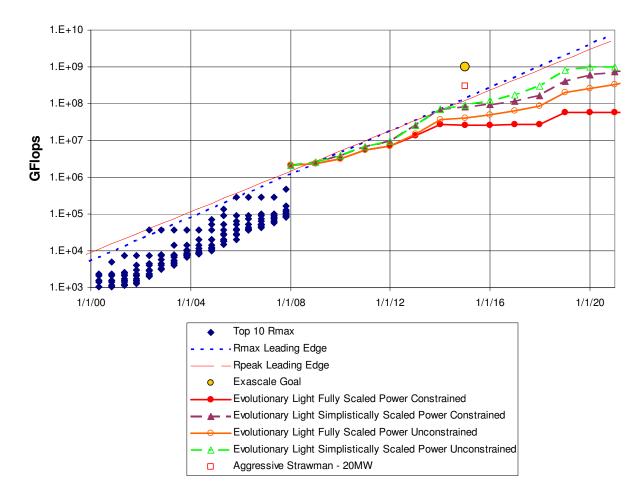

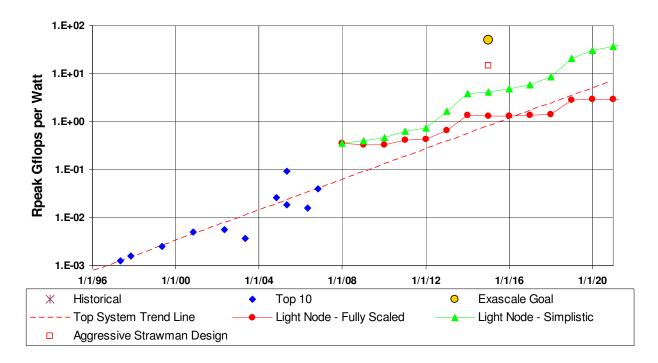

| 7.14 | Light node strawman performance projections                |

| 7.15 | Light node strawman Gflops per watt                        |

| 7.16 | Aggressive strawman architecture                           |

| 7.17 | Possible aggressive strawman packaging of a single node    |

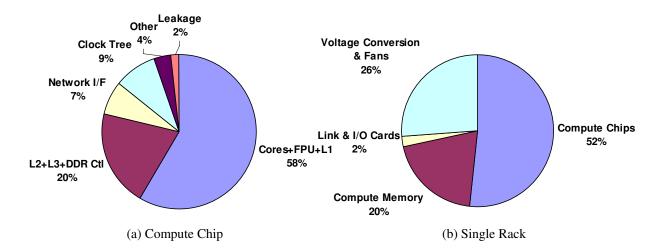

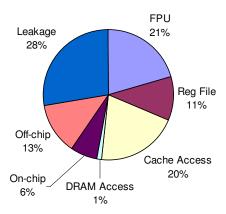

| 7.18 | Power distribution within a node                           |

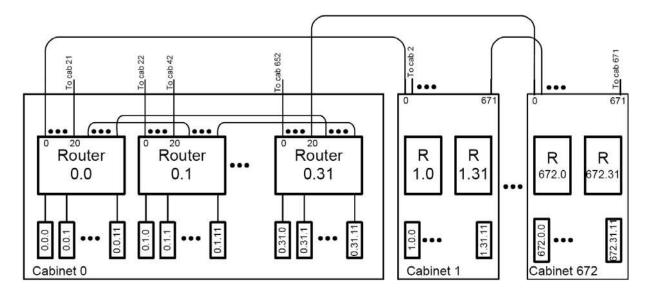

| 7.19 | The top level of a dragonfly system interconnect           |

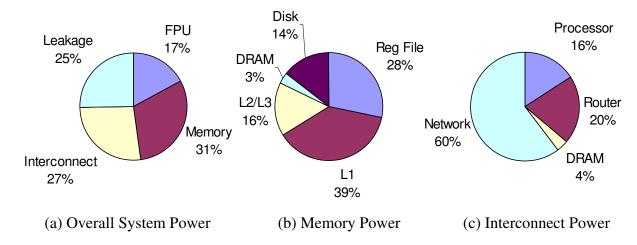

| 7.20 | Power distribution in aggressive strawman system           |

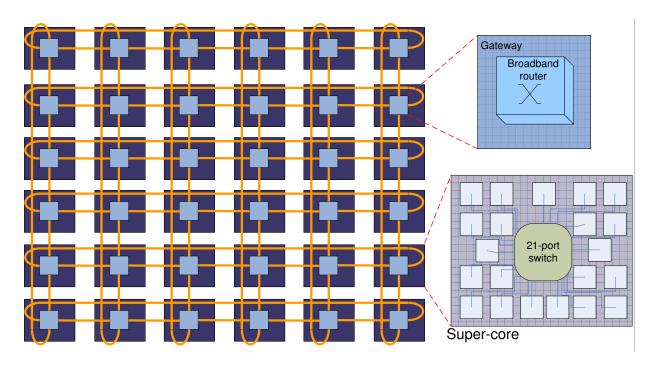

| 7.21 | Chip super-core organization and photonic interconnect     |

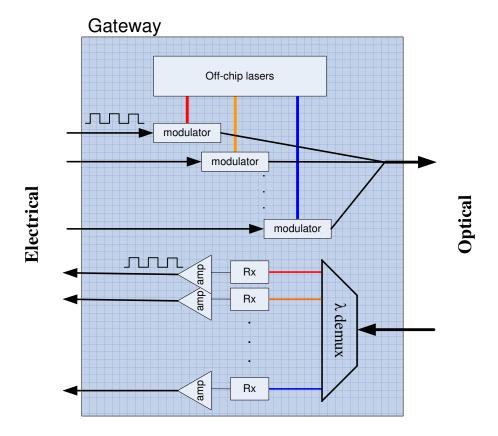

| 7.22 | Gateway functional block design                            |

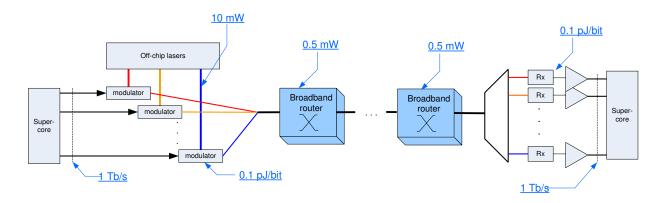

| 7.23 | Super-core to super-core optical on-chip link              |

| 7.24 | Optical system interconnect                                |

| 7.25 | A possible optically connected memory stack                |

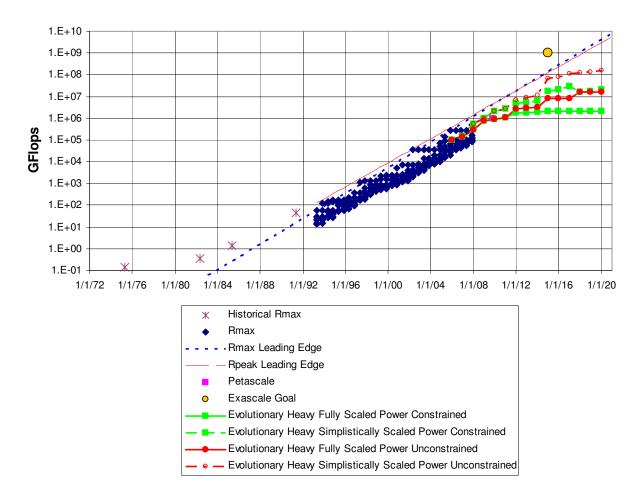

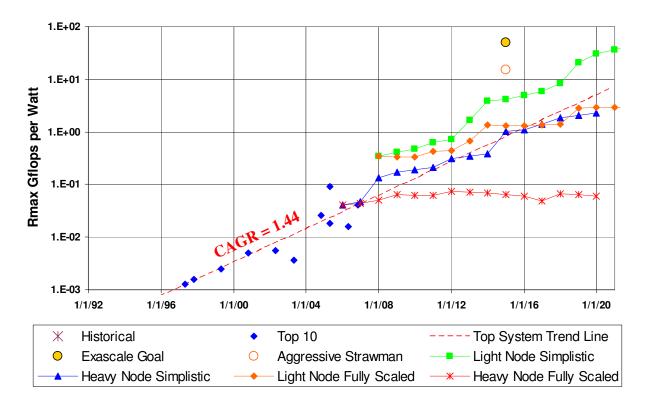

| 8.1  | Exascale goals - Linpack                                   |

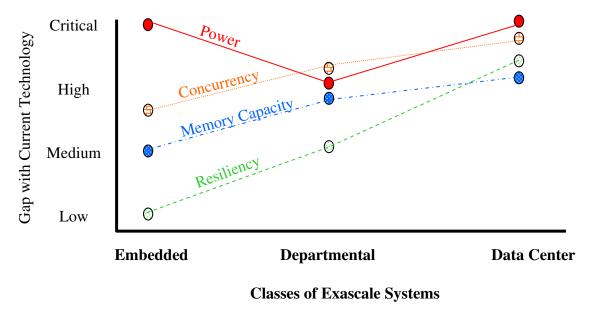

| 8.2  | Critically of each challenge to each Exascale system class |

| 8.3  | The power challenge for an Exaflops Linpack                |

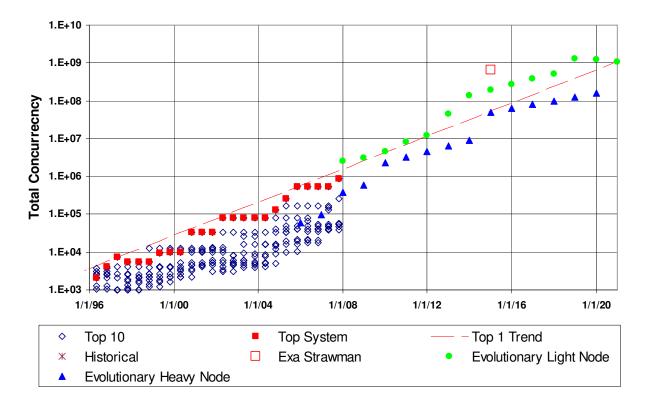

| 8.4  | The overall concurrency challenge                          |

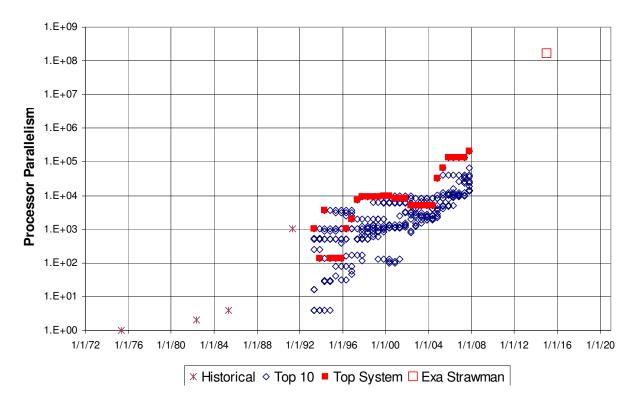

| 8.5  | The processor parallelism challenge                        |

| 8.6  | Future scaling trends present DARPA-hard challenges        |

| 8.7  | Sensitivities to changing $V_{dd}$                         |

# List of Tables

| 2.1  | Attributes of Exascale class systems                                                    |

|------|-----------------------------------------------------------------------------------------|

| 2.2  | Attributes of Exascale class systems                                                    |

| 4.1  | Power distribution losses in a typical data center                                      |

| 5.1  | Summary applications characteristics                                                    |

| 6.1  | Some performance comparisons with silicon                                               |

| 6.2  | 2005 projection of potential RSFQ logic roadmap                                         |

| 6.3  | Area comparisons of various memory technologies                                         |

| 6.4  | Memory types and characteristics                                                        |

| 6.5  | Commodity DRAM operating current                                                        |

| 6.6  | Projected disk characteristics                                                          |

| 6.7  | Energy budget for optical modulator                                                     |

| 6.8  | Summary interconnect technology roadmap                                                 |

| 6.9  | Internal heat removal approaches                                                        |

| 6.10 | External cooling mechanisms                                                             |

| 6.11 | Root causes of failures in Terascale systems                                            |

| 6.12 | BlueGene FIT budget                                                                     |

| 7.1  | Non-memory storage projections for Exascale systems                                     |

| 7.2  | Light node baseline based on Blue Gene                                                  |

| 7.3  | Summary characteristics of aggressively designed strawman architecture 176              |

| 7.4  | Expected area, power, and performance of FPUs with technology scaling 176               |

| 7.5  | Expected area, power, and performance of FPUs with more aggressive voltage scaling. 178 |

| 7.6  | Energy breakdown for a four FPU processor core                                          |

| 7.7  | Power budget for strawman multi-core chip                                               |

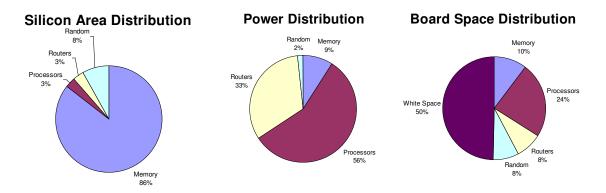

| 7.8  | Area breakdown of processor chip                                                        |

| 7.9  | Power allocation for adaptive node                                                      |

| 7.10 | Exascale class system characteristics derived from aggressive design                    |

|      | Failure rates for the strawman Exascale system                                          |

| 7.12 | · ·                                                                                     |

| 7.13 | Optical interconnect power parameters                                                   |

|      | Optical on-chip interconnect power consumption                                          |

|      | Optical system interconnect power consumption                                           |

| 8.1  | The relationship between research thrusts and challenges                                |

| A.1  | Study Committee Members                                                                 |

## Chapter 1

## **Executive Overview**

This report presents the findings and recommendations of the **Exascale Working Group** as conducted over the summer and fall of 2007. The objectives given the study were to understand the course of mainstream computing technology, and determine whether or not it would allow a 1,000X increase in the computational capabilities of computing systems by the 2015 time frame. If current technology trends were deemed as not capable of permitting such increases, then the study was also charged with identifying where were the major challenges, and in what areas may additional targeted research lay the groundwork for overcoming them.

The use of the word "Exascale" in the study title was deliberately aimed at focusing the group's attention on more than just high end, floating point intensive, supercomputers ("exaflops" machines), but on increasing our ability to perform computations of both traditional and emerging significance at across-the-board levels of performance. The study thus developed as a more precise goal the understanding of technologies to accelerate computing by 1,000X for three distinct classes of systems:

- data center-sized systems, where the focus is on achieving 1,000 times the performance of the "petaflop" class systems that will come on line in the next few years, and for more than just numeric intensive applications.

- departmental-sized systems that would allow the capabilities of the near-term Petascale machines to be shrunk in size and power to fit within a few racks, allowing widespread deployment.

- embedded systems that would allow something approximating a "Terascale" rack of computing such as may be found in the near-term Petascale systems to be reduced to a few chips and a few ten's of watts that would allow deployment in a host of embedded environments.

Clearly, if done right, a technology path that permits Terascale embedded systems would allow variants of that to serve in Petascale departmental systems, and then in turn grow into larger Exascale supercomputers. The study group recognizes that even though the underlying technologies may be similar, when implementing real systems the actual mix of each technology, and even the architecture of the systems themselves may be different. Thus it was not our focus to design such systems, but to develop a deep understanding of the technological challenges that might prohibit their implementation.

<sup>&</sup>lt;sup>1</sup>The term "Exa" is entering the national dialog through discussions of total Internet bandwidth and on-net storage - see for example *Unleashing the 'Exaflood'* in the Feb. 22, 2008 Wall Street Journal.

In total, the study concluded that there are four **major challenges** to achieving Exascale systems where current technology trends are simply insufficient, and significant new research is absolutely needed to bring alternatives on line.

- The Energy and Power Challenge is the most pervasive of the four, and has its roots in the inability of the group to project any combination of currently mature technologies that will deliver sufficiently powerful systems in any class at the desired power levels. Indeed, a key observation of the study is that it may be easier to solve the power problem associated with base computation than it will be to reduce the problem of transporting data from one site to another on the same chip, between closely coupled chips in a common package, or between different racks on opposite sides of a large machine room, or on storing data in the aggregate memory hierarchy.

- The Memory and Storage Challenge concerns the lack of currently available technology to retain data at high enough capacities, and access it at high enough rates, to support the desired application suites at the desired computational rate, and still fit within an acceptable power envelope. This information storage challenge lies in both main memory (DRAM today) and in secondary storage (rotating disks today).

- The Concurrency and Locality Challenge likewise grows out of the flattening of silicon clock rates and the end of increasing single thread performance, which has left explicit, largely programmer visible, parallelism as the only mechanism in silicon to increase overall system performance. While this affects all three classes of systems, projections for the data center class systems in particular indicate that applications may have to support upwards of a billion separate threads to efficiently use the hardware.

- A Resiliency Challenge that deals with the ability of a system to continue operation in the presence of either faults or performance fluctuations. This concern grew out of not only the explosive growth in component count for the larger classes of systems, but also out of the need to use advanced technology, at lower voltage levels, where individual devices and circuits become more and more sensitive to local operating environments, and new classes of aging effects become significant.

While the latter three challenges grew out of the high end systems, they are certainly not limited to that class. One need only look at the explosive grow of highly multi-core microprocessors and their voracious appetite for more RAM.

The study's recommendations are thus that significant research needs to be engaged in four major research thrusts whose effects cross all these challenges:

- 1. Co-development and optimization of Exascale Hardware Technologies and Architectures, where the potential of new devices must be evaluated in the context of new architectures that can utilize the new features of such devices to solve the various challenges. This research includes development of energy efficient circuits for communication, memory, and logic; investigation of alternative low-energy devices; development of efficient packaging, interconnection, and cooling technologies; and energy efficient machine organizations. Each of these research areas should be investigated in the context of all Exascale system classes, and metrics should be in terms of energy efficiency realized in this context.

- 2. Co-development and optimization of Exascale Architectures and Programming Models, where the new architectures that arise out of either the device efforts of the previous

thrust or those needed to control the explosive growth in concurrency must be played out against programming models that allow applications to use them efficiently. This work includes developing locality-aware and communication-efficient architectures to minimize energy consumed through data movement, and developing architectures and programming models capable of handling billion-thread concurrency.

- 3. Co-development of Exascale Algorithms, Applications, Tools, and Run-times, where substantial alternatives are needed for programmers to develop and describe, with less that heroic efforts, applications that can in fact use the new architectures and new technology capabilities in efficient enough ways that permit true "Exascale" levels of performance to be sustained.

- 4. Development of a deep understanding of how to architect **Resilient Exascale Systems**, where the problems in both sheer hardware and algorithmic complexity, and the emergence of new fault mechanisms, are studied in a context that drives the development of circuit, subsystem, and system-level architectures, and the programming models that can exploit them, in ways that allows Exascale systems to provide the kind of dependable service that will make them technically and economically viable.

Further, such research must be very heavily inter-disciplinary. For example, power is the number one concern, but research that focuses only on low-power devices is unlikely to solve the systemic power problems the study encountered. Co-optimization of devices and circuits that employ those devices must be done within the framework of innovative micro and system architectures which can leverage the special features of such devices in the most efficient ways. An explicit and constant attention must be made to **interconnect**, namely the technologies by which one set of functions exchange data with another.

As another example, research that leads to increasing significantly the density of memory parts will clearly help reliability by reducing part count; it may also reduce power significantly by reducing the number of off-chip interfaces that need to be driven, and reduce the number of memory controller circuits that must be incorporated elsewhere.

Finally, if the appropriate technologies are to be developed in time to be considered for 2015 deployments, then, given the level of technical maturity seen by the study group in potential emerging technologies, a three phase research agenda is needed:

- 1. A **System Architecture Exploration Phase** to not only enhance the maturity of some set of underlying device technologies, but to do enough of the higher level system architecture and modeling efforts to identify how best to employ the technology and what the expected value might be at the system level.

- 2. A **Technology Demonstration Phase** where solutions to the "long poles" in the challenges are developed and demonstrated in an isolated manner.

- 3. A Scalability Slice Prototyping Phase where one or more of the disparate technologies demonstrated in the preceding phase are combined into coherent end-to-end "slices" of a complete Exascale system that permits believable scaling to deployable systems. Such slices are not expected to be a complete system in themselves, but should include enough of multiple subsystems from a potential real system that the transition to a real, complete, system integration is feasible and believable.

The rest of this report is organized as follows:

- Chapter 2 defines the major classes of Exascale systems and their attributes.

- Chapter 3 gives some background to this study in terms of prior trends and studies.

- Chapter 4 discuss the structure and inter-relationship of computing systems today, along with some key historical data.

- Chapter 5 concentrates on developing the characteristics of applications that are liable to be relevant to Exascale systems.

- Chapter 6 reviews the suite of relevant technologies as we understand them today, and develops some roadmaps as to how they are likely to improve in the future.

- Chapter 7 takes the best of known currently available technologies, and projects ahead what such technologies would yield at the Exascale. This is particularly critical in identifying the holes in current technology trends, and where the challenges lie.

- Chapter 8 summarizes the major challenges, develops a list of major research thrusts to answer those challenges, and suggests a staged development effort to bring them to fruition.

## Chapter 2

## Defining an Exascale System

The goal of this study was not to design Exascale systems, but to identify the overall challenges and problems that need special emphasis between now and 2010 in order to have a technology base sufficient to support development and deployment of Exascale-class systems by 2015. However, to do this, it is first necessary to define more carefully those classes of systems that would fall under the Exascale rubric. In this chapter, we first discuss the attributes by which achievement of the label "Exascale" may be claimed, then the classes of systems that would lever such attributes into "Exascale" systems.

#### 2.1 Attributes

To get to the point of being able to analyze classes of Exascale systems, we first need a definition of what "Exascale" means. For this study, an Exascale system is taken to mean that one or more key attributes of the system has 1,000 times the value of what an attribute of a "Petascale" system of 2010 will have. The study defined three dimensions for these attributes: functional performance, physical attributes, and application performance. Each is discussed below.

#### 2.1.1 Functional Metrics

We define a functional metric as an attribute of a system that directly measures some parameter that relates to the ability of the system to solve problems. The three major metrics for this category include:

- Basic computational rate: the rate at which some type of operation can be executed per second. This includes, but is not limited to:

- flops: floating point operations per second.

- **IPS**: instructions per second.

- and (remote) **memory accesses** per second.

- Storage capacity: how much memory is available to support holding different forms of the problem state at different times. Specific metrics here include the capacities of various parts of the storage hierarchy:

- Main memory: the memory out of which an application program can directly access data via simple loads and stores.

- Scratch Storage: the memory needed to hold checkpoints, I/O buffers, and the like during a computation.

- **Persistent Storage**: the storage to hold both initial data sets, parameter files, computed results, and long-term data used by multiple independent runs of the application.

- Bandwidth: the rate at which data relevant to computation can be moved around the system, usually between memory and processing logic. Again, a variety of specialized forms of bandwidth metrics are relevant, including:

- Bisection bandwidth: for large systems, what is the bandwidth if we partition the system in half, and measure the maximum that might flow from one half of a system to the other.

- Local memory bandwidth: how fast can data be transferred between memories and closest computational nodes.

- Checkpoint bandwidth: how fast copies of memory can be backed up to a secondary storage medium to permit roll-back to some fixed point in the program if a later error is discovered in the computations due to hardware fault.

- I/O bandwidth: the rate at which data can be extracted from the computational regions of the system to secondary storage or visualization facilities where it can be saved or analyzed later.

- On chip bandwidth: how fast can data be exchanged between functional units and memory structures within a single chip.

#### 2.1.2 Physical Attributes

The second class of attributes that are relevant to an Exascale discussion are those related to the instantiation of the design as a real system, primarily:

- Total power consumption

- Physical size (both area and volume)

- Cost

Since this is primarily a technology study, cost is one metric that will for the most part be ignored.

While peak values for all the above are important, from a technology vantage, it proved to be more relevant to use these metrics as denominators for ratios involving the functional metrics described above. Further, for power it will also be valuable to focus not just on the "per watt" values of a technology, but a "per joule" metric. Knowing the rates per joule allows computation of the total energy needed to solve some problem; dividing by the time desired gives the total power.

#### 2.1.3 Balanced Designs

While individual metrics give valuable insight into a design, more complete evaluations occur when we consider how designs are **balanced**, that is how equal in efficiency of use is the design with respect to different high-cost resources. This balance is usually a function of application class.

For example, some systems based on special purpose processor designs such as Grape[97] may be "well-balanced" for some narrow classes of applications that consume the whole machine (such as multi-body problems), but become very inefficient when applied to others (insufficient memory, bandwidth, or ability to manage long latencies). Other systems such as large scale search engines may be built out of more commodity components, but have specialized software stacks and are balanced so that they perform well only for loads consisting of large numbers of short, independent, queries that interact only through access to large, persistent databases.

Classically, such balance discussions have been reduced to simple ratios of metrics from above, such as "bytes to flops per second" or "Gb/s per flops per second." While useful historical vignettes, care must be taken with such ratios when looking at different scales of applications, and different application classes.

#### 2.1.4 Application Performance

There are two major reasons why one invests in a new computing system: for solving problems not previously solvable, either because of time to solution or size of problem, or for solving the same kinds of problems solved on a prior system, but faster or more frequently. Systems that are built for such purposes are known as capability and capacity systems respectively. The NRC report *Getting Up to Speed* ([54] page 24) defines these terms more formally:

The largest supercomputers are used for **capability** or turnaround computing where the maximum processing power is applied to a single problem. The goal is to solve a larger problem, or to solve a single problem in a shorter period of time. Capability computing also enables the solution of problems that cannot otherwise be solved in a reasonable period of time (for example, by moving from a two-dimensional to a three-dimensional simulation, using finer grids, or using more realistic models). Capability computing also enables the solution of problems with real-time constraints (e.g. intelligence processing and analysis). The main figure of merit is time to solution.

Smaller or cheaper systems are used for **capacity** computing, where smaller problems are solved. Capacity computing can be used to enable parametric studies or to explore design alternatives; it is often needed to prepare for more expensive runs on capability systems. Capacity systems will often run several jobs simultaneously. The main figure of merit is sustained performance per unit cost.

Capacity machines are designed for throughput acceleration; they accelerate the rate at which certain types of currently solvable applications can be solved. Capability machines change the spectrum of applications that are now "solvable," either because such problems can now be fit in the machine and solved at all, or because they can now be solved fast enough for the results to be meaningful (such as weather forecasting).

We note that there is significant fuzziness in these definitions, especially in the "real-time" arena. A machine may be called a capability machine if it can take a problem that is solvable in prior generations of machines (but not in time for the results to be useful), and make it solvable (at the same levels of accuracy) in some fixed period of time where the results have value (such a weather forecasting). A machine that solves the same problems even faster, or solves multiple versions concurrently, and still in real-time, may be called a capacity machine. It is not uncommon for today's capability systems to become tomorrow's capacity systems and newer, and even more capable, machines are introduced.

Also, some machines may have significant aspects of both, such as large scale search engines, where the capability part lies in the ability to retain significant indexes to information, and the capacity part lies in the ability to handle very large numbers of simultaneous queries.

Although there is significant validity to the premise that the difference between a capacity and a capability machine may be just in the "style" of computing or in a job scheduling policy, we will continue the distinction here a bit further mainly because it may affect several system parameters that in turn affect real hardware and related technology needs. In particular, it may relate to the breadth of applications for which a particular design point is "balanced" to the point of being economically valuable. As an example, it appears from the strawmen designs of Chapter 7 that silicon-based Exascale machines may be significantly memory-poor in relation to today's supercomputing systems. This may be acceptable for some large "capability" problems where the volume of computation scales faster than required data size, but not for "capacity" applications where there is insufficient per-node memory space to allow enough copies of enough different data sets to reside simultaneously in the machine in a way that can use all the computational capabilities.

#### 2.2 Classes of Exascale Systems

To reiterate the purpose of this study, it is to identify those technology challenges that stand in the way of achieving initial deployment of Exascale systems by 2015. The approach taken here for identifying when such future systems may be called "Exascale" is multi-step. First, we partition the Exascale space based on the gross physical characteristics of a deployed system. Then, we identify the functional and application performance characteristics we expect to see needed to achieve "1,000X" increase in "capability." Finally, we look at the ratios of these characteristics to power and volume as discussed above. Then by looking at these ratios we can identify where the largest challenges are liable to arise, and which class of systems will exhibit them.

In terms of overall physical size and power, we partition the 2015 system space into three categories:

- "Exa-sized" data center systems,

- "Peta-sized" departmental computing systems,

- and "Tera-sized" Embedded systems.

It is very important to understand that these three systems are not just a 1,000X or 1,000,000X scaling in all parameters. Depending on the application class for each level, the individual mix of parameters such as computational rates, memory capacity, and memory bandwidth may vary dramatically.

#### 2.2.1 Data Center System

For this study, an exa-sized **data center system** of 2015 is one that roughly corresponds to a typical notion of a supercomputer center today - a large machine room of several thousand square feet and multiple megawatts of power consumption. This is the class system that would fall in the same footprint as the Petascale systems of 2010, except with 1,000X the capability. Because of the difficulty of achieving such physical constraints, the study was permitted to assume some growth, perhaps a factor of 2X, to something with a maximum limit of 500 racks and 20 MW for the computational part of the 2015 system.

#### 2.2.2 Exascale and HPC

In high-end computing (i.e. supercomputing or high-performance computing), the major milestones are the emergence of systems whose aggregate performance first crosses a threshold of  $10^{3k}$  operations performed per second, for some k. Gigascale ( $10^9$ ) was achieved in 1985 with the delivery of the Cray 2. Terascale ( $10^{12}$ ) was achieved in 1997 with the delivery of the Intel ASCI Red system to Sandia National Laboratory. Today, there are contracts for near-Petascale ( $10^{15}$ ) systems, and the first will likely be deployed in 2008. Assuming that progress continues to accelerate, one might hope to see an Exascale ( $10^{18}$ ) system as early as 2015.

For most scientific and engineering applications, Exascale implies 10<sup>18</sup> IEEE 754 Double Precision (64-bit) operations (multiplications and/or additions) per second (**exaflops**<sup>1</sup>). The **High Performance Linpack** (**HPL**) benchmark[118], which solves a dense linear system using LU factorization with partial pivoting, is the current benchmark by which the community measures the throughput of a computing system. To be generally accepted as an Exascale system, a computer must exceed 10<sup>18</sup> flops (1 exaflops) on the HPL benchmark. However, there are critical Defense and Intelligence problems for which the operations would be over the integers or some other number field. Thus a true Exascale system has to execute a fairly rich instruction set at 10<sup>18</sup> operations per second lest it be simply a special purpose machine for one small family of problems.

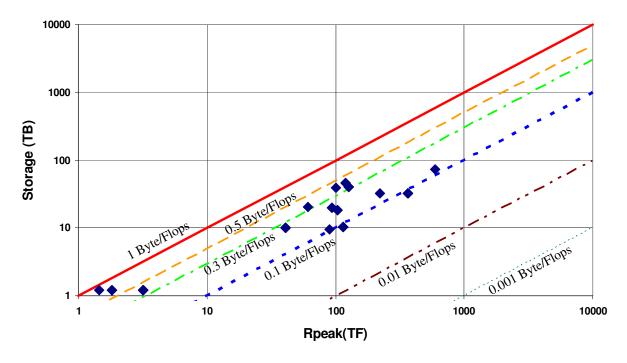

A truly general purpose computer must provide a balance of arithmetic throughput with memory volume, memory and communication bandwidth, persistent storage, etc. To perform the HPL benchmark in a reasonable period of time, an Exascale system would require on the order of 10 petabytes (10<sup>16</sup> Bytes) of main memory. Such a system could credibly solve a small set of other problems. However, it would need at least another order-of-magnitude of additional main memory (10<sup>17</sup> bytes) to address as broad a range of problems as will be tackled on near-Petascale systems in the next year or so. Amdahl's rule of thumb was one byte of main memory per operation, but in recent years systems have been deployed with less (0.14 to 0.3), reflecting both the diverging relative costs of the components as well as the evolving needs of applications. Chapter 5 tries to get a better handle on this as we scale algorithms up.

Finally, an Exascale system must provide data bandwidth to and from at least local subsets of its memory at approximately an exabyte per second. Section 5.6 discusses sensitivities of many current algorithms to bandwidth.

To store checkpoints, intermediate files, external data, results, and to stage jobs, an Exascale system will need at least another order-of-magnitude (i.e.,  $10^{18}$  Bytes) of persistent storage, analogous to today's disk arrays, with another 10-100X for file storage. Section 5.6.3 explores these numbers in more detail.

#### 2.2.3 Departmental Systems

The discussion in the previous was oriented towards the requirements for a leadership-class Exascale system deployed to support a handful of national-scale, capability jobs. To be economically viable, the technology developed for such a system must also be utilized in higher volume systems such as those deployed for departmental-scale computing in industry and government. To the casual eye, the biggest difference will be in the physical size of the departmental systems, which will only fill a few racks. Power density will be a critical aspect of these systems, as many customers will want them to be air cooled. Others may only have building chilled water available. Thus, a petasized **departmental system** of 2015 would be one whose computational capabilities would match

$<sup>^{1}</sup>$ We denote a computation involving a total of  $10^{18}$  floating point operations as an **exaflop** of computation; if they are all performed in one second then the performance is one **exaflops**.

roughly those of a 2010 Petascale data center-sized system, but in the form factor of a departmental computing cluster - perhaps one or two racks, with a maximum power budget of what could be found in reasonable computer "cluster" room of today - perhaps 100-200KW at maximum. In a sense this is around 1/1,000th in both capability and size of the larger systems.

The principle differentiation between the Exascale data center systems and departmental systems will be the need to support a large set of third-party applications. These span a broad range from business applications like Oracle to engineering codes like LS-DYNA[32]. These are very large, sophisticated applications that demand the services of a full featured operating system, usually a derivative of UNIX, not a micro-kernel as may suffice on the early Exascale systems. The operating system will need to support virtualization and to interact with a **Grid**[45] of external systems as the department will likely be part of a much larger, geographically distributed enterprize.

To support a broad range of such mainstream applications, departmental systems composed of Exascale components will require a proportionately larger main memory and persistent store. It's not uncommon today to see systems such as the SGI Altix delivered with only four Intel Itanium CPUs yet a terabyte of main memory. Latency and bandwidth to the memory hierarchy (DRAM and disk) is already a problem today for mainstream applications, and probably cannot be tapered as aggressively as it likely will be on a leadership, Exascale system.

The third party applications whose availability will be critical to the success of departmental scale systems in 2015 run on up to 100 processors today. Only a handful of scaling studies or heroic runs exceed that. Petascale departmental systems will likely have 10<sup>5</sup>, perhaps even 10<sup>6</sup> threads in them. Extending enough of today's applications to this level of parallelism will be a daunting task. In the last fifteen years, commercial software developers have struggled to transition their codes from one CPU (perhaps a vector system) to O(1000) today. They will have to expand this scalability by another three orders-of-magnitude in the next decade. This will require breakthroughs not only in computer architecture, compilers and other software tools, but also in diverse areas of applied mathematics, science, and engineering. Not amount of system concurrency can overcome an algorithm that does not scale well. Finally, mainstream applications can not be expected to have evolved to the point where they can adapt to faults in the underlying system. Thus mean-time-to failure comparable to today's large-scale servers will be necessary.

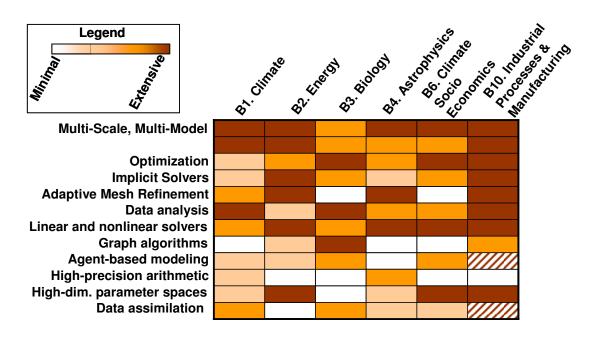

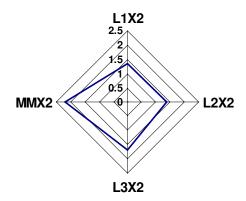

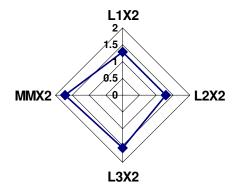

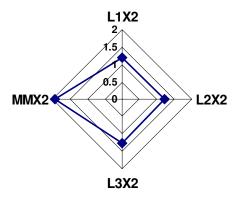

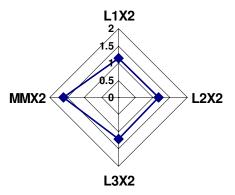

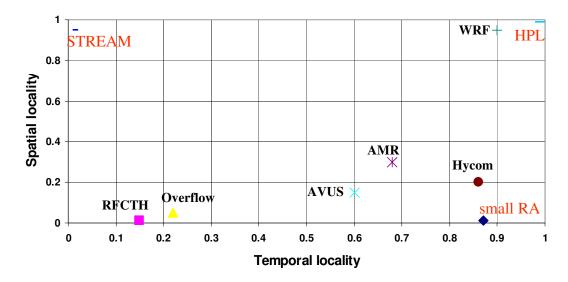

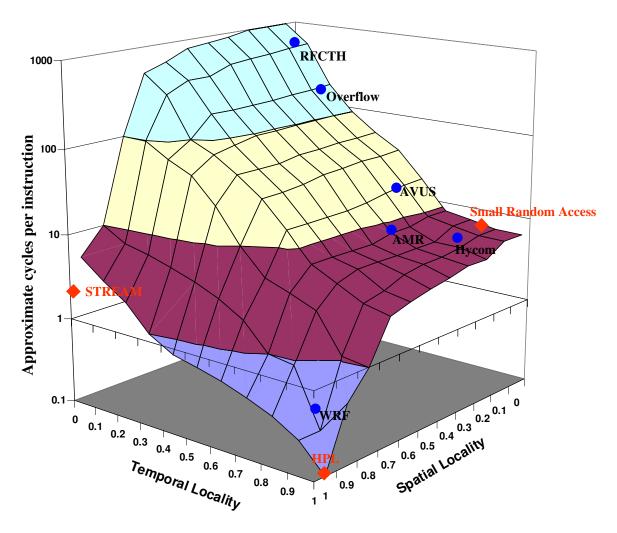

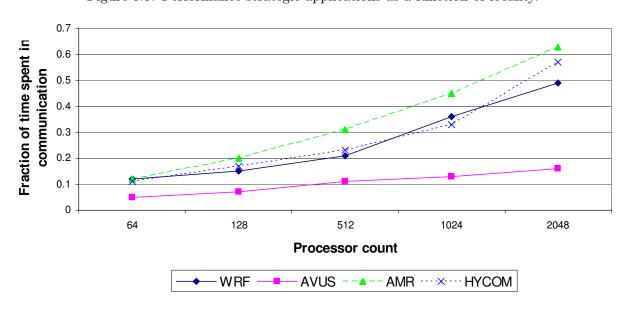

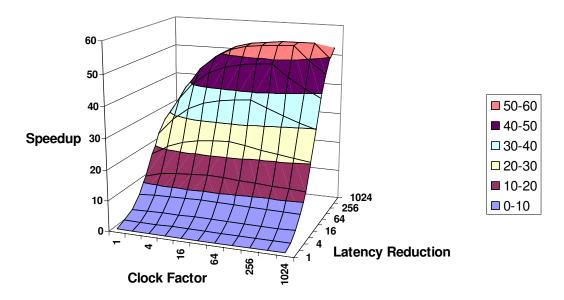

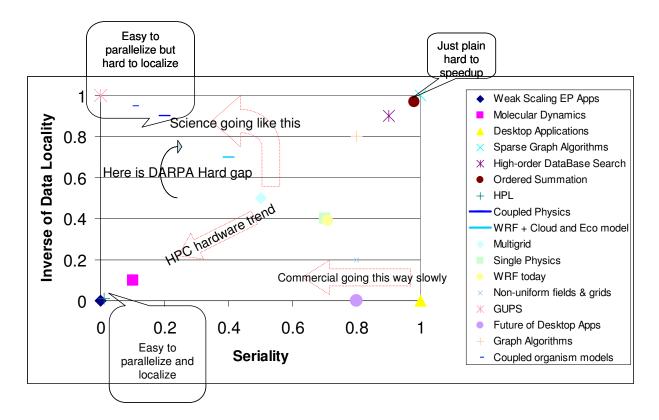

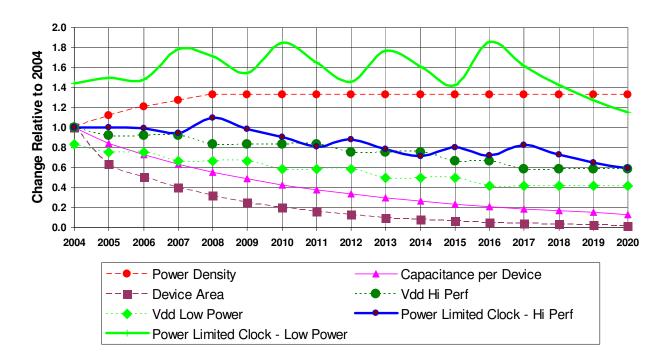

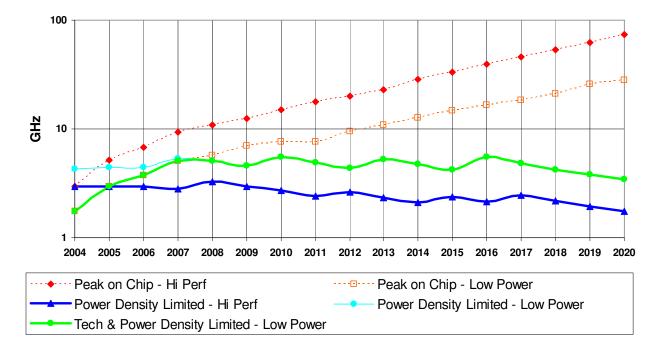

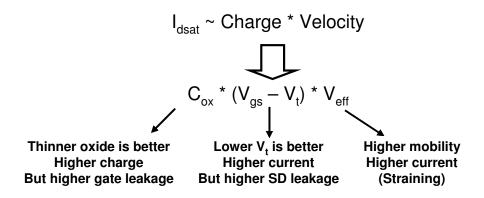

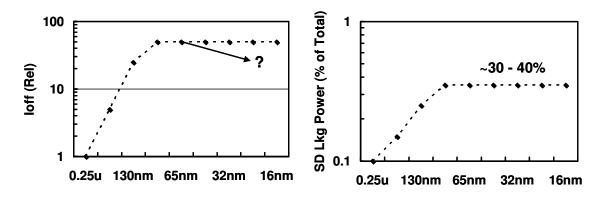

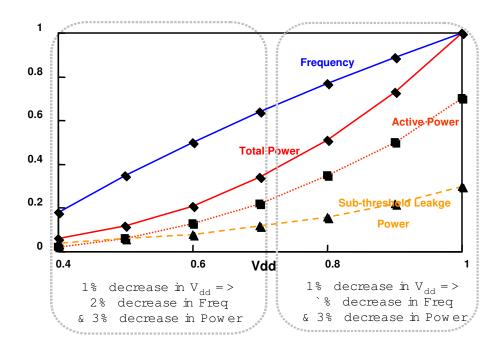

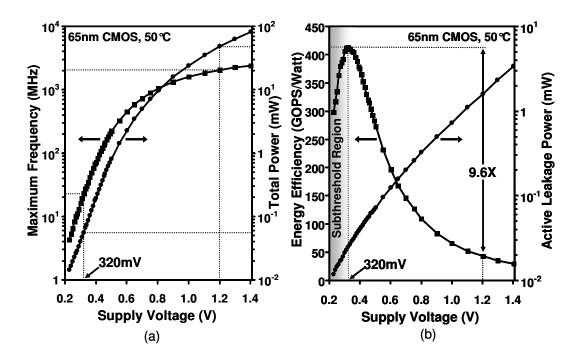

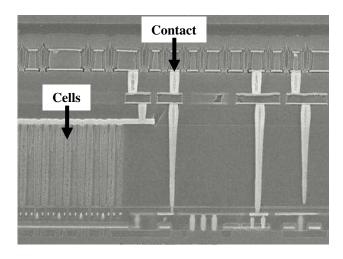

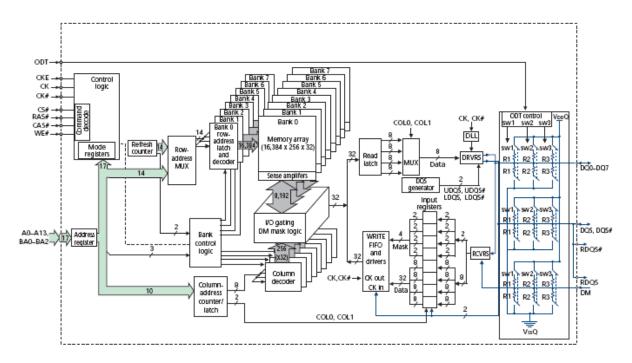

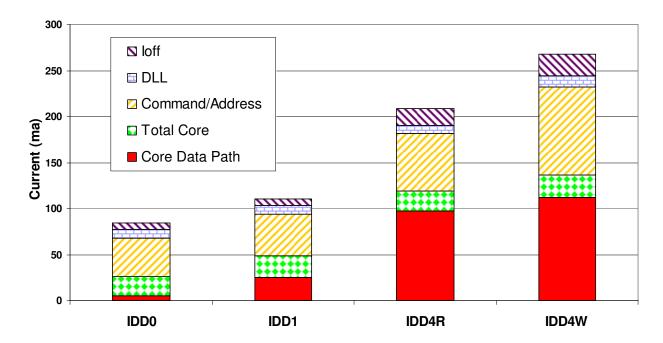

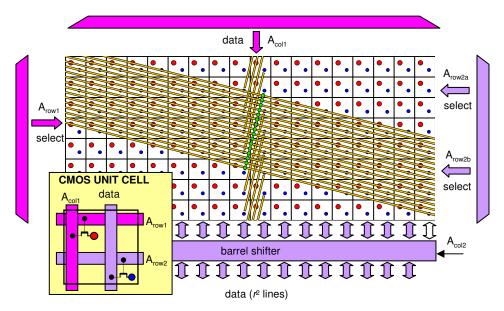

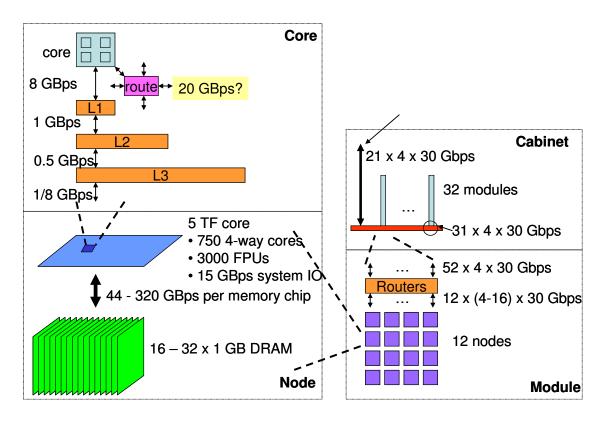

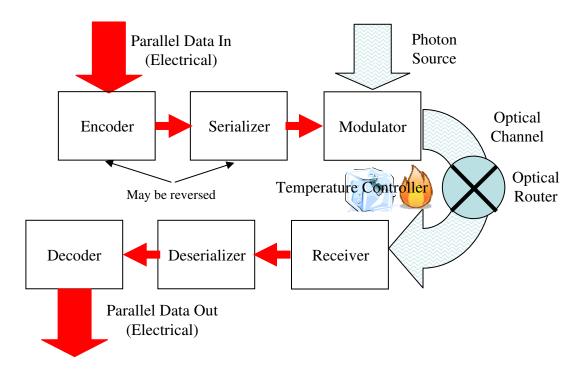

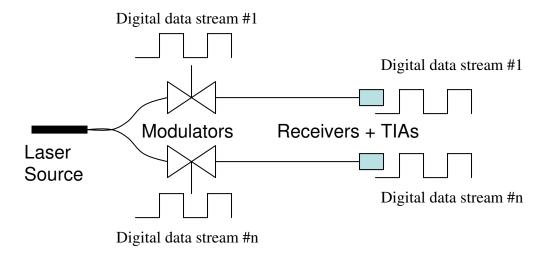

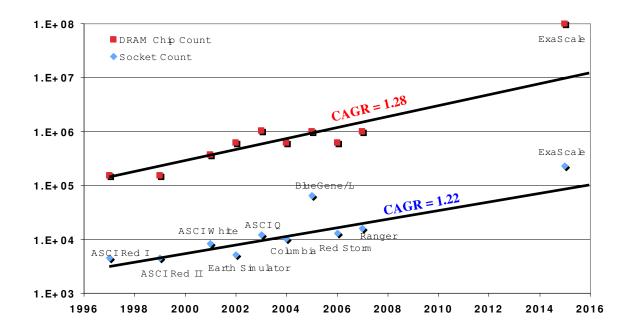

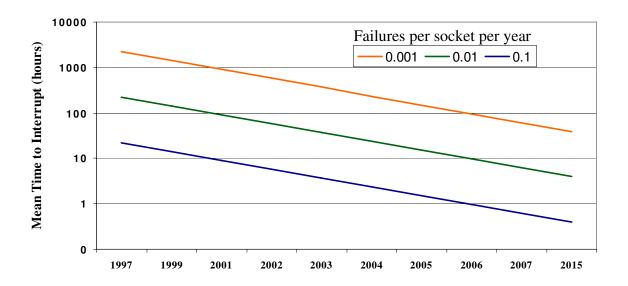

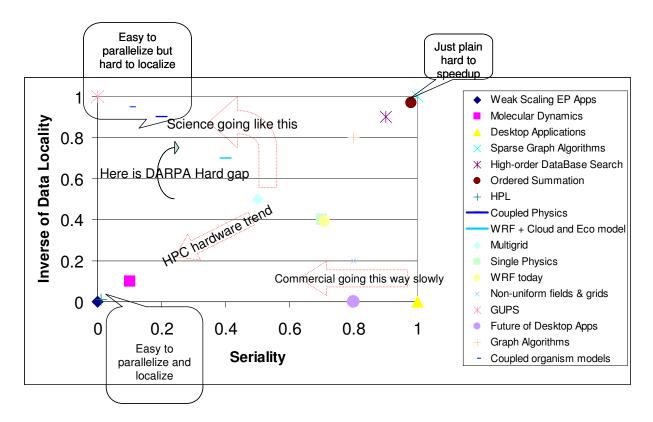

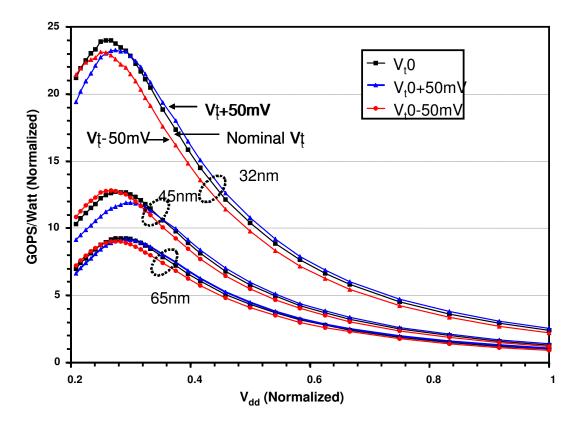

#### 2.2.4 Embedded Systems