# Recent Progress and Challenges for Relay Logic Switch Technology

Tsu-Jae King Liu

Louis Hutin, I-Ru Chen, Rhesa Nathanael, Yenhao Chen, Matthew Spencer and Elad Alon

Electrical Engineering and Computer Sciences Department University of California, Berkeley, CA USA

June 12, 2012

#### **Outline**

- Introduction

- Why relays?

- Relay-based IC design

- Recent Progress

- Current Challenges

- Conclusion

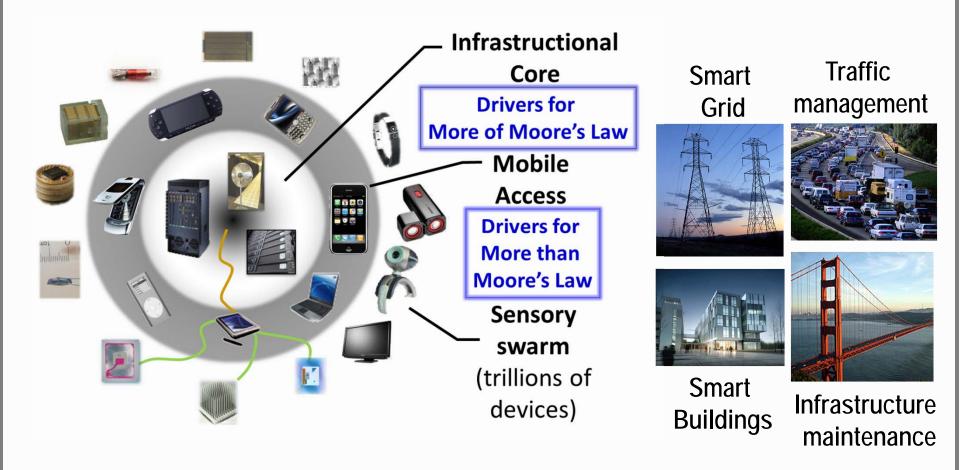

#### Vision of the Future: Swarms of Electronics

#### Emergence of Ambient Intelligence

- Sense/monitor, communicate, and react to the environment

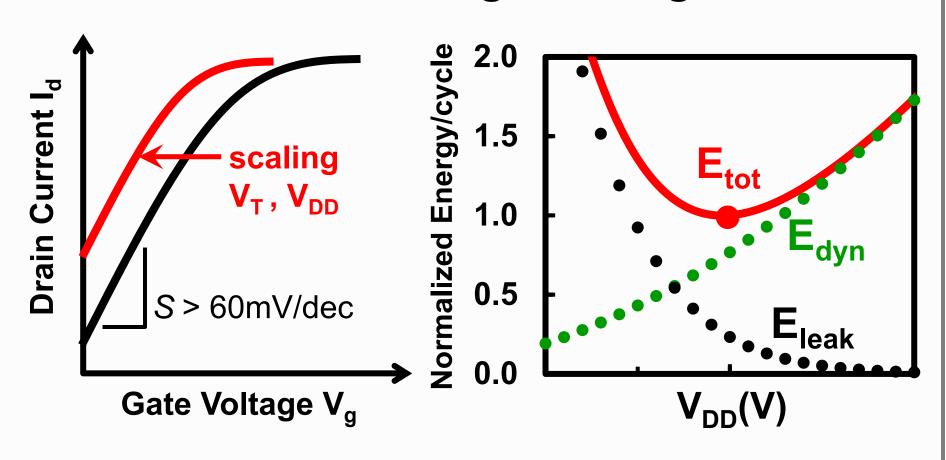

#### **CMOS Voltage Scaling**

- Scaling supply voltage (V<sub>DD</sub>) reduces circuit speed

- Scaling threshold voltage (V<sub>T</sub>) increases leakage

### Why Relays?

- Zero OFF-state current (I<sub>OFF</sub>); abrupt switching

- Turns on by electrostatic actuation when |V<sub>GS</sub>| ≥ V<sub>PI</sub>

- Turns off by spring restoring force when  $|V_{GS}| \le V_{RL}$

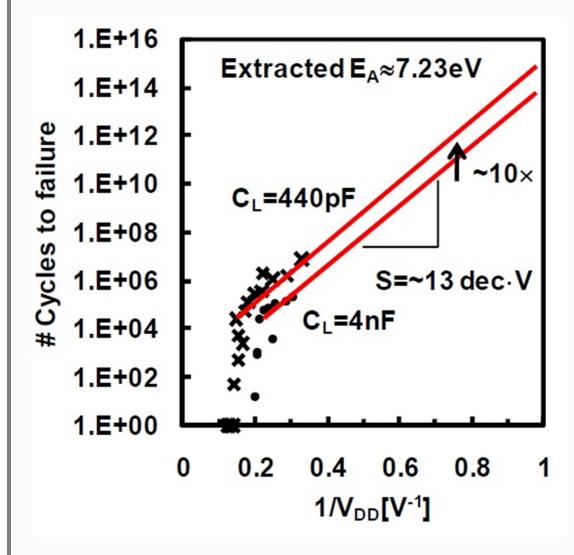

#### **Relay Endurance**

- Endurance increases exponentially with decreasing  $V_{\rm DD}$ , and linearly with decreasing  $C_{\rm L}$

- Endurance is projected to exceed 10<sup>15</sup> cycles @ 1V

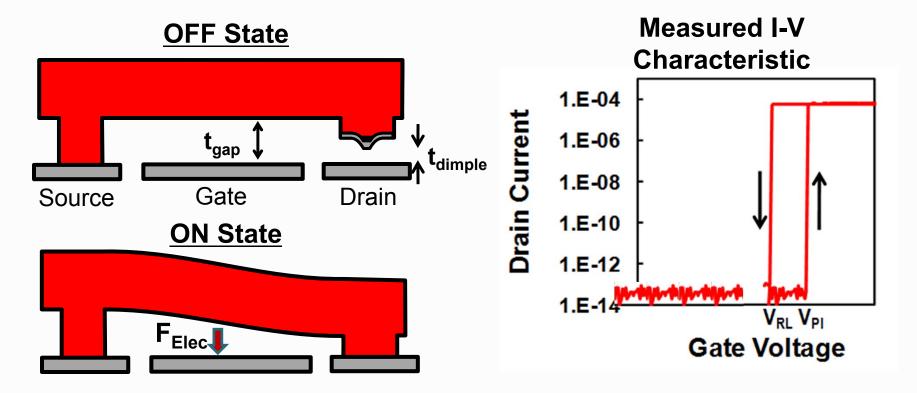

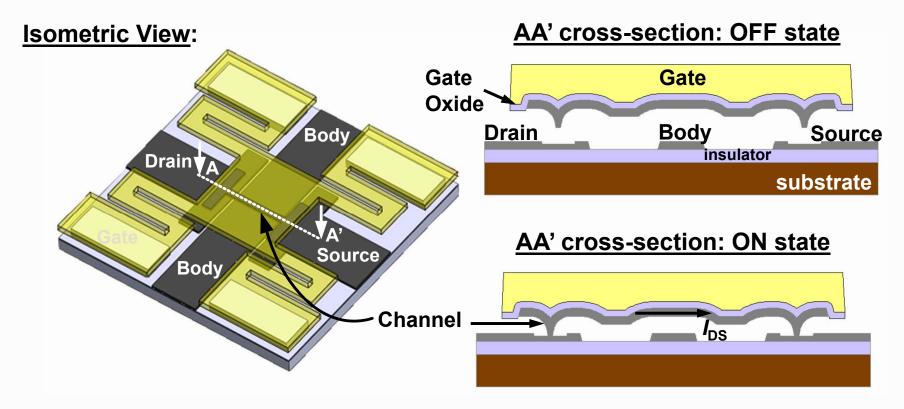

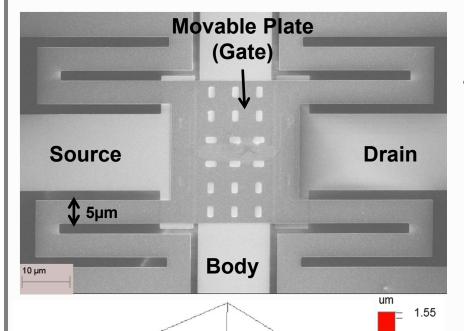

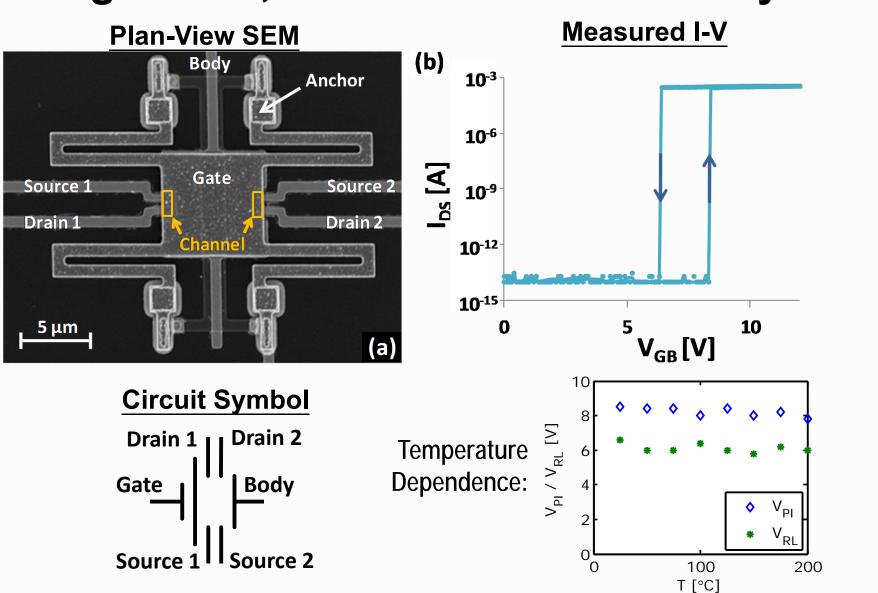

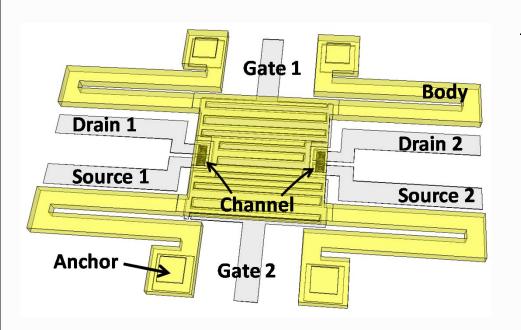

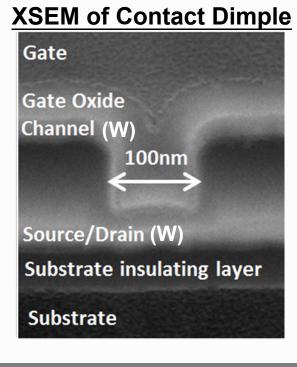

## 4-Terminal (4-T) Relay for Digital Logic

- Voltage applied between the gate and body brings the channel into contact with the source and drain.

- Folded-flexure design relieves residual stress.

- Gate oxide layer insulates the channel from the gate.

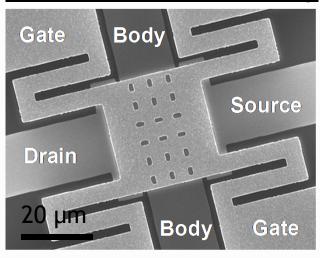

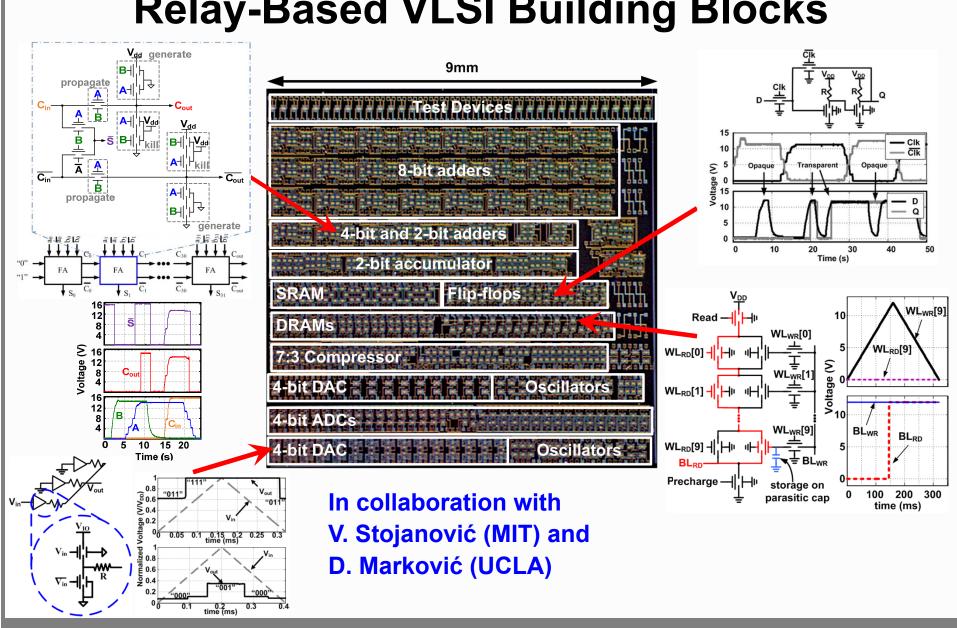

# 4-T Relay $I_D$ - $V_G$ Characteristics

Plan View SEM of 4-T Relay

- Zero I<sub>OFF</sub> and abrupt switching behavior observed

- Hysteresis is due to pull-in mode operation (t<sub>dimple</sub> > t<sub>qap</sub>/3) and contact surface adhesion.

## Digital IC Design with Relays

- CMOS: delay is set by electrical time constant

- Quadratic delay penalty for stacking devices

- → Buffer & distribute logical/electrical effort over many stages

- Relays: delay is dominated by mechanical movement

- Can stack ~100 devices before t<sub>elec</sub> ≈ t<sub>mech</sub>

- → Implement relay logic as a single complex gate

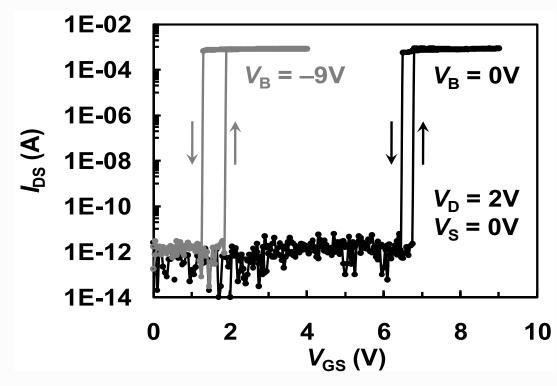

# Relay-Based VLSI Building Blocks

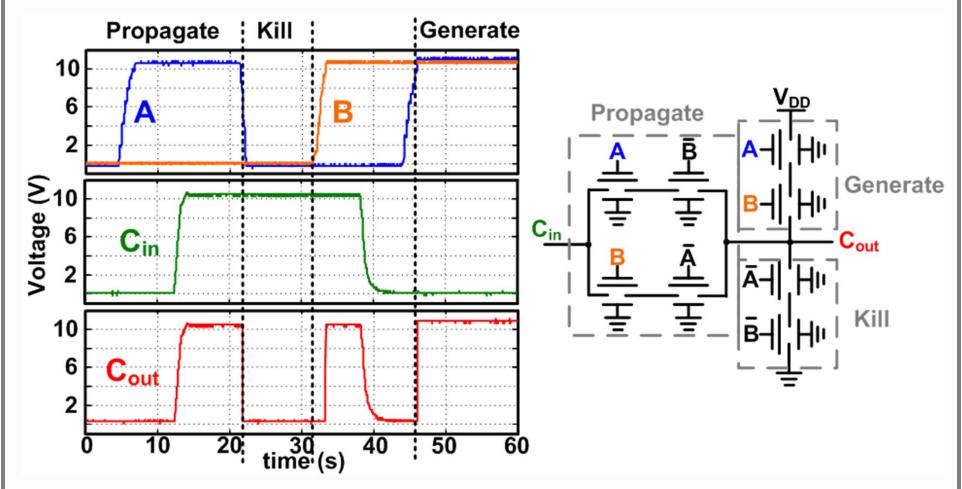

## **Relay Carry Generation Circuit**

Demonstrates propagate-generate-kill logic as a single complex gate

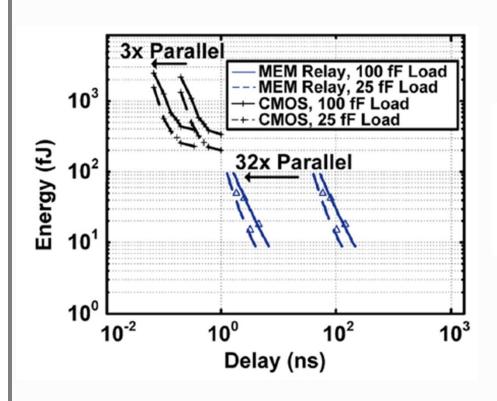

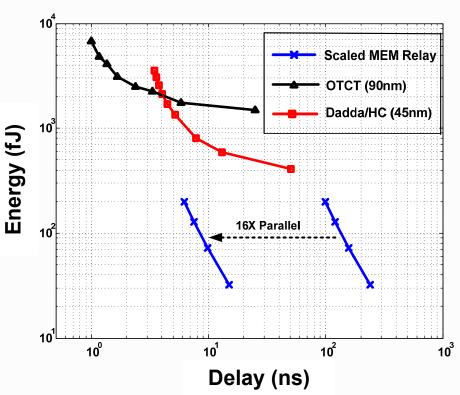

### **Energy-Delay Comparison with CMOS**

90nm relay vs. CMOS adders and multipliers:

>2-100× energy savings @ 3-100× higher delay

#### **Outline**

- Introduction

- Recent Progress

- Relay scaling

- Multi-input/multi-output relay designs

- Current Challenges

- Conclusion

### **Structural Layer Requirements**

• To reduce  $V_{Pl}$ , the effective spring constant  $(k_{eff})$  and actuation gap thickness  $(t_{gap})$  must be reduced.

$$V_{PI} \propto \sqrt{\frac{k_{eff}t_{gap}^3}{\varepsilon_0 A}}$$

where  $k_{eff} \propto \frac{EWh^3}{L^3}$

- → Need to reduce the structural layer thickness (h)

- Strain gradient causes out-of-plane bending

$$\frac{1}{\rho} = \frac{2\Delta z}{L^2} \propto \frac{M}{EWh^3}$$

$\Delta z$ : tip deflection  $\rho$ : radius of curvature  $\Delta z$ : tip deflection  $\Delta z$ : tip deflection

→ Need very low strain gradient

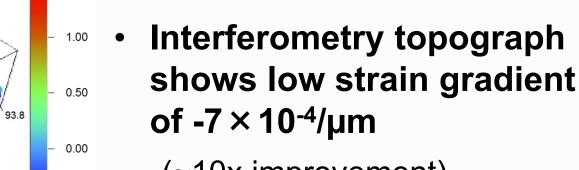

#### Structural Film Development

1.5

-0.7 79.0

- Thin TiN + poly-Si<sub>0.4</sub>Ge<sub>0.6</sub>

bi-layer stack:

- Tensile TiN compensates

strain gradient in Si<sub>0.4</sub>Ge<sub>0.6</sub>

(~10x improvement)

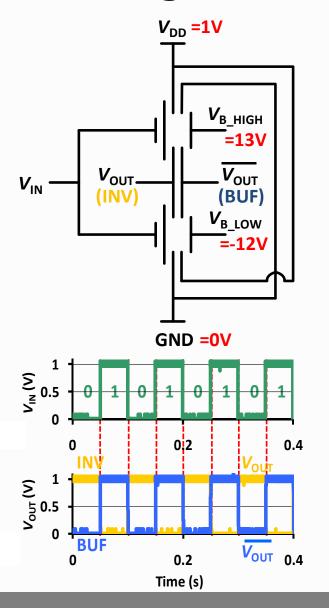

## Single-Gate, Dual-Source/Drain Relay

## Single-Gate Relay Inverter/Buffer

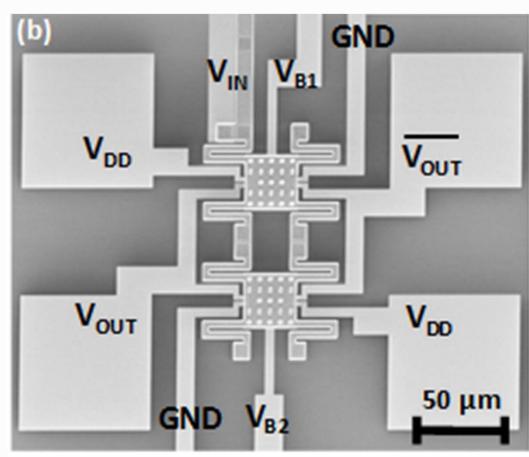

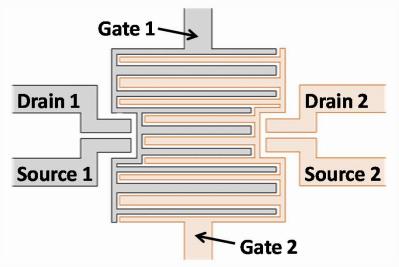

#### **Dual-Gate, Dual Source/Drain Relay**

#### **Bottom (Gate) Electrode Layout**

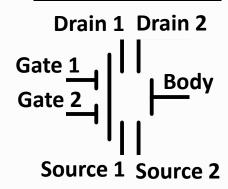

#### **Circuit Symbol**

Gate electrodes are interdigitated to ensure that each gate has equal influence on the movable body

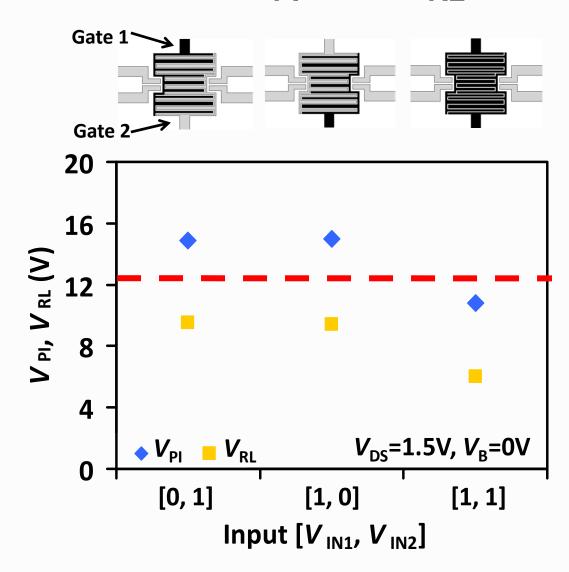

## Measured $V_{Pl}$ and $V_{RL}$ of a Dual-Gate Relay

- "1"≡V<sub>G</sub>

- Each gate has equal influence

- Depending on V<sub>B</sub>, relay can be actuated using one or two gate electrodes

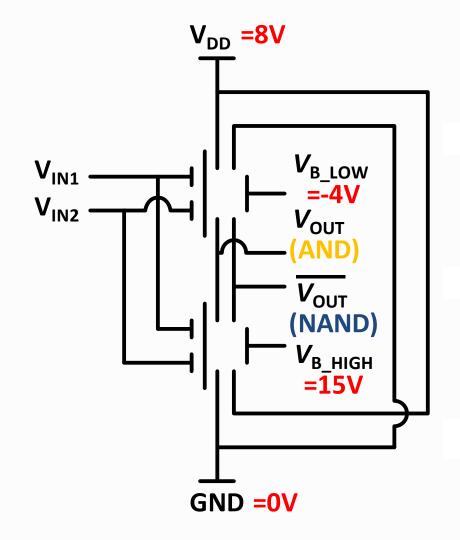

### **Dual-Gate Relay Circuit: AND/NAND**

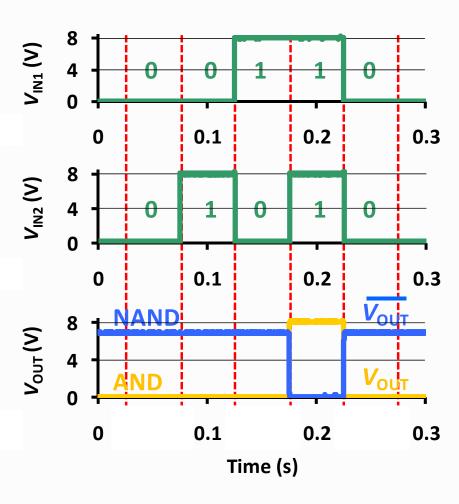

## **Dual-Gate Relay Circuit: OR/NOR**

#### **Outline**

- Introduction

- Recent Progress

- Current Challenges

- Contact resistance

- Surface adhesion

- Conclusion

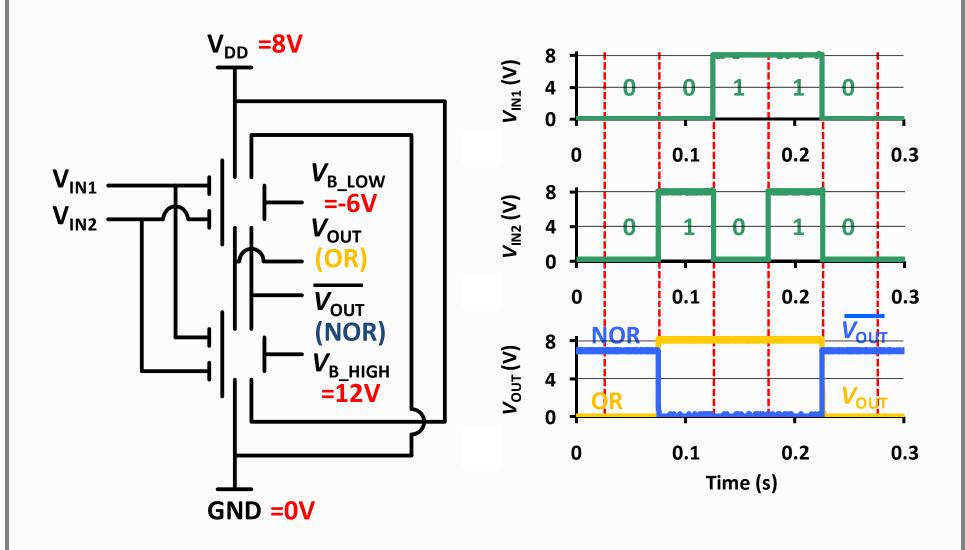

### **Tungsten Contact Resistance Evolution**

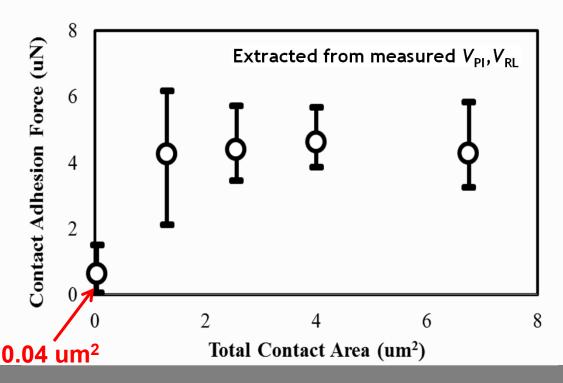

#### Stiction: The Ultimate Relay Scaling Limiter

Hysteresis voltage (V<sub>PI</sub>-V<sub>RL</sub>) scales with V<sub>PI</sub>:

$$V_{PI} - V_{RL} = V_{PI} \left[ 1 - 2.6 \sqrt{\frac{t_{dimple}}{t_{gap}}} \left( 1 - \frac{t_{dimple}}{t_{gap}} \right) \right]$$

ignoring surface adhesion force

Adhesive force reduces with contacting region area:

#### **Outline**

- Introduction

- Recent Progress

- Current Challenges

- Conclusion

#### Conclusion

- Relays have zero l<sub>OFF</sub> and can incorporate multiple input/output electrodes

- → potentially can achieve lower energy per operation and greater functionality per device than CMOS for digital logic applications.

- Practical challenges remain to be solved:

- Contact surface oxidation

- Minimization of adhesion force within R<sub>ON</sub> limits

- Development of ultra-thin structural films with very low strain gradient

#### **Acknowledgments**

#### Collaborators:

- Fred Chen, Hossein Fariborzi, Prof. Vladimir Stojanović (MIT)

- Chengcheng Wang, Kevin Dwan, Prof. Dejan Marković (UCLA)

#### Funding sources:

- DARPA/MTO NEMS Program

- SRC/DARPA Focus Center Research Program

- NSF Center for Energy Efficient Electronics Science (E3S)

- NSF Center of Integrated Nanomechanical Systems (COINS)

- Berkeley Wireless Research Center

#### Device fabrication support:

- UC Berkeley Marvell Nanofabrication Laboratory

- SVTC Technologies & SPTS Technologies