## Segmented-Channel $Si_{1-x}Ge_x/Si pMOSFET$ for Improved I<sub>ON</sub> and Reduced Variability

<u>Byron Ho</u><sup>1</sup>, Nuo Xu<sup>1</sup>, Bingxi Wood<sup>2</sup>, Vinh Tran<sup>2</sup>, Saurabh Chopra<sup>2</sup>, Yihwan Kim<sup>2</sup>, Bich-Yen Nguyen<sup>3</sup>, Olivier Bonnin<sup>3</sup>, Carlos Mazure<sup>3</sup>, Satheesh Kuppurao<sup>2</sup>, Chorng-Ping Chang<sup>2</sup>, Tsu-Jae King Liu<sup>1</sup>

> <sup>1</sup>University of California at Berkeley, <sup>2</sup>Applied Materials, Inc. <sup>3</sup>Soitec

# Outline

#### Introduction

- Why silicon-germanium (Si<sub>1-x</sub>Ge<sub>x</sub>) ?

- Segmented-channel MOSFET (SegFET) design

#### Device Fabrication

- Corrugated substrate

- p-channel MOSFETs

- Results and Discussion

- Conclusion

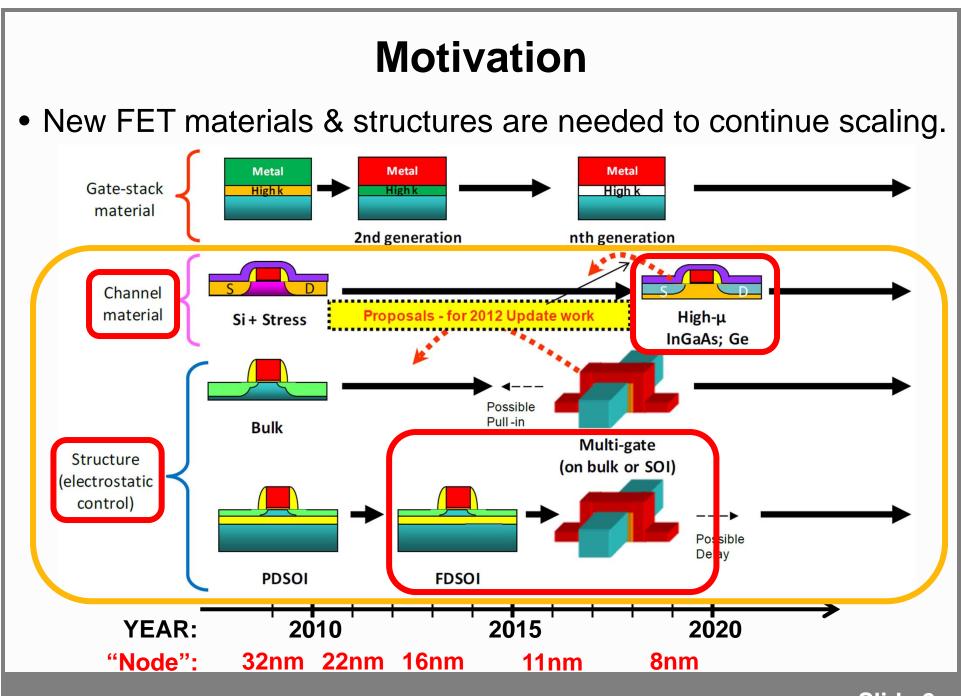

International Technology Roadmap for Semiconductors, 2011 Executive Summary

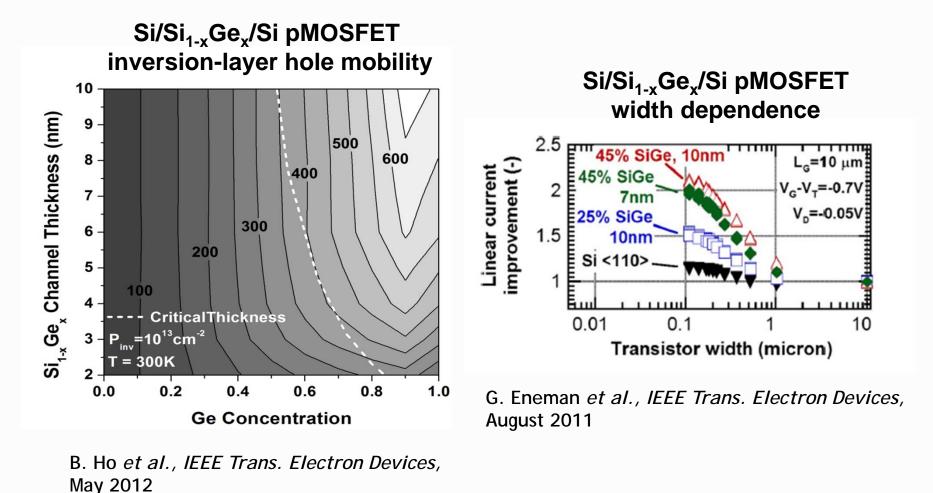

# Why Si<sub>1-x</sub>Ge<sub>x</sub> ?

• Enhanced hole mobility ... but significant width dependence

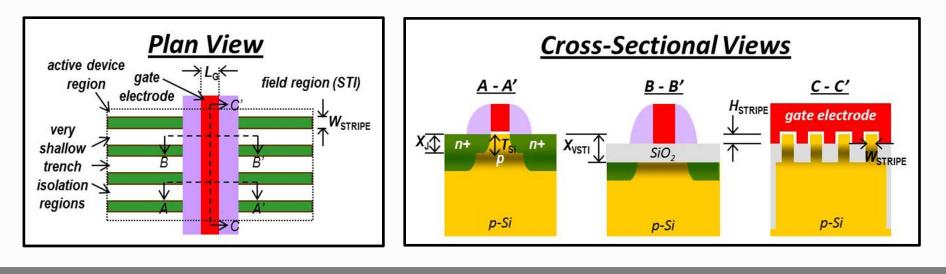

# Segmented Channel MOSFET (SegFET)

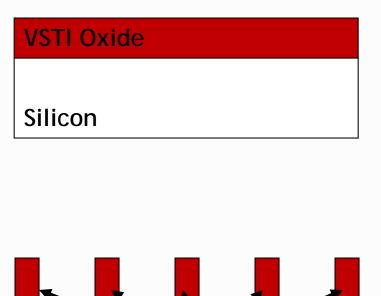

- Channel comprises parallel stripes of <u>equal width</u>, isolated by <u>very shallow trench isolation</u> (VSTI).

−VSTI is much shallower than the STI between transistors

→ Source/drain regions are contiguous!

- <u>Electrostatic control is enhanced</u> by fringing E-fields; also, the channel stripes can be slightly elevated above the VSTI so that the gate stack wraps their top portions.

B. Ho et al., International Semiconductor Device Research Symposium 2011

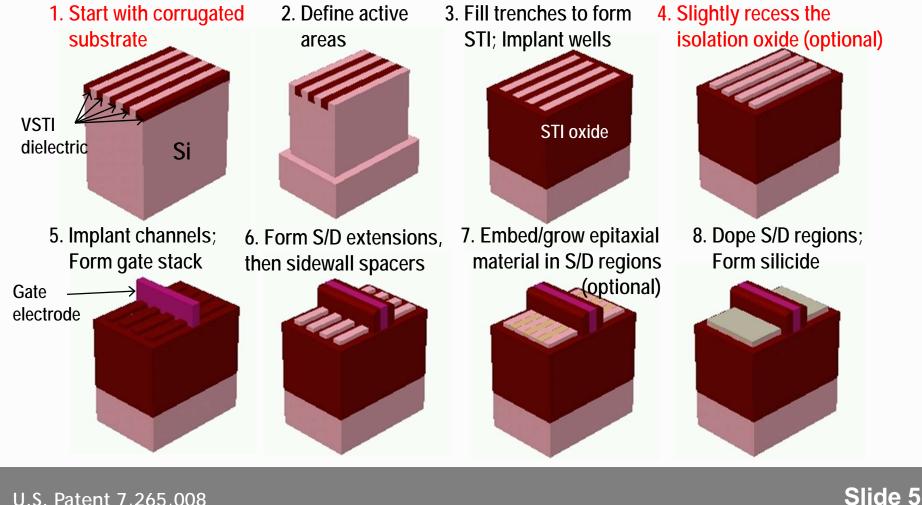

## **SegFET Fabrication**

Conventional CMOS process starting w/ corrugated substrate

- Geometrically regular pattern  $\rightarrow$  uniform stripe width

# This Work

Fabrication of segmented vs. conventional (non-segmented) Si<sub>1-x</sub>Ge<sub>x</sub>/Si pMOSFETs <u>using</u> the same process flow

*i.e.*, corrugated substrate vs. non-corrugated substrate

- Comparison of MOSFET drive current per unit layout width

*i.e.*, layout area efficiency

- Comparison of active area width dependence

# Outline

- Introduction

- Why silicon-germanium (Si<sub>1-x</sub>Ge<sub>x</sub>) ?

- Segmented-channel MOSFET (SegFET) design

#### • Device Fabrication

- Corrugated substrate

- p-channel MOSFETs

- Results and Discussion

- Conclusion

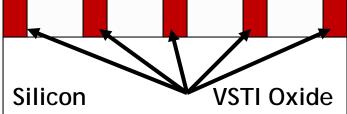

### **Corrugated Substrate Fabrication**

- Start with Si wafer substrate

Deposit/grow VSTI oxide layer

- 20 nm SiO<sub>2</sub>

Pattern VSTI layer to form 30 nm/70 nm lines/spaces (double patterning)

#### **Corrugated Substrate Fabrication (cont'd)** Selectively grow silicon epitaxially, to fill trenches 20 nm Si epitaxial Si Silicon Selectively grow segmented channel regions epitaxial Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si 2 nm Si<sub>0.5</sub>Ge<sub>0.5</sub> 3 nm Si cap

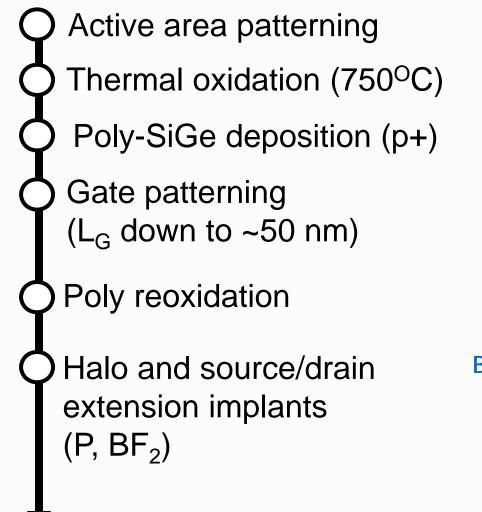

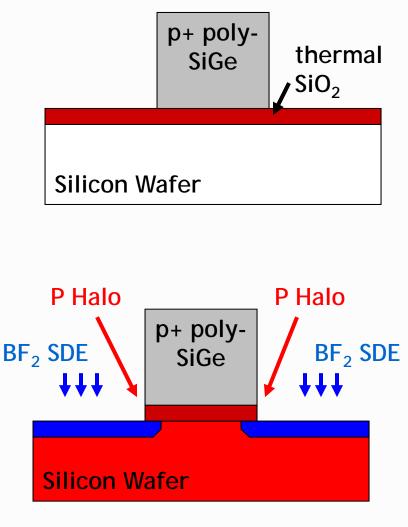

pMOSFET Device Fabrication

Note: Same epi growth done on planar (un-corrugated) substrates for planar control devices

Silicon

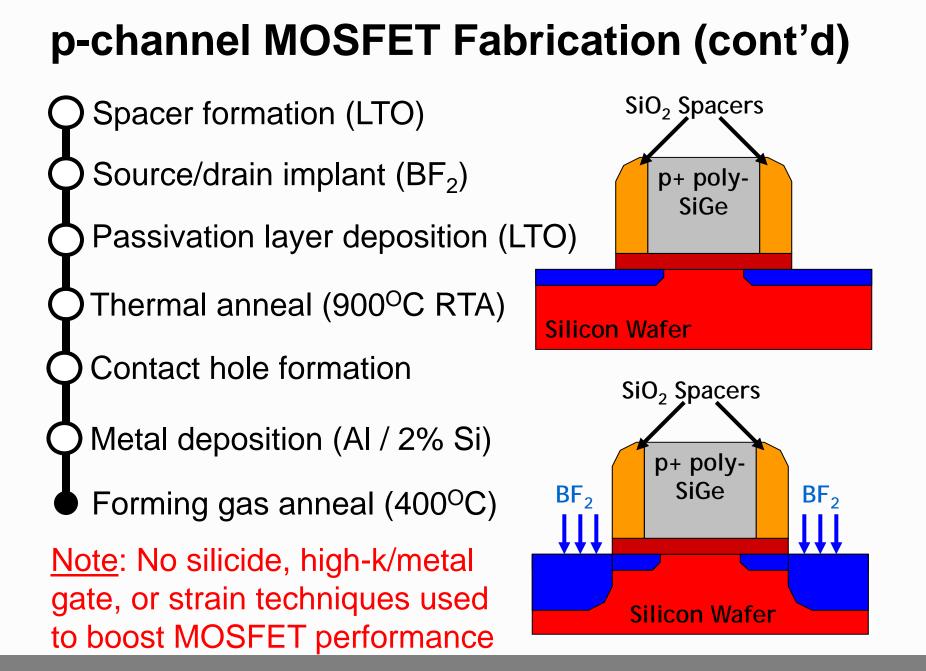

## **p-channel MOSFET Fabrication**

# Outline

- Introduction

- Why silicon-germanium (Si<sub>1-x</sub>Ge<sub>x</sub>) ?

- Segmented-channel MOSFET (SegFET) design

- Device Fabrication

- Corrugated substrate

- p-channel MOSFETs

- Results and Discussion

- Conclusion

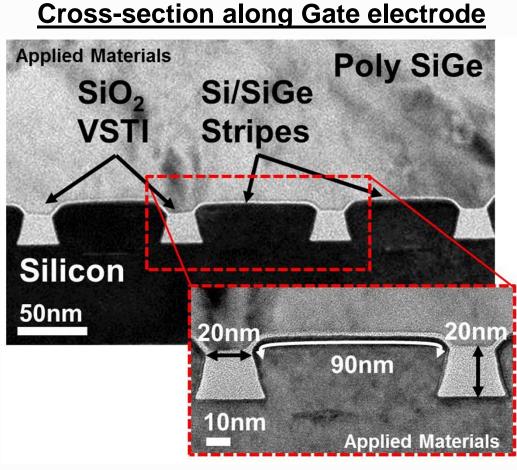

## **SegFET X-TEM Analysis**

- Stripe width ~ 80 nm

pitch = 100 nm

- Channel regions are elevated ~5 nm above VSTI

→ 90 nm effective channel width (W<sub>EFF</sub>) per stripe

→ 10% lower W<sub>EFF</sub> per unit layout width than non-segmented channel control device

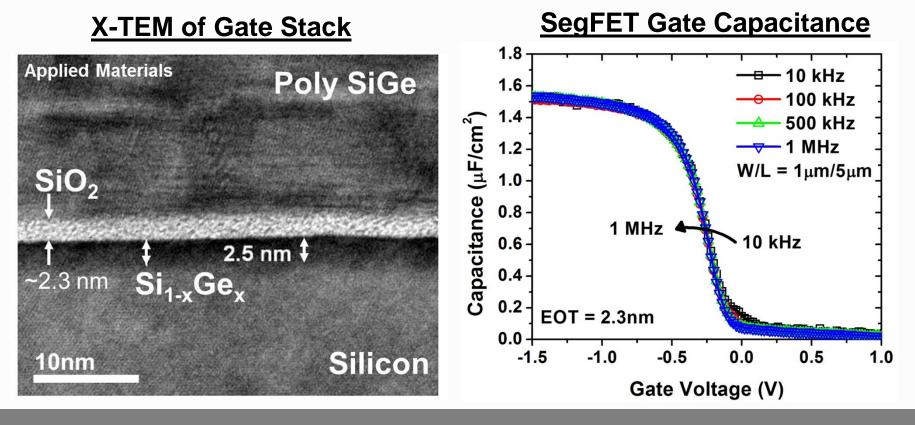

### **Gate Stack Characterization**

- Si<sub>1-x</sub>Ge<sub>x</sub> channel layer is ~2.5 nm thick.

→ Si cap layer was consumed during device fabrication.

- C-V indicates high-quality gate dielectric interface.

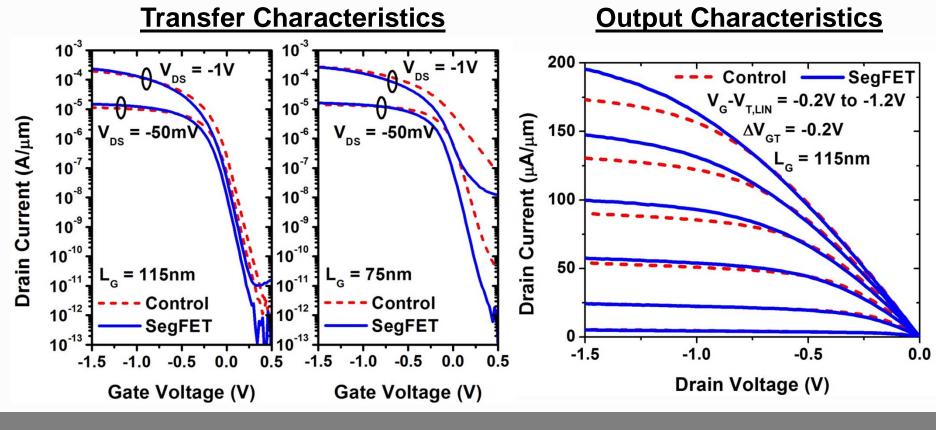

### **Measured Current per Unit Layout Width**

- SegFET has higher linear V<sub>T</sub> than control device.

possibly due to reduced biaxial (more uniaxial) strain

- SegFET has better layout area efficiency (same  $V_{GT}$ ).

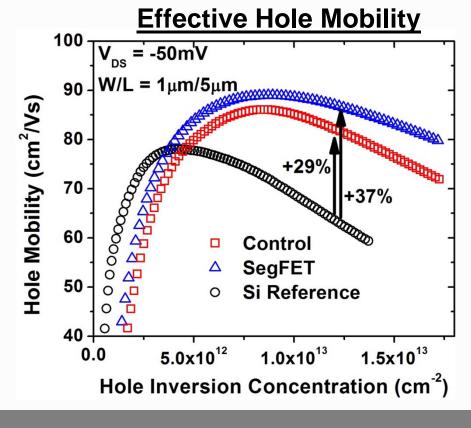

### **Transconductance and Mobility**

- Higher effective hole mobility is seen in the SegFET, especially at higher inversion charge concentration.

- due to different channel strain and lower transverse E-field

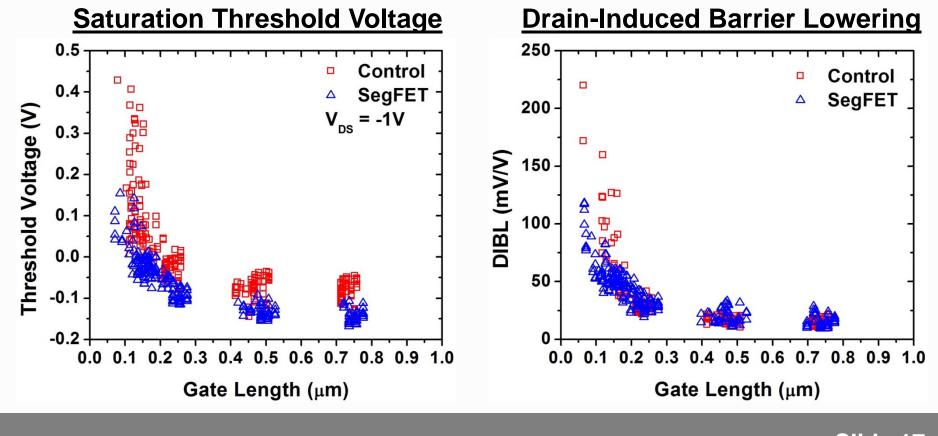

### **Comparison of Short-Channel Effects**

Short-channel effects are mitigated in SegFETs

...and can be better suppressed by recessing the VSTI oxide and/or reducing W<sub>STRIPE</sub> to improve gate control

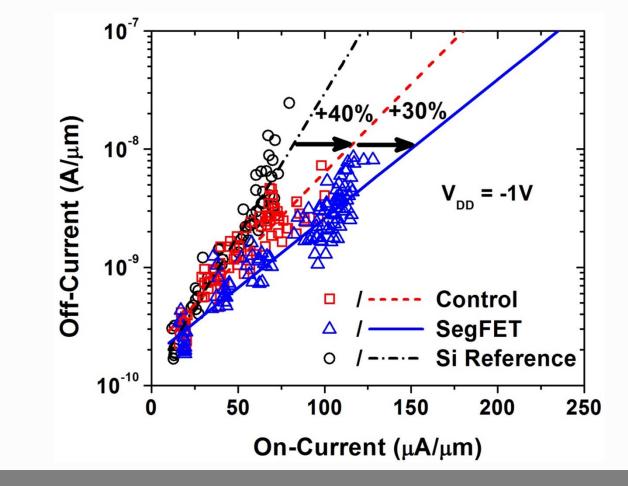

# I<sub>OFF</sub> vs. I<sub>ON</sub> (normalized to layout width)

- SegFETs achieve 30% higher  $I_{ON}$  ( $I_{OFF}$  = 10nA/um)

- higher hole mobility, lower  $R_{SD}$ , reduced short-channel effects

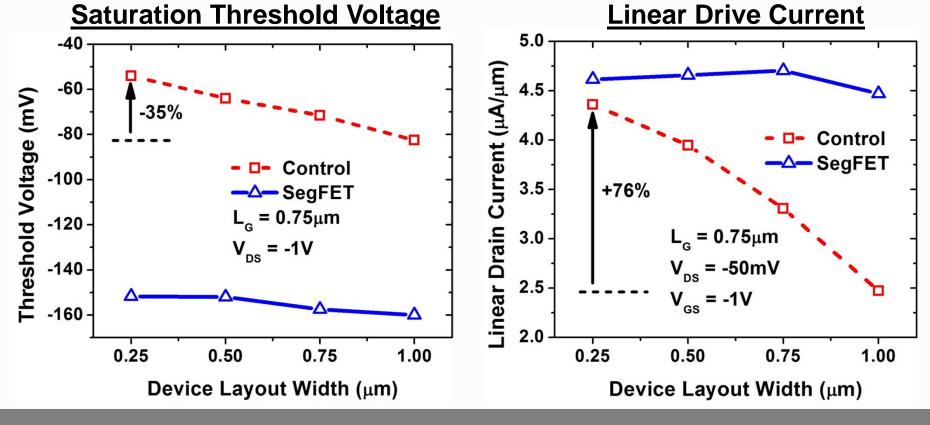

### Active Area Width (W) Dependence

- Change in W  $\rightarrow$  change in number of channel stripes – Each stripe has the same width (hence same V<sub>T</sub> & current)

- $\rightarrow$  Width dependence is dramatically lower for SegFET

# Outline

- Introduction

- Why silicon-germanium (Si<sub>1-x</sub>Ge<sub>x</sub>) ?

- Segmented-channel MOSFET (SegFET) design

- Device Fabrication

- Corrugated substrate

- p-channel MOSFETs

- Results and Discussion

- Conclusion

# Conclusion

- Corrugated substrate technology is advantageous for fabrication of Si<sub>1-x</sub>Ge<sub>x</sub>/Si pMOSFETs using a conventional process flow:

- ✓ Higher hole mobility

- ✓ Improved electrostatic control

- ✓ Dramatically reduced dependence on active area width

- $\rightarrow$ Higher performance and reduced variability

...facilitating continued scaling

### Acknowledgements

- Semiconductor Research Corporation

- GRC Graduate Fellowship

- Contract 2007-VJ-1631

- UC Berkeley Marvell Nanofabrication Laboratory