### Welcome to EECS 150: Components and Design Techniques for Digital Systems

#### Course staff

- Randy Katz (Instructor), Po-Kai Chen (Head TA)

- I Teaching Assistants: Bryan Brady, Jay Chen, Brian Gawalt, Jack Tzeng

- Readers: David Lin, Kevin Lin

- Course web

- inst.eecs.Berkeley.edu/~eecs150 (coming soon)

#### This week

- What is logic design?

- What is digital hardware?

- What will we be doing in this class?

- Quick Review

- I Class administration, overview of course web, and logistics

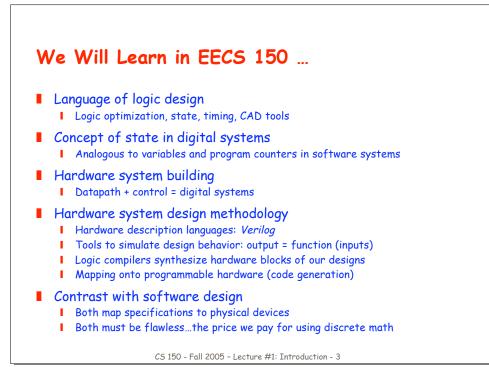

# CS 150: Concepts/Skills/Abilities

- Basics of logic design (concepts)

- Sound design methodologies (concepts)

- Modern specification methods (concepts)

- Familiarity with full set of CAD tools (skills)

- Appreciation for differences and similarities (abilities) in hardware and software design

<u>New ability</u>: perform logic design with computer-aided design tools, validating that design via simulation, and mapping its implementation into programmable logic devices; Appreciating the advantages/disadvantages hw vs. sw implementation

### Administrative Details

#### See course web page for gory details!

- MW 1-2:30 course lecture, F 2-3 lab lecture

- I 1x3 hour lab, 1x1=hour discussion per week

- No labs or discussions first week!

#### Grading

- Midterm Exams (28 Sep, 9 Nov): 20%

- Final Exam (16 Dec): 20%

- Labs (1-5): 15%

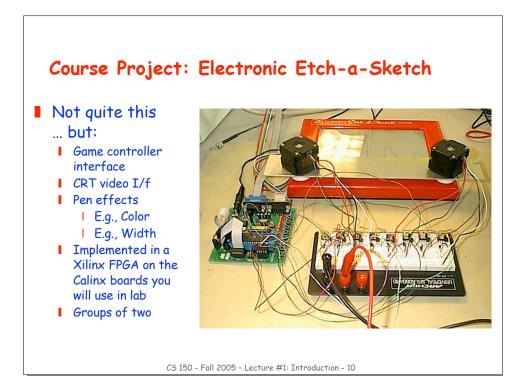

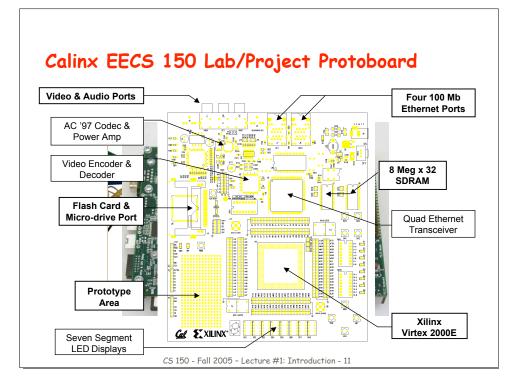

- Project (Etch-a-Sketch): 30%

- Homeworks (10 problem sets): 10%

- I In-class pop quizzes: 5%

- I First one NOW: Diagnostic Quiz (not graded!)

## Mapping Physical to Binary World

| Technology                                                                                                                                                                                          | State 0                                                                                                                                                                     | State 1                                                                                                                                                              |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Relay logic<br>CMOS logic<br>Transistor transistor logic (TTL<br>Fiber Optics<br>Dynamic RAM<br>Nonvolatile memory (erasable)<br>Programmable ROM<br>Bubble memory<br>Magnetic disk<br>Compact disc | Circuit Open<br>0.0-1.0 volts<br>) 0.0-0.8 volts<br>Light off<br>Discharged capacito<br>Trapped electrons<br>Fuse blown<br>No magnetic bubble<br>No flux reversal<br>No pit | Circuit Closed<br>2.0-3.0 volts<br>2.0-5.0 volts<br>Light on<br>r Charged capacitor<br>No trapped electrons<br>Fuse intact<br>Bubble present<br>Flux reversal<br>Pit |  |

| CS 150 - Fall 200                                                                                                                                                                                   | 5 - Lecture #1: Introduction - 2                                                                                                                                            | 1                                                                                                                                                                    |  |

## Implementation in Software integer number\_of\_days (month, leap\_year\_flag) { switch (month) { case 1: return (31); case 2: if (leap\_year\_flag == 1) then return (29) else return (28); case 3: return (31); case 12: return (31); default: return (0); } } }

CS 150 - Fall 2005 - Lecture #1: Introduction - 33

### Implementation in Software integer combination lock ( ) { integer v1, v2, v3; integer error = 0; static integer c[3] = 3, 4, 2;while (!new\_value( )); v1 = read value(); if (v1 != c[1]) then error = 1; while (!new\_value( )); v2 = read\_value(); if (v2 != c[2]) then error = 1; while (!new\_value( )); v3 = read value(); if (v2 != c[3]) then error = 1; if (error == 1) then return(0); else return (1); }

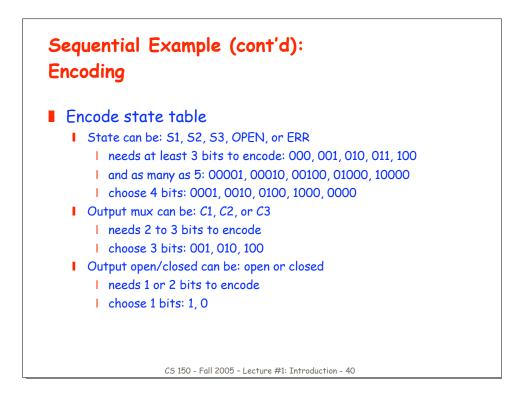

| Seque<br>Encod | ential<br>ding | Exc     | ample      | e (co        | ont'd         | l):     |            |                          |

|----------------|----------------|---------|------------|--------------|---------------|---------|------------|--------------------------|

| Enco           | de state       | e tabl  | e          |              |               |         |            |                          |

| 1.5            | tate can b     | ne: 51  | 52 53      | OPEN         | or FRR        |         |            |                          |

|                |                |         | : 0001, (  |              |               |         | 00         |                          |

|                |                |         |            |              |               | , 000   |            |                          |

|                | output mux     |         |            |              |               |         |            |                          |

|                |                |         | : 001, 0   |              |               |         |            |                          |

|                | output ope     | n/close | ed can b   | e: open      | or close      | ed      |            |                          |

|                | I Choose       | 1 bits  | 1, 0       |              |               |         |            |                          |

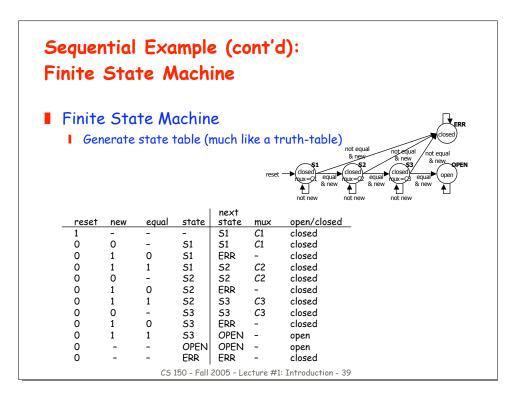

|                | reset          | new     | egual      | state        | next<br>state | mux     | onen/      | closed                   |

|                | 1              | -       | -          | -            | 0001          | 001     | 0          | closed                   |

|                | 0              | 0       | -          | 0001         | 0001          | 001     | ŏ          |                          |

|                | 0              | 1       | 0          | 0001         | 0000          | -       | Ō          | good choice of encoding! |

|                | 0              | 1       | 1          | 0001         | 0010          | 010     | 0          | geea energe en energe    |

|                | 0              | 0       | -          | 0010         | 0010          | 010     | 0          | mux is identical to      |

|                | 0              | 1       | 0          | 0010         | 0000          | -       | 0          | last 3 bits of state     |

|                | 0              | 1       | 1          | 0010         | 0100          | 100     | 0          |                          |

|                | 0              | 0       | -          | 0100         | 0100          | 100     | 0          | open/closed is           |

|                | 0              | 1       | 0          | 0100<br>0100 | 0000<br>1000  | -       | 0          | identical to first bit   |

|                | 0              | -       | -          | 1000         | 1000          | -       | 1          | of state                 |

|                | õ              | -       | -          | 0000         | 0000          | -       | ō          |                          |

|                |                | CS      | 150 - Fall | 2005 - 1     | ecture #1:    | Tntrodu | ction - 41 |                          |