#### Centrifuge: Evaluating full-system HLSgenerated heterogeneous-accelerator SoCs using FPGA-Acceleration

Qijing Huang, Christopher Yarp, Sagar Karandikar, Nathan Pemberton, Benjamin Brock, Liang Ma<sup>†</sup>, Guohao Dai<sup>‡</sup>, Robert Quitt, Krste Asanović, John Wawrzynek

> University of California, Berkeley <sup>†</sup>Politecnico di Torino <sup>‡</sup>Tsinghua University

#### 1. Motivation

#### 2. Centrifuge Design Flow

#### 3. Centrifuge Design Space

#### 4. Case Studies

#### Motivation

# What is a good methodology for designing SoCs with many accelerators?

High-Performance System Low NRE costs Short Time-to-market

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

• Profiling on existing systems

Hotspot detection is only valid for the current system

ISA-independent IR trace analysis

Lack of detailed information for hotspot detection

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

- Roofline Models

- Dynamic Data

Dependence Graphs

(DDDG) Analysis

Inaccurate

Lack of insights for architectural variations in real implementation

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification-

- 5. Chip Tapeout

- 6. Software Development

- A. Build Software Models for Hardware Components

- B. Gather Costs from RTL Synthesis

- C. Verify Functionality

#### **Engineering Intensive**

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

Missing co-optimization opportunities

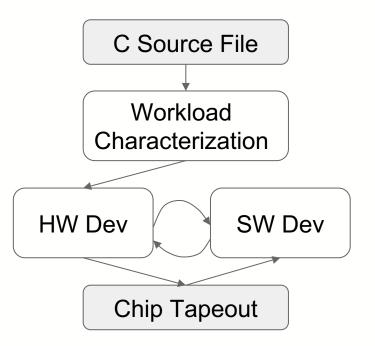

### **Current Design Flow Complexities**

- 1. Workload Characterization

- 2. Hardware Modeling and Verification

- 3. Software Integration

#### **Our Objectives**

- 1. Tradeoffs informed with full-system evaluation

- 2. Fast development and verification cycle for both HW/SW

- 3. Large design space for rapid algorithm-hardware exploration

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

#### **Proposal 1: Native Simulation**

Run full-stack software with target SoC simulation

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

#### **Proposal 1: Native Simulation**

Run full-stack software with target SoC simulation

#### Proposal 2: Rapid Prototyping

- 1. Workload Characterization

- 2. Accelerator Modeling

- Analytical

- Transaction-based

- 3. RTL Development

- 4. Emulation and Verification

- 5. Chip Tapeout

- 6. Software Development

#### **Proposal 1: Native Simulation**

Run full-stack software with target SoC simulation

Proposal 2: Rapid Prototyping

Combine 2 and 3 with one highlevel abstraction

Proposal 3: Agile Development

Improve software stack concurrently with hardware development

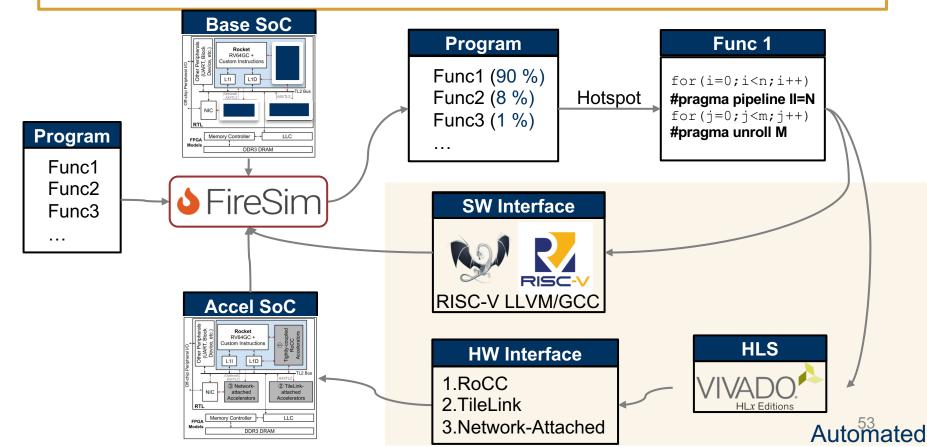

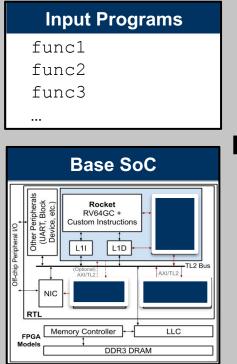

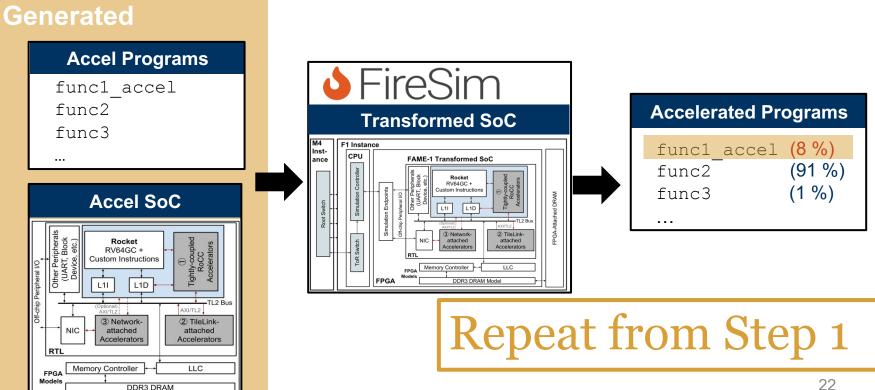

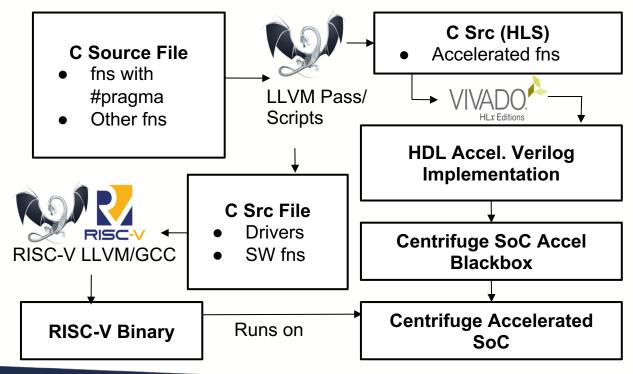

# **Centrifuge** Accelerator Design Flow

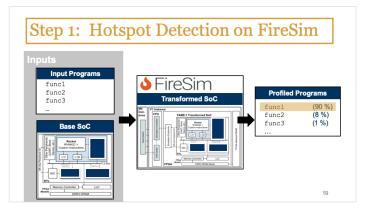

- 1. Hotspot Detection on Native System Simulation

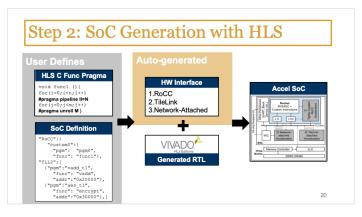

- 2. Fast Accelerator SoC Generation with HLS

- 3. Auto Generation of SW Communication Primitives

- 4. Continue HW and SW Development

- 5. Chip Tapeout

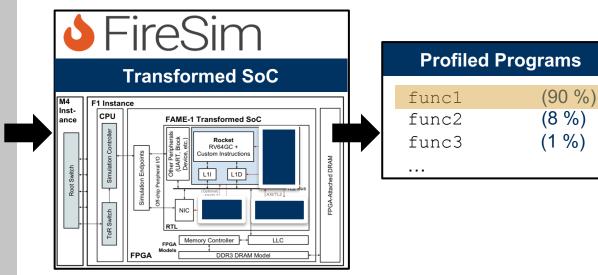

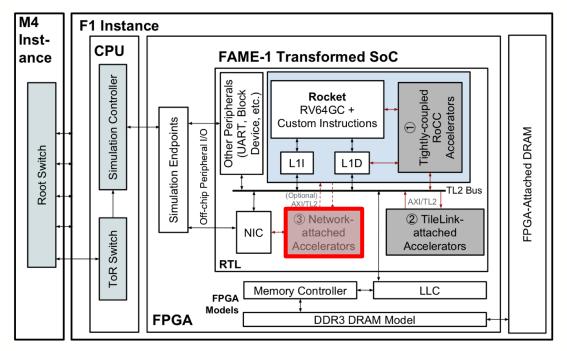

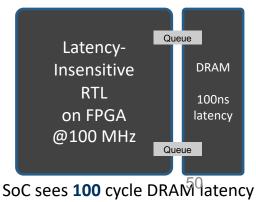

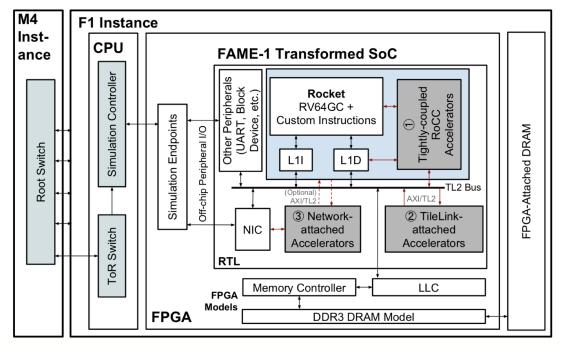

# Background: FireSim

**FireSim** is an open-source, FPGA-accelerated, cycle-exact, scalable hardware simulator:

- Ingests:

- RTL Design (e.g. Rocket Chip, BOOM, NVDLA)

- HW and/or SW IO Models (e.g. UART, Ethernet, DRAM)

- Workload Descriptions

- $\circ$  **Produces:**

- FPGA-accelerated Simulation (Not FPGA prototype)

- Deployment on Cloud FPGAs

# Background: High-level Synthesis

**High-level Synthesis (HLS)** raises the level abstraction for hardware design and verification:

- Ingests:

- High-level Algorithmic Description in C/C++/SystemC

- Produces:

- Hardware RTL, C and RTL Verification Models

- Commercial Tools:

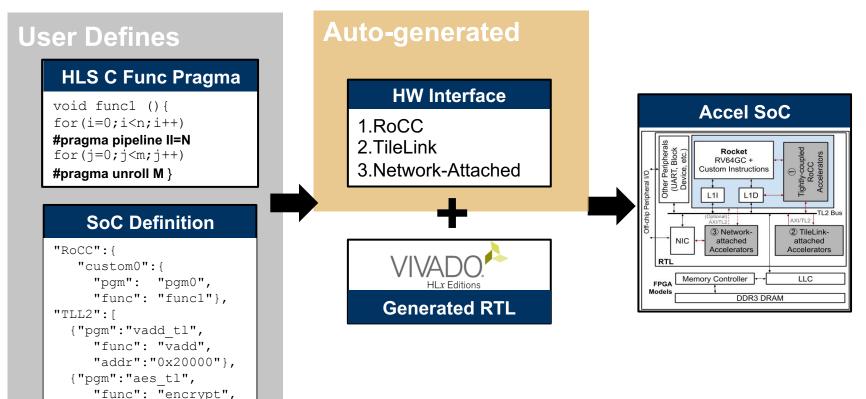

### **Centrifuge Design Flow**

**Centrifuge** is a unified accelerator design flow that generates the interfaces and design automation scripts that leverages existing tools:

- Injects:

- High-level Algorithmic Description in C/C++

- Accelerator Configuration

- Produces:

- Full Functional Accelerator SoC

- Corresponding Software Stack

- Tooling Scripts

### **Centrifuge Design Flow**

**Centrifuge** provides the user with:

- 1. Full-system evaluation of the target workload

- 2. Fast development and verification cycle for both HW/SW

- 3. Large design space for rapid algorithm-hardware exploration

- A. Hardware Integration

- B. Architectural Design Variation

- C. Software Integration

### **Centrifuge Tool Flow**

### Step 1: Hotspot Detection on FireSim

#### Inputs

#### Step 2: SoC Generation with HLS

"addr":"0x30000"},]

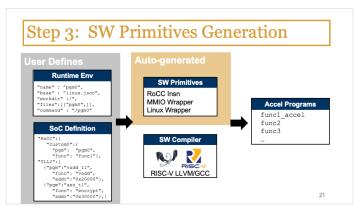

#### **Step 3: SW Primitives Generation**

#### **User Defines**

#### **Runtime Env**

"name" : "pgm0",

"base" : "linux.json",

"workdir" :/",

"files":[["pgm0",]],

"command" : "/pgm0"

#### **SoC Definition**

"RoCC":{

"custom0":{

"pgm": "pgm0",

"func": "func1"},

"TLL2":[

{"pgm":"vadd\_t1",

"func": "vadd",

"addr":"0x20000"},

{"pgm":"aes\_t1",

"func": "encrypt",

"addr":"0x30000"},]

#### **Auto-generated**

#### **SW Primitives**

RoCC Insn MMIO Wrapper Linux Wrapper

| Accel Programs                |

|-------------------------------|

| func1_accel<br>func2<br>func3 |

|                               |

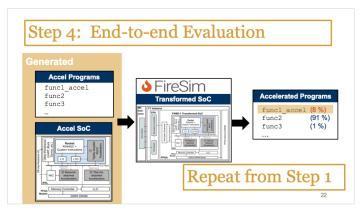

### Step 4: End-to-end Evaluation

- 1. Hardware Integration

- 2. Accelerator Design Variation

- 3. Software Integration

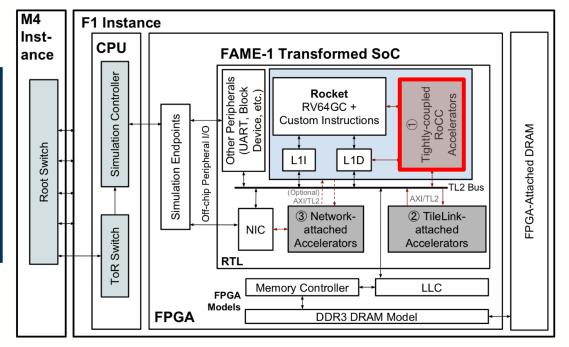

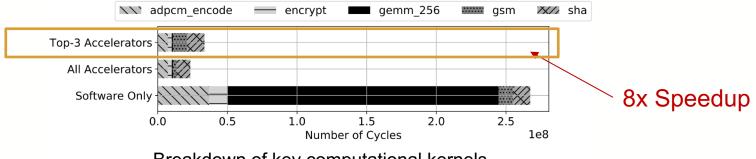

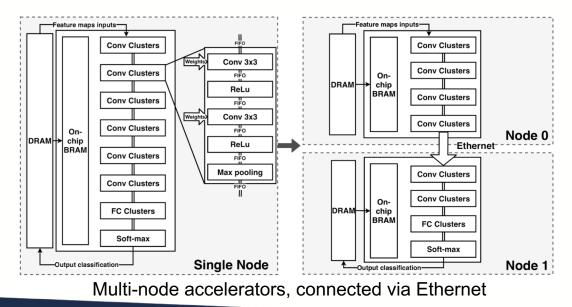

#### **RoCC Coprocessors**

- Invoked by RoCC instruction

- Sharing L1 and LLC with the CPU

- Sharing TLB with the CPU

- 1. Hardware Integration

- 2. Accelerator Design Variation

- 3. Software Integration

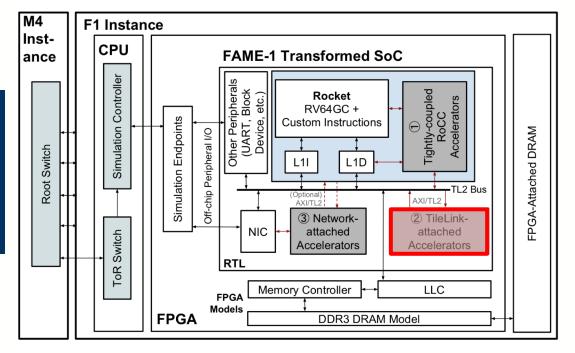

#### **TileLink Accelerators**

Invoked by RoCC instruction or MMIO

Sharing LLC with the CPU

• Physically-addressed

- 1. Hardware Integration

- 2. Accelerator Design Variation

- 3. Software Integration

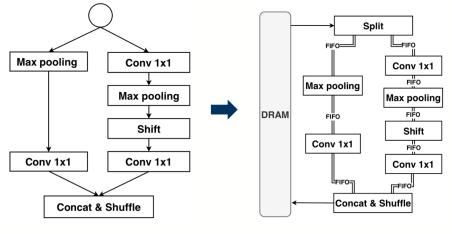

#### Network-attached Accelerators

- Same as TileLink Accelerators

- With Direct Access to the Ethernet

#### Network-Attached Accelerator

1. User includes the Centrifuge Ethernet streaming interfaces and packet parser functions in the HLS code

Centrifuge Ethernet Interfaces:

hls::stream<ap\_uint<128> >& resp\_head, hls::stream<ap\_uint<65> >& resp\_data, hls::stream<ap\_uint<128> >& req\_head, hls::stream<ap\_uint<65> >& req\_data, ap\_uint<64>srcmac, ap\_uint<64>dstmac

2. Centrifuge generates the interconnect between the accelerator and the Ethernet

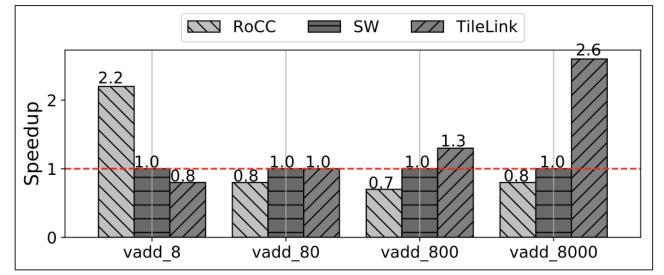

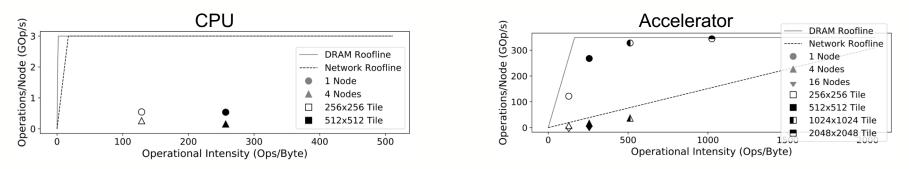

#### Hardware Integration DSE

Different Coupling for vadd Accelerator

Three factors:1. Cache Size2. Cache Latency3. Interface

Bandwidth

Determine the best hardware integration strategy

- 1. Hardware Integration

- 2. Accelerator Design Variation

- 3. Software Integration

- 1. Hardware Integration

- 2. Accelerator Design Variation

- 3. Software Integration

#### A. Loop Unrolling Factors

- B. Loop Pipelining Factors

- C. Memory Size and Parallel Ports

- D. Resource Binding

- 1. Hardware Integration

- 2. Accelerator Design Variation

- 3. Software Integration

A. Bare-metalB. Linux

#### Linux Wrapper Generation

- Allocates contiguous physical addresses

- Virtual to physical address lookup

- Map MMIO registers to the user space

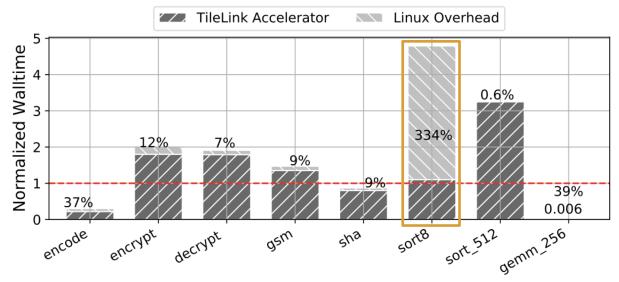

#### **Software Integration DSE**

Tilelink Accelerators with Linux Driver

- In most cases, the Linux overhead is not significant

- RoCC-level integration might be better option for sort8

Determine whether the functions can be accelerated under Linux

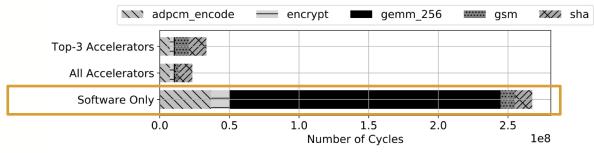

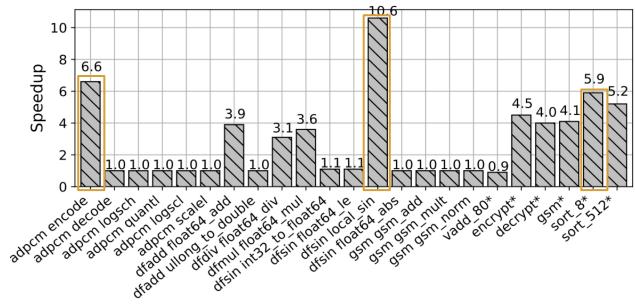

#### Case Study 1: Smart-House Hub

• Application: A smart-house assistant

Breakdown of key computational kernels

1. Apply Amdahl's law in hotspot detection

#### **Acceleration Region DSE**

**RoCC Accelerators Speedup Compared to Software**

2. Determine whether the functions can be accelerated with HW

#### Case Study 1: Smart-House Hub

• Application: A smart-house assistant

Breakdown of key computational kernels

#### **Other Case Studies**

#### Case Study 2: Distributed GEMM Accelerator

- 1. Running Full-stack Linux with MPI

- 2. Distributed on 16 nodes

#### Case Study 3: Deep Learning Accelerators

- 1. Different Hardware Utilization

- 2. Network-attached Accelerators

#### Conclusion

We present a methodology and flow, *Centrifuge*, that can rapidly generate and evaluate heterogeneous SoCs by combining an HLS toolchain with the open-source FireSim FPGA-accelerated simulation platform

Access to code: <u>https://github.com/hqjenny/centrifuge</u> Email: <u>qijing.huang@berkeley.edu</u>

FireSim: https://fires.im

# **Backup Slides**

#### **RoCC Coprocessor Integration**

ap\_bus to RoCC Decoupled Interface

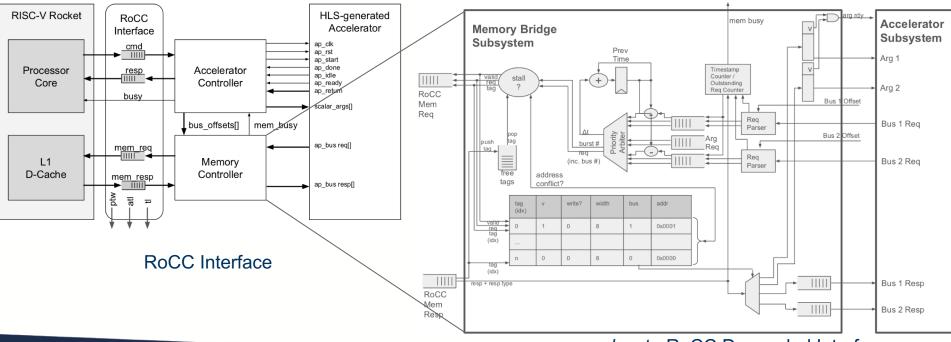

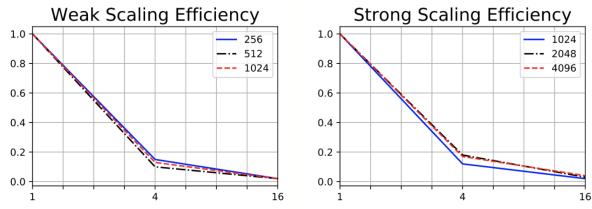

### Case Study 2: Distributed GEMM

#### **Roofline Models**

- Application: MPI-based Distributed Matrix Multiplication (DGEMM)

- Tools: STREAM and iperf are used to generate the rooflines

- Observation: With the GEMM accelerators, the distributed workload becomes more bandwidth-bound

#### Case Study 2: Distributed GEMM

- Experiments on 1, 4, 16 nodes

- 2.0 GB/s measured DRAM bandwidth

- 1.2 Gbit/s measured network bandwidth

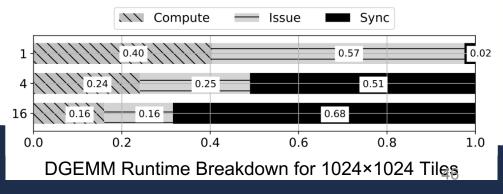

## Case Study 3: Deep Learning

1. HW Utilization for Different Layer Sizes

| vorkioad Size | Total Ops                     | Ops/cycle                                                                            |

|---------------|-------------------------------|--------------------------------------------------------------------------------------|

| 2×16          | 196608                        | 4.55                                                                                 |

| $2 \times 32$ | 786432                        | 15.12                                                                                |

| 2×64          | 3145728                       | 20.59                                                                                |

| 6×128         | 3145728                       | 21.35                                                                                |

| S×64          | 196608                        | 17.09                                                                                |

|               | 2×16<br>2×32<br>2×64<br>6×128 | 2×16     196608       2×32     786432       2×64     3145728       6×128     3145728 |

Total One

Wantsland Cine

#### Ops/Cycle for Different Workload Sizes

**DNN Building Block**

Spatial HW Design

Oncloude

## Case Study 3: Deep Learning

2. Distributed Accelerators

#### **Detailed Tool Flow**

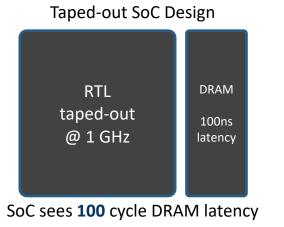

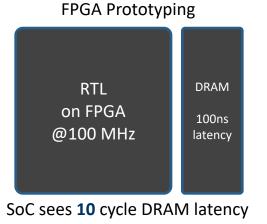

#### FireSim

**FireSim** is an open-source, FPGA-accelerated, cycleexact, scalable **hardware simulator**

- Produces:

- FPGA-accelerated Simulation (Not FPGA prototype)

- Deployment on Cloud FPGAs

#### FPGA-accelerated Simulation

## **Accelerator Coupling**

- RoCC

Coprocessors

TileLink

Accelerators

- 3. Network-attached Accelerators

#### New Applications to Accelerate

- Packet Processing

- Video/Audio Compression/Decompression

- DNN Acceleration

- Graph Acceleration

- Database Systems

### **Centrifuge Tool Flow**