1.

EECS140 Final

Fall 2019

Name Good Luck, Have Fun!

SID top secret

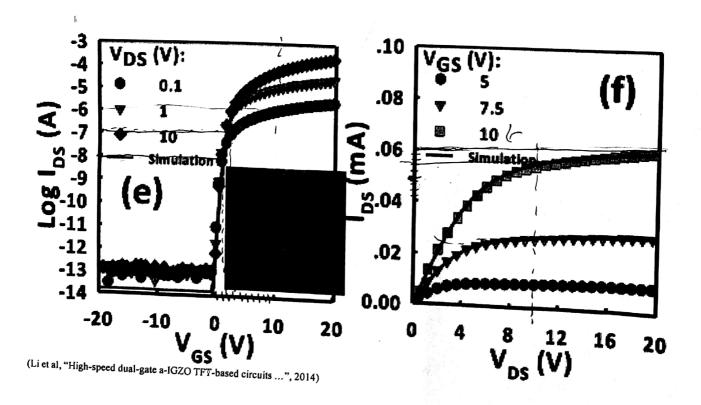

[8] The I-V curves below are from an Indium Gallium Zinc Oxide transistor

used in flat panel display TVs.

a. Estimate  $g_m$  when  $V_{GS}$ = 10V and  $V_{DS}$ = 10V. Write down what  $\Delta I$  and  $\Delta V$ you are using for your calculation.

b. Estimate  $g_0=1/r_0$  under the same conditions. Draw the line that you are using to estimate go. Say slope & 001mA~ 0.001 290

c. Calculate the intrinsic gain from parts a and b d. If  $I_{DS}=10$ nA when  $V_{GS}=2V$ , estimate the sub-threshold slope.

OV2 -13 50 / 5 decades/2V 2

| Prob.                                                                       | Score  |    |

|-----------------------------------------------------------------------------|--------|----|

| String out with anisked a contract right, the group against a status to the | 179    |    |

| 2,3                                                                         | /20    |    |

| 4                                                                           | /16    |    |

| 5                                                                           | /16    |    |

| 6                                                                           | /21_   | 21 |

| 7                                                                           | /8     |    |

| 8                                                                           | /15    |    |

| 9                                                                           | /14    |    |

| 10                                                                          | /10    |    |

| 11                                                                          | /15    |    |

| 12                                                                          | /22    |    |

| Total                                                                       | , /165 | _  |

|                                                                             | ( ==   |    |

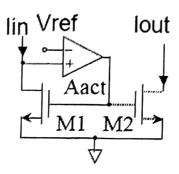

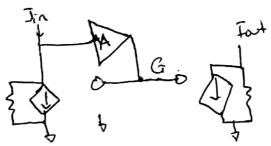

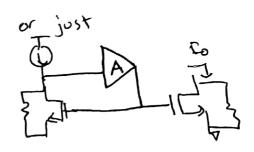

- [10] For the current mirror shown here,

- a. Draw the small signal model of the circuit, assuming that the amplifier is an ideal op-amp with a large positive gain A, and that V<sub>ref</sub> is a constant voltage.

b. What is the minimum value of Vref for which transistor M1 will remain in saturation? If we compare this circuit to a typical simple current mirror, which has a lower minimum input voltage? Why?

Weef TVOV, which is lover then the simple mirror.

c. Write an expression for the small-signal input impedance of the current mirror. How does that compare

Ro = roy nothing new here

[10] You are designing a single-stage CMOS op-amp to be used in feedback to achieve a gain of 5. The gain must be accurate to 1% from DC to 1 Mrad/s (including any 3dB losses). The load is a 10pF capacitor. You are restricted to biasing your transistors with overdrives between 100mV and 1V, and they look reasonably quadratic in that range. f = 1/5a. What is the minimum open-loop gain and dominant pole location of the op-amp?

b. What is the minimum unity gain frequency of the op-amp?

- $Wu = GBW = 500 \cdot \text{Moreoff} = 9 \text{ [500 M rad/s]}$ 2 c. What is the minimum transconductance of the input transistors?  $9m = 10^{-3} \text{ S. 5}$  $\mathcal V$  d. What is the minimum current in each of the input transistors?

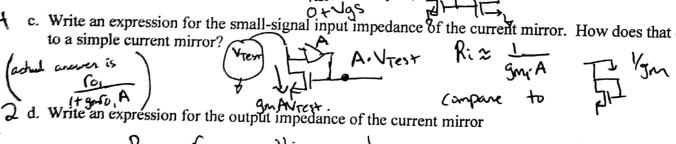

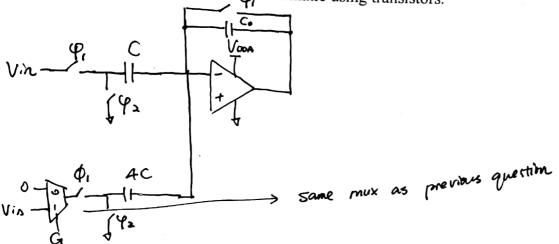

[16] For the figure below you may assume that the switches and op-amp are ideal.  $\phi_1$  and  $\phi_2$  are nonoverlapping clocks. Assume all of your capacitors are initially discharged.

a. After the first round of  $\phi_1$  and  $\phi_2$  (we'll call it cycle 0), what is the charge,  $Q_F[0]$ , on the right side of

in terms of that cycle's input,

$$V_{IN}[0]$$

?

$\gamma$  b. What is the corresponding voltage,  $V_{OUT}[0]$ ?

$$Vout[0] = \frac{Cs}{CF} V_{IM}[0] = \frac{QF[0]}{CF}$$

$\nu$ c. Now the input voltage has changed to  $V_{IN}[1]$ . What is the charge  $Q_F[1]$  on the right side of  $C_F$  after the next cycle in terms of  $Q_F[0]$  and  $V_{IN}[1]$ ?

$$Q_{S}[i] = Q_{S}[i] + Q_{S}[i] \longrightarrow Q_{F}[i] = Q_{F}[0] - Q_{S}[i]$$

$$Q_{X}[i] = Q_{X}[i] + Q_{S}[i] \longrightarrow Q_{F}[i] = Q_{F}[0] + C_{S}V_{IM}[i]$$

$$V_{CF}[i] = Q_{X}[i] + Q_{S}[i] \longrightarrow Q_{F}[i] = Q_{F}[i] + C_{S}V_{IM}[i]$$

$$V_{CF}[i] = Q_{F}[i] = Q_{F}[i] = Q_{F}[i] + Q_{S}[i]$$

$$V_{CF}[i] = Q_{F}[i] = Q_{F}[i] + Q_{S}[i]$$

$$Q_{F}[i] = Q_{F}[i] + Q_{S}[i]$$

**v**e. What do we call this kind of circuit?

Same circuit, different types of questions:

$^{\bullet}$ f. During  $\phi_2$  what is the feedback factor for the amplifier?

$\nu$  g. During  $\phi_2$  what is the total capacitance at the output of the amplifier?

${m \nu}$  h. If there is parasitic capacitance Cp on node V-, does that change the feedback factor during  $\phi_2$  , and if s

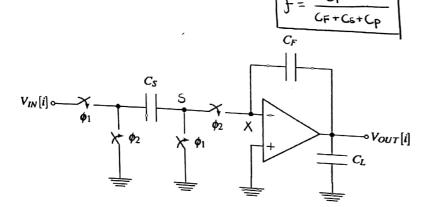

- [24] For the figure below, Vtn=-Vtp=1V. The overdrive voltage on M5 and M7 is 100 mV. You may ignore body effect, and assume that the devices all look quadratic.

- a. Assuming lambda=0, estimate the currents in on the transistors in the table below

- b. Assuming lambda=0, estimate the bias voltages on the gates of the transistors in the table below The square root of 20 is approximately 4.5

|         | M1     | M3     | M5    | M7    | M9     | MII   | M16   | M17   |

|---------|--------|--------|-------|-------|--------|-------|-------|-------|

|         | Au col | 200 uA | 200uA | 200uA | 200 แA | Aucel | 10044 | 20044 |

| $V_{G}$ | 3V     | 3.9√   | 3.97  | 1.17  | 1.17   | 1.457 | 3.9V  | 3.651 |

c. Estimate the input common mode range (give a voltage for each)

$V_{icm, min} =$   $\sim 0.65$

$V_{icm, max} =$ 3.8V

d. Estimate the output swing for which all transistors will remain in saturation

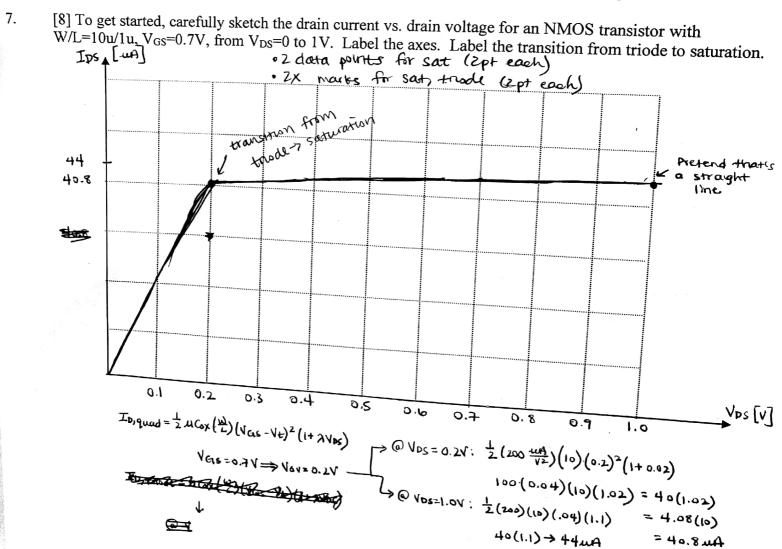

For the following problems related to the project, you will be working in a CMOS process with  $\mu_n C_{ox} = 200 \text{uA/V}^2$ ,  $\mu_p C_{ox} = 100 \text{uA/V}^2$ ,  $V_{tn} = -V_{tp} = 0.5 \text{V}$  and  $\lambda = 1/(10 \text{V}) (1 \text{um/L})$  with  $W_{min} = L_{min} = 1 \text{um}$ . Note that this is NOT the same process as you used for your project this semester.

The supply is 2 alkaline cells, so  $V_{bat} = 1.6..3.2V$

You will design parts of the following analog blocks

- A low voltage bandgap reference

- an analog regulator with an output of 1.25 V

- an ADC reference voltage of 1V

- a digital regulator with an output of 1.5 V

- a 2-input analog multplexor with a single control bit

- a programmable gain amplifier with one gain select bit, and a gain of either 1 or 5

- a 10 bit switched capacitor ADC. The ADC has an input range from 0-1V. This is less than  $V_{\text{DDA}}$ .

op-amp topologies for parts "b" below: N or P input; 5 transistor, current mirror, 2 stage, folded cascode

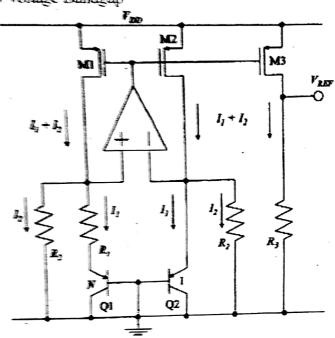

Low-voltage Bandgap

For the above circuit, assume that the op-amp is high gain and the transistors are identical with high output impedance

a) Explain why (prove) the three currents labeled "I1+I2" must be equal, why the two currents labeled I2 must be equal and why the two currents labeled I1 must be equal.

c) Write expressions for I<sub>1</sub> and I<sub>2</sub> in terms of V<sub>eb2</sub> (the right diode voltage), V<sub>th</sub> (thermal voltage), R1, N, and R2.

d) For I1 and I2, which one is PTAT, which one has a negative temperature coefficient?

E) Put it all together: Find the equation for

$$V_{ref}$$

!

Vel =  $(T_1 + T_2)R3 = \frac{R_3}{R_2} \left( Veb_2 + \left( \frac{R_2}{R_1} \right) | n N \cdot V_{R_1} \right)$

The Roughly what should the ratio between  $R_1$  and  $R_2$  be to get zero temperature come as an integer times the other. If  $\lambda = 0$  and  $\lambda = 0$  the same reference of the same reference of  $\lambda = 0$ .

Roughly what should the ratio between  $R_1$  and  $R_2$  be to get zero temperature coefficient on  $V_{ref}$ ? Write one as an integer times the other. If  $V_{ref} \approx -2mV/k$ ,  $V_{ref} \approx 0.08 \text{ sm}/k$

- 2 2) Roughly what should the ratio between R2 and R3 be to get Vref=0.6 V? Write one as an integer times Bandyap = 1.2V.

- $R_3 = \frac{1}{2}R_2$  or  $\frac{R_3}{R_1} = \frac{1}{2}$ 16) Give the minimum required supply voltage for this circuit if the mirror transistors have a Vov of 200mV

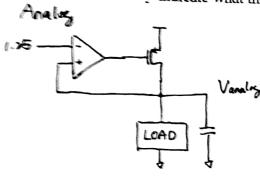

Regulators. You decide not to use the fancy low-voltage bandgap, and go back to a traditional one.

± [9] draw the schematic for the analog regulator (1.25V), digital regulator (1.5V), and ADC reference regulator (1V) using op-amp symbols, assuming that the bandgap is producing  $V_{BG}$ =1.25V. If you use resistors, clearly indicate what their ratios should be.

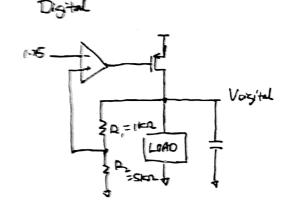

Voigital ·

$$\frac{R_2}{R_1 + R_2} = 1.25$$

(1.5)

$$R_1 = R_2 = 1.5$$

- b. [5] for the digital regulator op-amp:

- i. what is the common mode input?

ii. what is the output swing needed?

iii. what is the voltage supply?

- iv. which topologies will NOT work, and why?

- · Plues input will not work

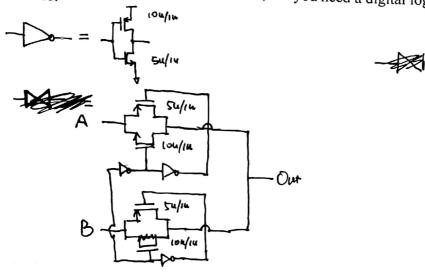

## Gain of 1 or 5 PGA

a. [10] draw the schematic using an op-amp symbol, transistors, and capacitors. Assume that the gain control bit G and two non-overlapping clock phases φ1 and φ2 are in the analog power domain (0, VDDA).

If you need a digital gate, draw the schematic using transistors.

- b. [5] for the op-amp:

- i. what is the common mode input?

٥V

- ii. what is the output swing needed?

- iii. what is the voltage supply

## VODA

- iv. which topologies will NOT work, and why?

- 1) News input not work

- 2) 5T

- 3) without a output stages

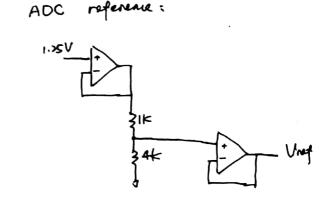

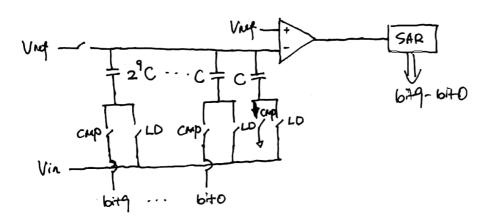

ADC. Vin=0 to 1V. The reference voltage is 1V. The analog supply is 1.25 V.

a. [10] draw a schematic of the ADC using an op-amp symbol for the comparator, and transistors and capacitors. Don't draw anything for bits 1 through 8, but do draw bits 0 and 9. Assume that there is a 10 bit digital SAR controller supplied to you.

b. [2] if the unit capacitance is 2 fF, what is the total input capacitance of the ADC?

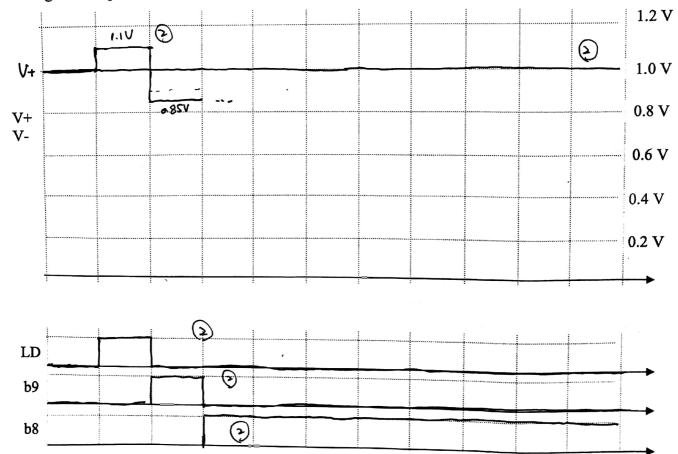

c. [10] sketch the waveforms for the first two bit decisions (b9 and b8) for an input of 0.4V. Specifically, sketch LD, b9 and b8 on the lower axes, and both V+ and V- of the comparator on the upper axes. Clock edges correspond to the vertical dotted lines. LD goes high on the second rising edge.

2-input MUX. Inputs will be between 0 and 1V (not 0 and  $V_{DDA}$ )

a. [4] draw the schematic of the transistor implementation. Label W/L values. Assume that the control bit is in the analog power domain (0, VDDA). If you need a digital logic cell, draw the transistors

b. [2] estimate the MUX "on" resistance for an input near 0V (I want an answer in Ohms, not a formula)

$|2_{\text{on}}| = \frac{1}{\mu \text{Con} \, \frac{W}{V} (\text{Vood-Vin})} = \frac{1}{2^{\text{od}} \, \mu \times 5 \times \text{o-75V}} = \frac{6}{3} \text{k} \approx 1.3 \text{ks}$

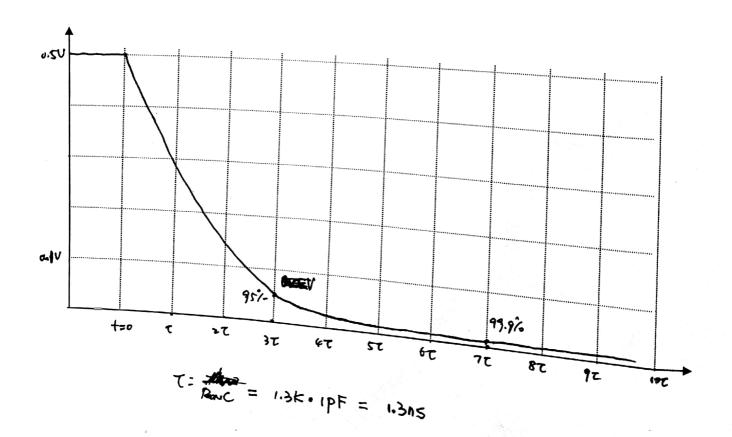

c. [4] The MUX, with one input at 0V and one input at 0.5V, is driving a 1pF capacitor. Carefully sketch the voltage waveform when the input to the MUX select switches from the 0.5V input to the 0V input. Label the axes. Label the times when the settling accuracy is at 95%, and 99.9%