## EECS140 Midterm 2 Spring 2017

| Name | Key |  |

|------|-----|--|

| arp  | (   |  |

| SID  |     |  |

| Score |

|-------|

| /10   |

| /25   |

| /30   |

| /15   |

| /80   |

|       |

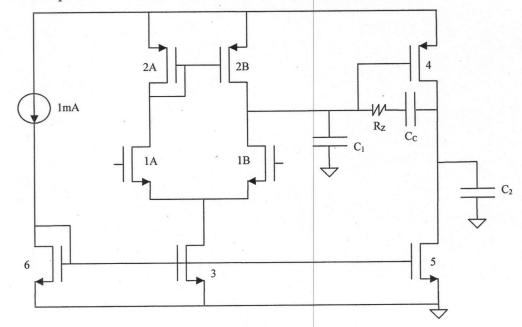

- 1) Unless otherwise indicated, you may make the following assumptions:

- All transistors are biased in saturation with  $V_{ov}^{\parallel}=0.2V$

- $V_{DD}=3V, V_{tn}=1V, V_{tp}=-1V$

- M3, and M6 are identical, M5 is 10 times wider

- All capacitors are assumed to be zero except  $C_C$ ,  $C_1$ , and  $C_2$ .

What is the common mode input range (min and max)?

b. What is the output swing (min and max)?

c. If  $C_1=0$ ,  $C_2=1$  pF, and  $C_c=1$  pF, what is the positive slew rate?

b. What is the output swing (min and max)?

$$+l \min_{c} = 0.2 \text{ V} \quad \text{max} = 2.8 \text{ V} + l$$

c. If  $C_1=0$ ,  $C_2=1$  pF, and  $C_c=1$  pF, what is the positive slew rate?

$$C_c = l \cdot 0^9 \text{ V/s}$$

d. If  $C_1=0$ ,  $C_2=2$  pF, and  $C_c=1$  pF, what is the negative slew rate?

$$C_c = l \cdot 0^9 \text{ V/s}$$

e. If  $C_1=0$ ,  $C_2=1,000$  pF, and  $C_c=1$  pF, what is the negative slew rate?

$$C_c = l \cdot 0^9 \text{ V/s}$$

e. If  $C_1=0$ ,  $C_2=1,000$  pF, and  $C_c=1$  pF, what is the negative slew rate?

A different amplifier with the same topology has the following parameters. You may

| ignore the pole/zero doublet from the mirror. | ignore the | pole/zero | doublet fi | rom | the mirror. |

|-----------------------------------------------|------------|-----------|------------|-----|-------------|

|-----------------------------------------------|------------|-----------|------------|-----|-------------|

| g <sub>m1,2</sub> | R <sub>o1</sub> | g <sub>m4</sub> | R <sub>o2</sub> | $C_1$ | $C_{\rm C}$ | C <sub>2</sub> |

|-------------------|-----------------|-----------------|-----------------|-------|-------------|----------------|

| 1mS               | 1M              | 1mS             | 100k            | 10p   | 1p          | 100p           |

f. If Cc=0 (magically we will assume no Cgd4 for this part only), what are the uncompensated poles?

On the following pages,

g. what is the location of the RHZ zero?

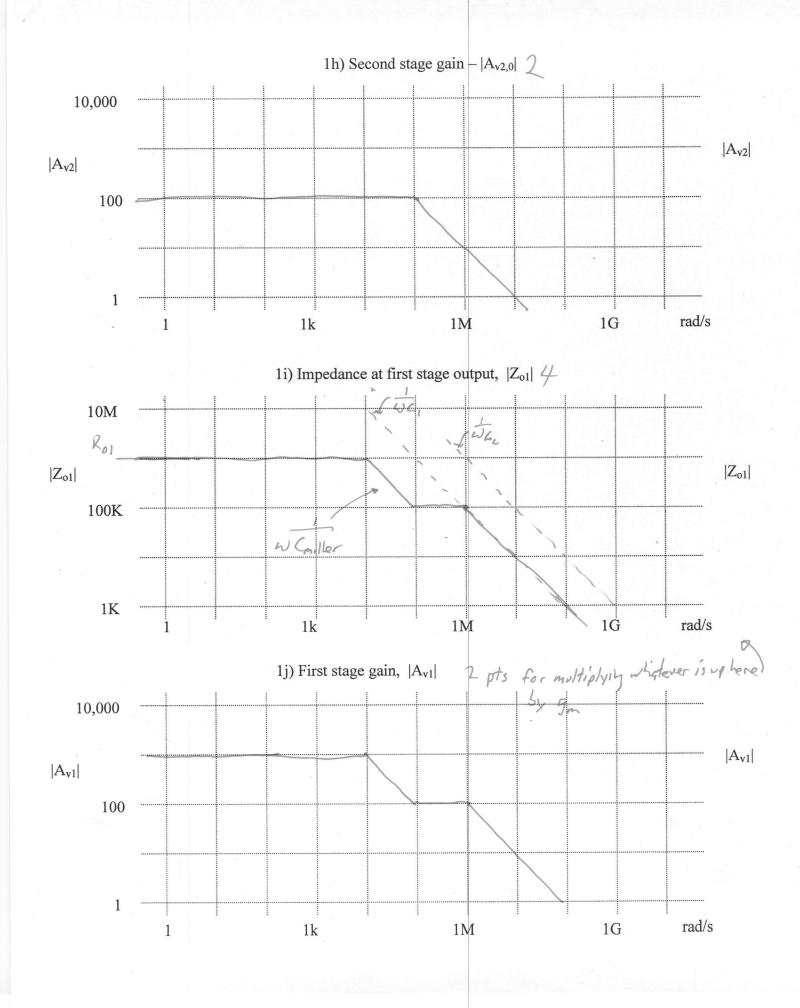

h. plot the magnitude of the second stage gain

i. plot the overall impedance seen at the first stage output (including R<sub>o1</sub>, C<sub>1</sub>, C<sub>C</sub>, and any effects of Miller multiplication),

j. plot the magnitude of the first stage gain,

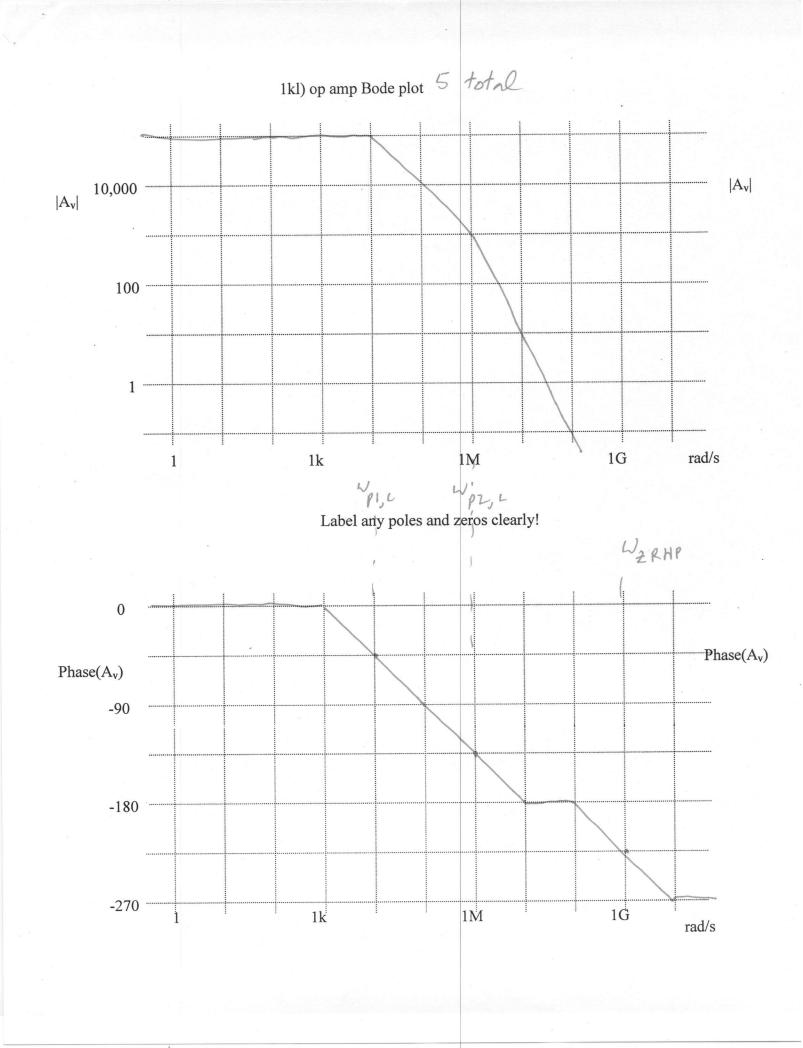

k. plot the magnitude and phase of the overall gain. Label any poles and zeros clearly.

1. Estimate the phase margin for this value of C<sub>C</sub>.

m. What is the maximum feedback factor and closed loop gain for which the amplifier has a 45 degree phase margin?

$$f = 10^{-3}$$

$A_{cl} = 10^{3}$

| 2)<br>fee<br>a. | [8] A single-pole amplifier has a gain of 1,000 and a pole at 1MHz. It is used in edback with a feedback factor f=0.01.  What is the approximate closed-loop gain, |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b.              | percent gain error, $\frac{1}{AF} \times 100\% = -10\% + 1$                                                                                                        |

| c.              | closed-loop pole location, for = 6BWACL = 10 MHZ+                                                                                                                  |

| d.              | and time constant of the step response?                                                                                                                            |

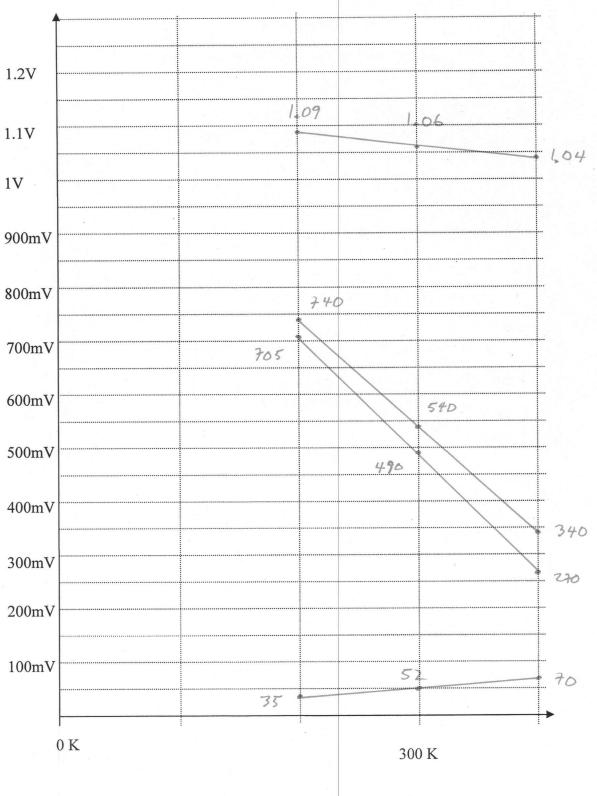

3) [22] A particular diode D1 has a saturation current of 1pA, and at 1mA current at room temperature the diode voltage has a temperature coefficient of -2mV/K. You are using copies of this diode to make a bandgap reference as in Lab 4, with D2 composed of seven copies of D1. You can use the approximation that  $ln(7) \sim 2$ . Assuming that the current in both diodes is maintained at 1mA at room temperature

b. What is the voltage on D2 at room temperature? In (7) Vat smaller = 0.490 V

c. What is the different between the two diode voltages at 200K, 300K, and 400K? 400K = 70mV 300K=52mV

200K = 35 mV d. What is the temperature coefficient of the voltage on D2?  $-\frac{2mV}{K} - \frac{52mV}{300K} = -2.17$

e. Roughly what is the right value for R1? 52mV = 52 52

f. On the following page, carefully sketch by hand the voltage on D1, the voltage on D2, and the difference between them as a function of temperature from 200K to 400K. g. On the same plot, if  $R_3=R_2=10$   $R_1$ , sketch  $V_{ref}$  vs. temperature from 200K to 400K.

It will help your grade if you draw carefully and label the voltage values of any dots that you draw.

10(70) + 340 = 60.40 10(52) + 540 = 600 10(35) + 740 = 6020

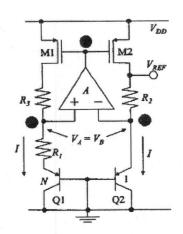

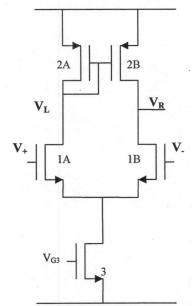

4) [15] For the differential amplifier in the figure below, estimate the change in  $V_{TAIL}$ ,  $I_{TAIL}$ ,  $V_L$ , and  $V_R$  due to

a. An increase of  $\Delta V$  in both V+ and V-

b. An increase of  $\Delta V$  in just V+

c. An increase of  $\Delta V$  in just V-

Give your answers in terms of  $g_{mi}$ ,  $r_{oj}$ , and assume that  $g_m * r_o >> 1$  for all i,j combinations.

|                      | V <sub>TAIL</sub> | I <sub>TAIL</sub> | $V_{\rm L}$         | $V_R$             |

|----------------------|-------------------|-------------------|---------------------|-------------------|

| ΔV in both V+ and V- | ΔV                | To3               | - DV<br>2003 gm2    | 2003 gm2          |

| ΔV in just V+        | AV/2              | 2ro3              | - LVgml. 1<br>2 gm2 | DVgml sollsoz     |

| ΔV in just V-        | DV/2              | <u>OV</u><br>2603 | DV gm1, 1<br>2 gm2  | - Avgml For// Foz |

+1 each box +1 for correct signs in each row