## Homework Assignment #3v2

Due by online submission Wednesday 2/10/2016 (Thursday 9am)

- 1. An NPN common emitter amplifier has a 10V supply and a  $10k\Omega$  load in parallel with 100pF. Assume  $V_A$ =100V. You should be able to do all of the calculations by hand (without calculators). One-ish significant digits is fine.

- a. Write an expression for  $I_C$  as a function of output bias point.

- b. Write an expression for  $g_m$  and  $r_o$  as a function of output bias point.

- c. Write an expression for  $A_{v0}$  as a function of output bias point.

- d. For each of the output bias points  $\{9V, 8V, 5V, 1V\}$ , calculate the current in the device,  $g_m$ ,  $r_o$ ,  $A_{v0}$ ,  $\omega_p$ , and  $\omega_u$ . Fill in a table with those columns.

- e. roughly how much does the input bias point Vin change over this range of output bias points?

- f. Plot the output response to a 1mV input step on 3 time scales: 1ns, 1µs, 1ms.

- 2. Write down a table of settling error vs. time for  $t/\tau = \{1,3,5,7\}$ . Use a calculator for this one. Memorize the table to one significant digit.

- 3. A common source amplifier has a resistive load  $R_L$  and  $\lambda=1/(10V)$ .  $V_{DD}=2V$ , and the output bias point is 1V.

- a. At this bias point, if the resistive load has the same impedance as the output resistance of the transistor, what is the supply voltage  $V_{\rm DD}$ ?

- b. Should we approximate the output resistance  $R_O$  as  $R_L$  or  $r_o$ ? Why? What error in output resistance do we get if we make that approximation?

- c. With that approximation, write an expression for the gain that involves only voltages and a constant (no resistances, transconductances, etc.)

- 4. A single-pole amplifier has a low frequency gain of 100. At 100MHz the gain is 5. What are the pole frequency and the unity gain frequency?

- 5. Fill in the following table

| $A_{v0}$ | $\omega_{ m p}$ | $\omega_{\mathrm{u}}$ | $\mathbf{g}_{\mathbf{m}}$ | r <sub>o</sub> | $C_{L}$ |

|----------|-----------------|-----------------------|---------------------------|----------------|---------|

| 1000     | 1M              |                       |                           |                | 1p      |

|          | 10M             | 1G                    |                           | 100k           |         |

|          |                 | 1G                    |                           | 1M             | 10f     |

|          | 10              | 1M                    |                           |                | 10p     |

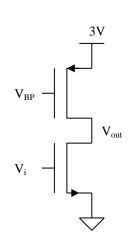

- 6. For the common source amplifier, assume  $\mu C_{ox}(W/L)=1mA/V^2$ ,  $|V_t|=1V$ , and  $\lambda=0.1V^{-1}$  for both devices.

- A) Assuming  $V_{BP} = 1.8$  V, calculate  $V_{dsatp}$  and  $I_{dp}$  at  $Vdp = V_{DD} |Vdsatp|$  for the PMOS transistor.

- B) Plot |Idp| vs. Vout. What is the minimum and maximum value for Idp with the PMOS device in saturation in this circuit?

- C) What is the approximate value of V<sub>i</sub> for which the PMOS device is just on the edge between the saturation and linear regions? (you calculated the current and output voltage at which this happens in part A above). Considering just the current/voltage relationship for the NMOS device, plot Idn at this Vi on the same plot as step B.

- D) What is the value of V<sub>i</sub> for which the NMOS device leaves saturation? Again, considering only the NMOS device, plot Idn at this value of V<sub>i</sub> on the same plot as B.

- E) Based on these values, plot  $V_{out}$  vs  $V_i$ , paying careful attention to the location of the endpoints of the high gain region (calculated in parts C and D above).

- F) Based on the (Vi, Vout) pairs that you calculated in C & D, what is the gain of the amplifier? What are the input and output range over which this gain is achieved.

- G) Calculate the gain for this amplifier using the small signal model evaluated at 3 different operating points for Vout: the edges of the high gain region, and the center of the high gain region.