# EECS 244: Overview of the IC Design Flow

Prof. Kurt Keutzer

EECS

keutzer@eecs.berkeley.edu

1

# Class News

• Web page almost up – stay tuned!

# **Important Class Dates**

- Project teams + topics (1 paragraph) due 9/13

- Full project proposals due 9/29

- Exam 1 Handed out 10/6

- Exam 1 collected at BEGINNING of class 10/11

- Preliminary project report due 11/1

- Exam 2 Handed out 11/3

- Exam 2 collected at BEGINNING of class 11/8

- Final project presentations between 12/6 and 12/8

3

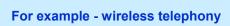

# **Application**

- Motivated by:

- A bright idea

- A market opportunity

- An emerging market

- A high growth market

- A technological breakthrough

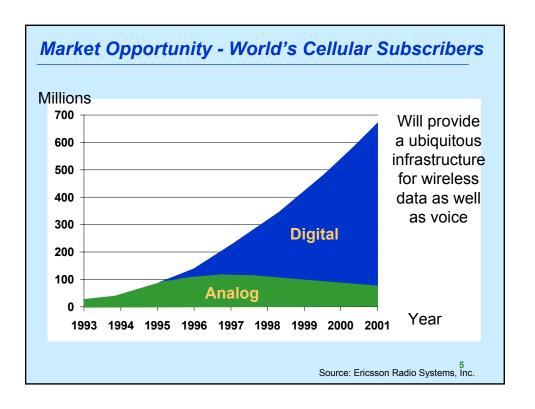

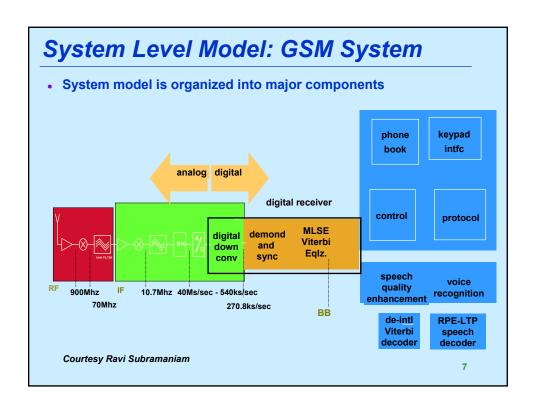

# **Specification**

- Function, performance (power, delay, area), cost

- A competitor's

- Integrated circuit

- Data sheet

- A napkin

- · An industry standard

For example, GSM standard for cellular telephony

# Current Practice: HDL at RTL Level

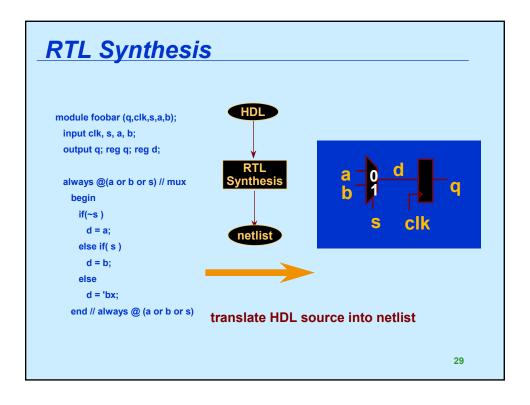

```

module foobar (q,clk,s,a,b);

input clk, s, a, b;

always @(clk) // latch

output q; reg q; reg d;

always @(a or b or s) // mux

begin

begin

if(clk == 1)

if(!s)

q = d;

d = a;

else if( clk !== 0 )

else if(s)

q = bx;

d = b;

end // always @ (clk)

else

d = bx;

end // always @ (a or b or s)

endmodule

14

```

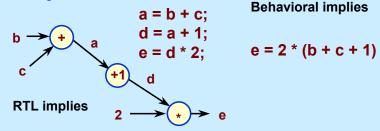

### RTL level

An RTL description is always implicitly structural - the registers and their interconnectivity are defined

Thus the clock-to-clock behavior is defined

Only the control logic for the transfers is synthesized.

This approach can be enhanced:

- **Register inferencing**

- **Automating resource allocation**

**Behavioral implies**

$$e = 2 * (b + c + 1)$$

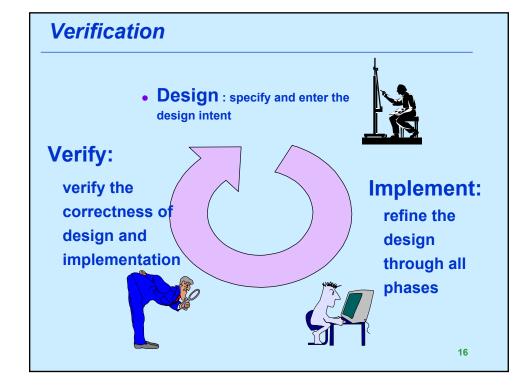

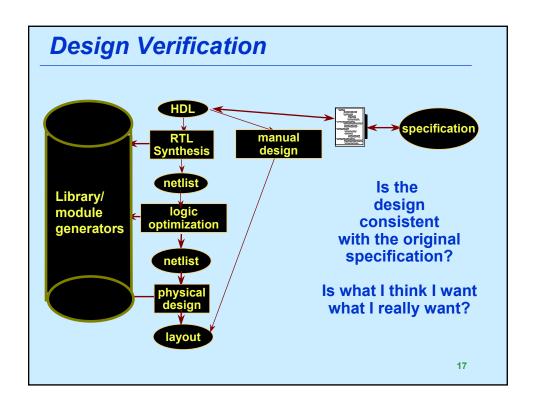

# Approaches to Design Verification

- Formal verification

- Model checking prove properties relative to model

- Theorem proving prove properties of a circuit

- Simulation

- Application of simulation stimulus to model of circuit

- Emulation

- Implement a version of the circuit on emulator

- Rapid prototyping

- · Create a prototype of actual hardware

# Simulation Simulation driver (vectors) Simulation model (HDL) Simulation monitor (yes/no)

# Types of software simulators

- Circuit simulation

- Spice, Advice, Hspice

- Timemill + Ace, ADM

- Event-driven gate/RTL/Behavioral simulation

- Verilog VCS, NC-Verilog, Turbo-Verilog, Verilog-XL

- VHDL VSS, MTI, Leapfrog

- Cycle-based gate/RTL/Behavioral simulation

- Verilog Speedsim

- VHDL Cyclone

- Generic system-level simulation SystemC

- Domain-specific simulation

- SPW, COSSAP,

- · Architecture-specific simulation

- VAST, Axys, Lisatek

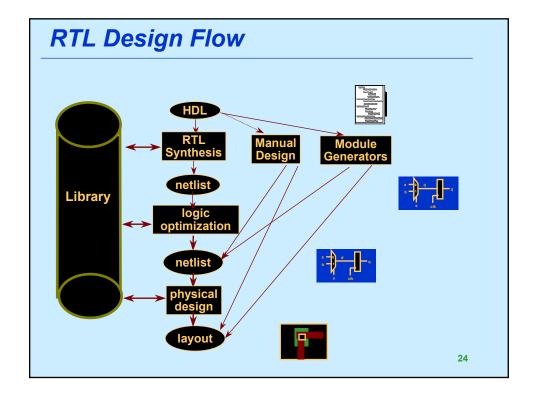

# **Manual Design**

- Performed at

- Gate level (100 gates/week) /gate-level editor

- Transistor level (10 20 gates week)/tr level editor

- · Very expensive in design cost and design time -

- Used for:

- Analog

- · Leaf cells libraries, memory cells

- Datapaths in high performance designs DSP, microprocessor etc.

25

### **Module Generators**

- Parameterized generators of actual physical layout

- Typically used for:

- Memories (word length, #words, # ports)

- Programmable logic arrays (PLA)

- Register files

- Occasionally used for:

- Multipliers

- General-purpose datapath

- Datapaths in high performance designs DSP, microprocessors etc.

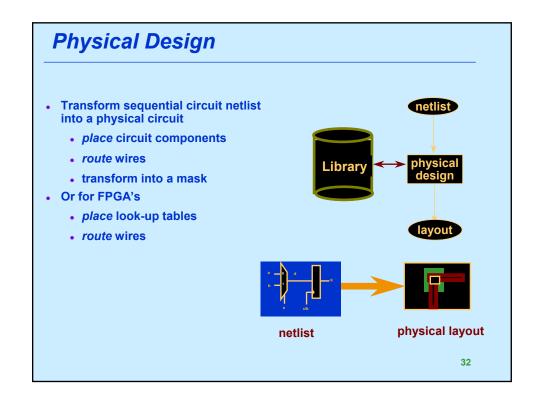

# Library

- Contains for each cell:

- Functional information: cell = a \*b \* c

- Timing information: function of

- input slew

- intrinsic delay

- output capacitance

non-linear models used in tabular approach

- Physical footprint (area)

- Power characteristics

- · Wire-load models function of

- Block size

- Wiring

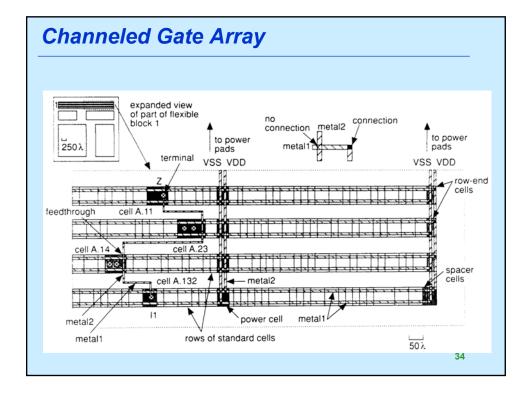

## Channeled and Channel less

- Routing:

- Channel based: Routing only in channels between gates

(few metal layers: 2)

• Channel less: Routing over gates

(many metal layers: 3 - 6)

- Often split in two steps:

- Global route: Find a coarse route depending on local routing density

- Detailed route: Generate routing layout

- . J. Christiansen,

- CERN EP/MIC

- Jorgen.Christiansen@cern.ch

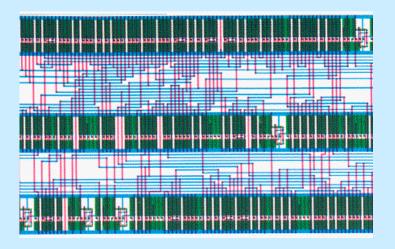

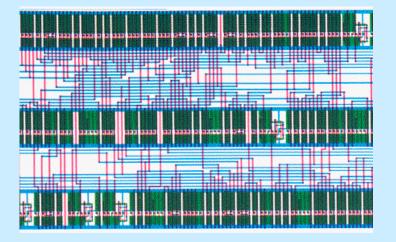

# Standard Cell Layout

35

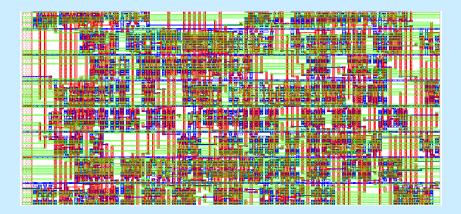

# **Channel less Cells**

• Arbitrary routing over cells

# Resulting Layout

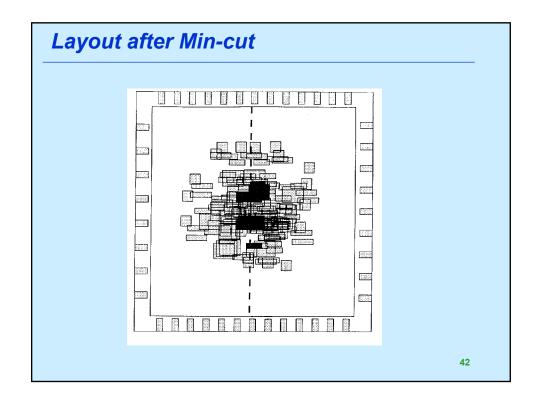

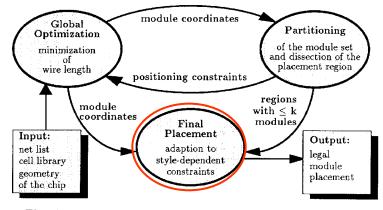

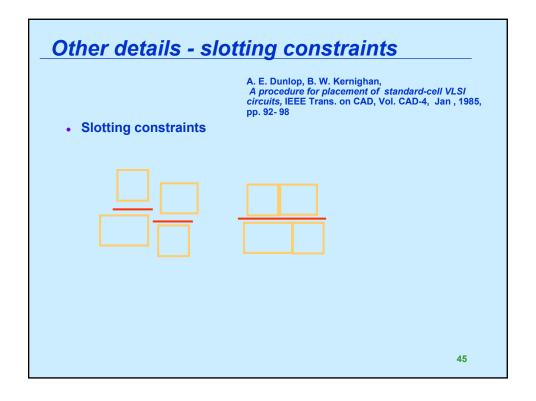

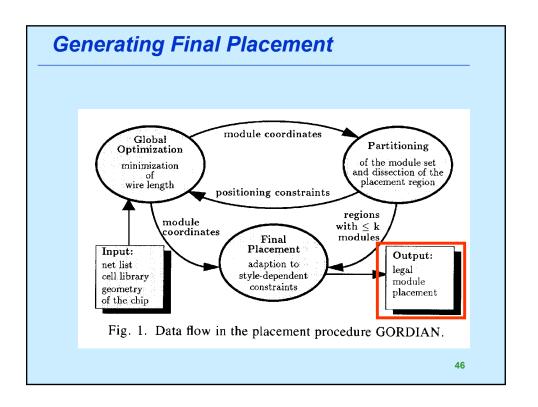

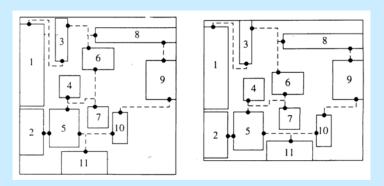

# Final Placement

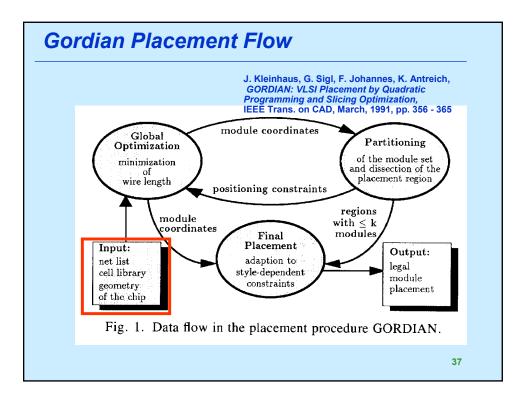

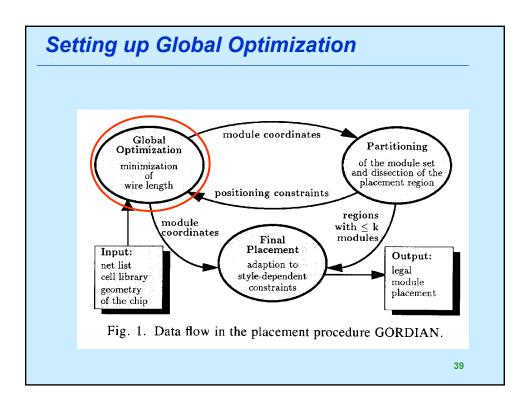

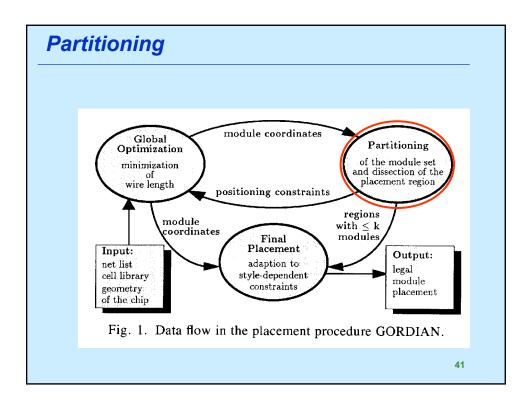

Fig. 1. Data flow in the placement procedure GORDIAN.

43

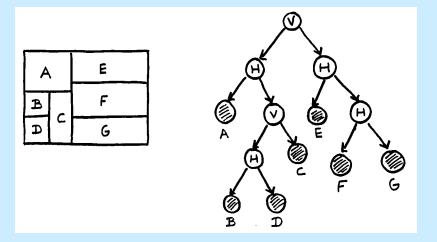

# Slicing Tree

# Standard Cell Layout

47

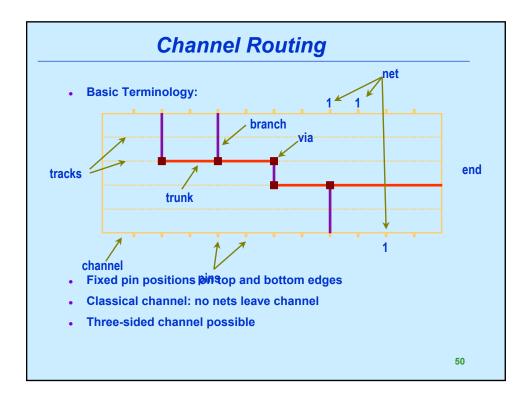

# **Routing**

- To simplify routing problem, divide it into two phases

- Global

- Detailed

- Global routing

- Define routing regions

- Assign nets to regions

- Detailed (Channel) routing

- Route nets within each region

- Assign nets to pins

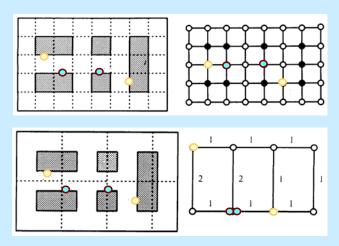

# **Global Routing**

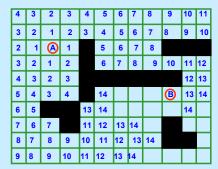

- Grid-Graph Model

- Checker-Board Graph (also use slicing structure)

# **Maze Routing**

Basic idea -- wave propagation method(Lee, 1961)

- Breadth-first search

- Back-tracing after finding the shortest path

- guarantee to find the shortest path

51

# Followed by Two-Dimensional Compaction

X then Y 1D Compaction

Y then X 1D Compaction

# **Placed and Routed Standard Cells**

53

# **Another Final Placement**

Fig. 10. Macrocell design with standard cell blocks scb8 and scb9.

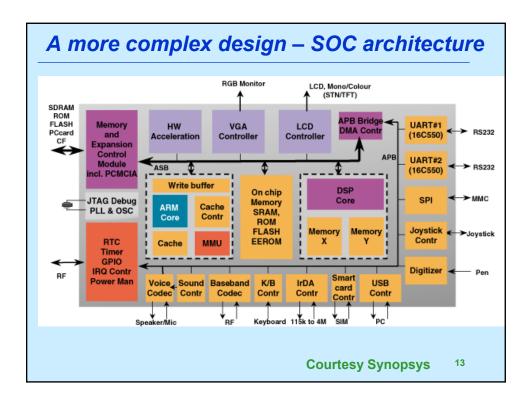

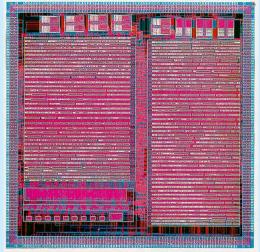

# **Current Status of RTL Design Flow**

- Current RTL design flow is able to produce

- High speed microprocessors e.g. Alpha, Pentium Pro > 1M gate-equivalents > 1GHz. (with intervention)

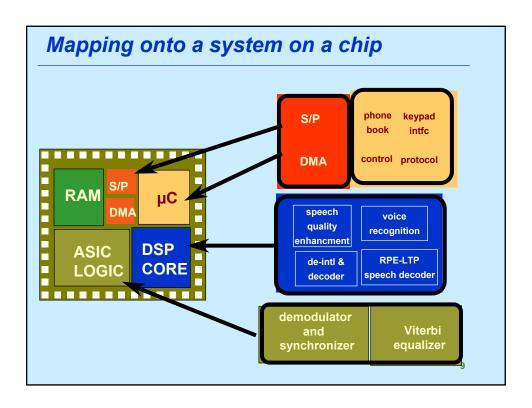

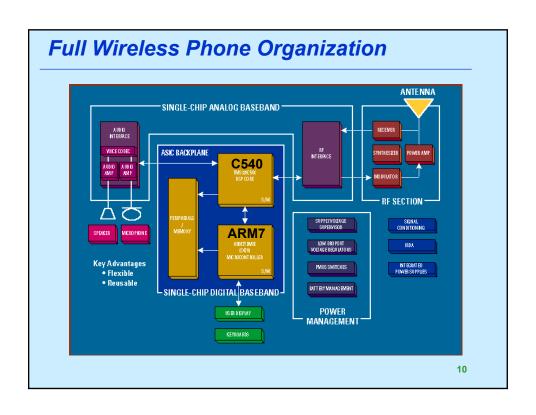

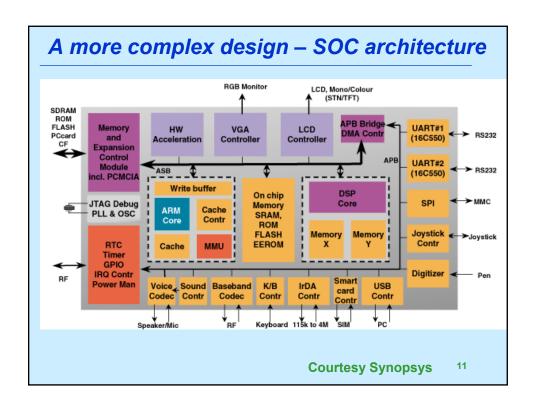

- · System-on-a-chip/Systems on silicon

- Integration of micro-p, DSP, memory and ASIC on a single die > 10M gate-equivalents >500MHz.

- Rapid turnaround "Structured" ASIC

- ISSP-90 HIS from NEC

- ~ 3M usable gates

- ~10 Mb SRAM; 10G SerDes

- RTL Design flow now used for FPGA's as well

- RTL synthesis provided by independent vendors e.g.

Synplicity as well as FPGA providers e.g. Xilinx

- Place and route provided by FPGA vendors e.g. Xilinx