### UNIVERSITY OF CALIFORNIA Santa Barbara

# Linear Algebraic Primitives for Parallel Computing on Large Graphs

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Aydın Buluç

#### Committee in Charge:

Professor John R. Gilbert, Chair

Professor Shivkumar Chandrasekaran

Professor Frederic T. Chong

Professor Ömer N. Eğecioğlu

March 2010

# The Dissertation of Aydın Buluç is approved:

Professor Shivkumar Chandrasekaran

Professor Frederic T. Chong

Professor Ömer N. Eğecioğlu

Professor John R. Gilbert, Committee Chairperson

March 2010

Linear Algebraic Primitives for Parallel Computing on Large Graphs

Copyright  $\bigcirc$  2010

by

Aydın Buluç

To my friend of misery.

### Acknowledgements

It is a great pleasure to thank everybody who made this thesis possible.

It is downright impossible to overstate how thankful I am to my advisor, John R. Gilbert. He has been a magnificant advisor and a great role model in all aspects: as a scientist, collaborator, teacher, and manager. He provided me a great work environment, perfectly balanced between my thesis work and the side projects that I wanted to pursue. This allowed me to enhance my breadth of knowledge of the general areas of parallel computing, sparse linear algebra and graph algorithms, without comprimising my depth of knowledge on my thesis work. Especially during my junior years as his Ph.D. student, John was as patient as a human being can ever be, pointing me to the right direction over and over again, secretly knowing that I would keep on asking the same type of questions for another three months until I would get mature enough to comprehend what he had been trying to tell me from the very beginning. I will always remember his amazing ability to motivate me without micromanaging.

I am grateful to all my committee members, for their time and valuable feedback. I am especially indebted to Ömer N. Eğecioğlu for being my mentor from the very first day I came to UCSB. He gave me more of his time than I probably deserved. I want to thank Alan Edelman for officially hosting me during my visit

to MIT, and giving me the opportunity to meet extremely smart people from all fields.

Special thanks to Charles E. Leiserson for his lead in reshaping our casual research discussion into a real collaboration. I am truly amazed by his outstanding scholarship and strong work ethics. The chapter on parallel sparse matrix-vector multiplication is a reprint of the material resulted from that collaboration with Jeremy T. Fineman and Matteo Frigo. I learned a lot from all three of them.

I am grateful to Erik Boman for having me at Sandia National Labs as a summer intern in 2008. I thank all the folks in our group at Sandia/Albuquerque for their company. Special thanks to Bruce Hendrickson for his support and encouragement. As a great scientist, he has a unique ability to stay righteous while speaking his opinions without reservations.

I would also like to thank my lab mates over the years: Viral Shah, Vikram Aggarwal, Imran Patel, Stefan Karpinski and Adam Lugowski. Many times, our conversations and meetings helped me think out of the box or sharpen my arguments.

When it comes to who gets the most credits about who I become, my family can simply not face competition. Thanks to "Annem ve Babam" who has supported me and my decisions without reservations. I know they would make God their enemy in this cause, if they had to.

I would like to thank all my friends who made my journey enjoyable. Special thanks to Murat Altay and Lütfiye Bulut for generously opening up their apartment to me while I was visiting MIT. Many thanks to my off-county friends, Simla Ceyhan and Osman Ertörer, for making North California my third home. I am especially grateful to Ahmet Bulut, Petko Bogdanov, Ali Irturk, Arda Atalı, Ceren Budak, Bahar Köymen, Emre Sargın, Başak Alper, Pegah Kamousi, Mike Wittie and Lara Deek for their company at UCSB. Vlasia Anagnostopoulou gets the most credit for reasons that will stay with me longer.

### Curriculum Vitæ

### Aydın Buluç

#### Education

2009 Master of Science in Computer Science, UC Santa Barbara.

2005 Bachelor of Science in Computer Science, Sabanci University

#### Experience

2007 – Present Graduate Research Assistant, UC Santa Barbara.

2008 Summer Intern, Sandia National Labs

2006 Summer Intern, Citrix Online

2005 – 2007 Teaching Assistant, UC Santa Barbara.

#### Selected Publications

Aydın Buluç and John R. Gilbert. "On the Representation and Multiplication of Hypersparse Matrices," In *Proceedings of the 22nd IEEE International Parallel and Distributed Processing Symposium (IPDPS)*, April 2008.

Aydın Buluç and John R. Gilbert. "Challenges and Advances in Parallel Sparse Matrix-Matrix Multiplication," In *Proceedings of the 37th International Conference on Parallel Processing (ICPP)*, September, 2008.

Aydın Buluç, Jeremy T. Fineman, Matteo Frigo, John R. Gilbert, and Charles E. Leiserson "Parallel Sparse Matrix-Vector and Matrix-Transpose-Vector Multiplication using

Compressed Sparse Blocks" In Proceedings of the 21st ACM Symposium on Parallelism in Algorithms and Architectures (SPAA), August 2009.

Aydın Buluç, Ceren Budak, and John R. Gilbert. "Solving path problems on the GPU", Parallel Computing (2009), in press.

#### Abstract

## Linear Algebraic Primitives for Parallel Computing on Large Graphs

#### Aydın Buluç

This dissertation presents a scalable high-performance software library to be used for graph analysis and data mining. Large combinatorial graphs appear in many applications of high-performance computing, including computational biology, informatics, analytics, web search, dynamical systems, and sparse matrix methods.

Graph computations are difficult to parallelize using traditional approaches due to their irregular nature and low operational intensity. Many graph computations, however, contain sufficient coarse grained parallelism for thousands of processors that can be uncovered by using the right primitives. We will describe the Parallel Combinatorial BLAS, which consists of a small but powerful set of linear algebra primitives specifically targeting graph and data mining applications.

Given a set of sparse matrix primitives, our approach to developing a library consists of three steps. We (1) design scalable parallel algorithms for the key primitives, analyze their performance, and implement them on distributed memory machines, (2) develop reusable software and evaluate its performance, and finally (3) perform pilot studies on emerging architectures.

The technical heart of this thesis is the development of a scalable sparse (generalized) matrix-matrix multiplication algorithm, which we use extensively as a primitive operation for many graph algorithms such as betweenness centrality, graph clustering, graph contraction, and subgraph extraction. We show that 2D algorithms scale better than 1D algorithms for sparse matrix-matrix multiplication. Our 2D algorithms perform well in theory and in practice.

# Contents

| A            | ckno  | wledgements                                     | V    |

|--------------|-------|-------------------------------------------------|------|

| $\mathbf{C}$ | urric | ulum Vitæ                                       | viii |

| A            | bstra | act                                             | X    |

| Li           | st of | Figures                                         | xvi  |

| Li           | st of | Tables                                          | XX   |

| 1            | Intr  | oduction and Background                         | 1    |

|              | 1.1   | The Landscape of Parallel Computing             | 2    |

|              | 1.2   | Parallel Graph Computations                     | 6    |

|              | 1.3   | The Case for Primitives                         | 11   |

|              |       | 1.3.1 A Short Survey of Primitives              | 12   |

|              |       | 1.3.2 Graph Primitives                          | 14   |

|              | 1.4   | The Case for Sparse Matrices                    | 15   |

|              | 1.5   | Definitions and Conventions                     | 18   |

|              |       | 1.5.1 Synthetic R-MAT Graphs                    | 19   |

|              |       | 1.5.2 Erdős-Rényi Random Graphs                 | 19   |

|              |       | 1.5.3 Regular 3D Grids                          | 20   |

|              | 1.6   | Contributions                                   | 20   |

| <b>2</b>     | Imp   | plementing Sparse Matrices for Graph Algorithms | 23   |

|              | 2.1   | Introduction                                    | 23   |

|              | 2.2   | Key Primitives                                  | 29   |

|              | 2.3   | Triples                                         | 32   |

|              |       | 2.3.1 Unordered Triples                         | 36   |

|   |     | 2.3.2   | Row-Ordered Triples                          | 42  |

|---|-----|---------|----------------------------------------------|-----|

|   |     | 2.3.3   | v i                                          | 50  |

|   | 2.4 | Compr   | ressed Sparse Row/Column                     | 55  |

|   |     | 2.4.1   | CSR and Adjacency Lists                      | 56  |

|   |     | 2.4.2   | CSR on Key Primitives                        | 58  |

|   | 2.5 | Other   | Related Work and Conclusion                  | 62  |

| 3 | Nev |         | 1                                            | 64  |

|   | 3.1 |         |                                              | 64  |

|   | 3.2 | Sequen  | 1 0                                          | 69  |

|   |     | 3.2.1   | Hypersparse Matrices                         | 73  |

|   |     | 3.2.2   | •                                            | 82  |

|   |     | 3.2.3   | Performance of the Cache Efficient Algorithm | 88  |

|   | 3.3 | Paralle | el Algorithms for Sparse GEMM                | 90  |

|   |     | 3.3.1   | 1D Decomposition                             | 90  |

|   |     | 3.3.2   | 2D Decomposition                             | 91  |

|   |     | 3.3.3   | Sparse 1D Algorithm                          | 91  |

|   |     | 3.3.4   | Sparse Cannon                                | 92  |

|   |     | 3.3.5   | Sparse SUMMA                                 | 94  |

|   | 3.4 | Analys  | sis of Parallel Algorithms                   | 95  |

|   |     | 3.4.1   | Scalability of the 1D Algorithm              | 97  |

|   |     | 3.4.2   | Scalability of the 2D Algorithms             | 97  |

|   | 3.5 | Perform |                                              | 00  |

|   |     | 3.5.1   |                                              | .01 |

|   |     | 3.5.2   | Scalability with Hypersparsity               | .05 |

|   | 3.6 | Paralle |                                              | .11 |

|   |     | 3.6.1   | Experimental Design                          | .11 |

|   |     | 3.6.2   |                                              | 13  |

|   | 3.7 | Alterna |                                              | 19  |

|   |     | 3.7.1   | Load Balancing and Asynchronous Algorithms   | 19  |

|   |     | 3.7.2   | · · · · · · · · · · · · · · · · · · ·        | 24  |

|   |     | 3.7.3   |                                              | 25  |

|   | 3.8 | Future  | ·                                            | .30 |

| 4 | The | Comb    | oinatorial BLAS: Design and Implementation 1 | 32  |

|   | 4.1 |         |                                              | .32 |

|   | 4.2 |         |                                              | .33 |

|   |     | 4.2.1   | - ·                                          | .33 |

|   |     | 4.2.2   |                                              | 35  |

|   | 12  | A Rofo  |                                              | 11  |

|   |      | 4.3.1   | The Software Architecture                                                |              |

|---|------|---------|--------------------------------------------------------------------------|--------------|

|   |      | 4.3.2   | Management of Distributed Objects                                        | 146          |

| 5 | The  | Coml    | binatorial BLAS: Applications and Performance Anal                       | l <b>-</b>   |

|   | ysis |         |                                                                          | 149          |

|   | 5.1  | Betwe   | enness Centrality                                                        | 150          |

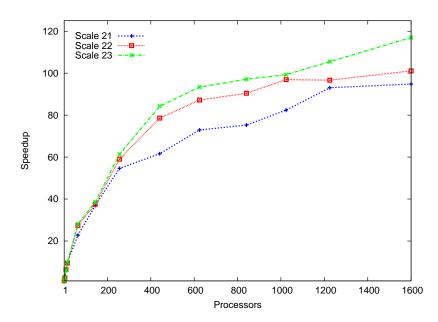

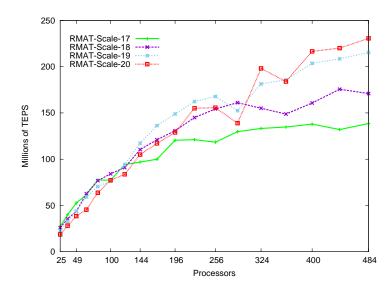

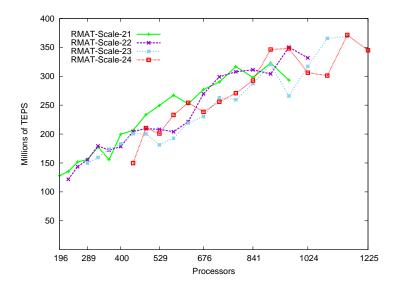

|   |      | 5.1.1   | Parallel Strong Scaling                                                  | 153          |

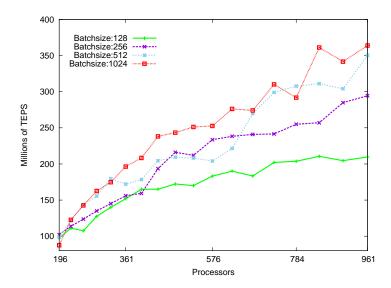

|   |      | 5.1.2   | Sensitivity to Batch Processing                                          | 155          |

|   | 5.2  | Marko   | ov Clustering                                                            | 157          |

| 6 | Para | allel S | parse $y \leftarrow Ax$ and $y \leftarrow A^{T}x$ Using Compressed Spars | $\mathbf{e}$ |

|   | Bloc | cks     |                                                                          | 161          |

|   | 6.1  | Introd  | luction                                                                  | 162          |

|   | 6.2  |         | entional storage formats                                                 | 165          |

|   | 6.3  |         | CSB storage format                                                       | 172          |

|   | 6.4  |         | x-vector multiplication using CSB                                        | 178          |

|   | 6.5  | Analy   | sis                                                                      | 186          |

|   | 6.6  | Exper   | imental design                                                           | 192          |

|   | 6.7  | _       | imental results                                                          | 202          |

|   | 6.8  | Concl   | usion                                                                    | 211          |

| 7 | Solv | _       | ath Problems on the GPU                                                  | 214          |

|   | 7.1  | Introd  | luction                                                                  | 215          |

|   | 7.2  | _       | ithms Based on Block-Recursive Elimination                               | 218          |

|   |      | 7.2.1   | The All-Pairs Shortest-Paths Problem                                     | 220          |

|   |      | 7.2.2   | Recursive In-Place APSP Algorithm                                        | 223          |

|   | 7.3  |         | Computing Model with CUDA                                                | 229          |

|   |      | 7.3.1   | GPU Programming                                                          | 230          |

|   |      | 7.3.2   | Experiences and Observations                                             | 232          |

|   | 7.4  | Imple   | mentation and Experimentation                                            | 235          |

|   |      | 7.4.1   | Experimental Platforms                                                   | 235          |

|   |      | 7.4.2   | Implementation Details                                                   | 236          |

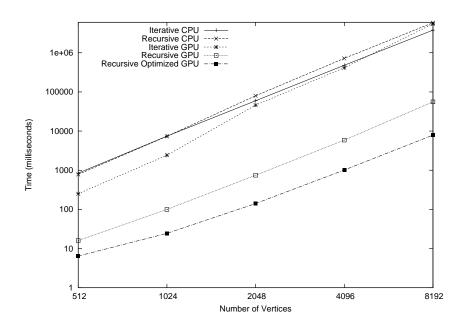

|   |      | 7.4.3   | Performance Results                                                      | 238          |

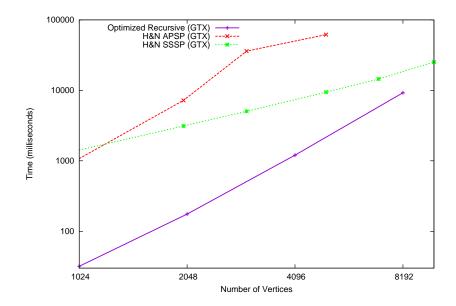

|   |      | 7.4.4   | Comparison with Earlier Performance Results                              | 241          |

|   |      | 7.4.5   | Scalability and Resource Usage                                           | 244          |

|   |      | 7.4.6   | Power and Economic Efficiency                                            | 246          |

|   | 7.5  | Concl   | usions and Future Work                                                   | 249          |

| 8 | Con  | clusio  | ns and Future Directions                                                 | 251          |

| Bi           | ibliography                                                              | 256          |

|--------------|--------------------------------------------------------------------------|--------------|

| $\mathbf{A}$ | ppendices                                                                | 275          |

| A            | Alternative One-Sided Communication Strategies for implering Sparse GEMM | nent-<br>276 |

| В            | Additional Timing Results on the APSP Problem                            | 279          |

# List of Figures

| 2.1                  | A typical memory hierarchy                                                                  |

|----------------------|---------------------------------------------------------------------------------------------|

| 2.2                  | Inner product formulation of matrix multiplication                                          |

| 2.3                  | Outer-product formulation of matrix multiplication                                          |

| 2.4                  | Row-wise formulation of matrix multiplication                                               |

| 2.5                  | Column-wise formulation of matrix multiplication                                            |

| 2.6                  | Multiply sparse matrices column-by-column                                                   |

| 2.7                  | Matrix <b>A</b> (left) and an unordered triples representation (right) . 34                 |

| 2.8                  | Operation $\mathbf{y} \leftarrow \mathbf{A}\mathbf{x}$ using triples                        |

| 2.9                  | Scatters/Accumulates the nonzeros in the SPA                                                |

| 2.10                 | Gathers/Outputs the nonzeros in the SPA                                                     |

| 2.11                 | Operation $\mathbf{C} \leftarrow \mathbf{A} \oplus \mathbf{B}$ using row-ordered triples 47 |

| 2.12                 | Operation $\mathbf{C} \leftarrow \mathbf{AB}$ using row-ordered triples                     |

| 2.13                 | Element-wise indexing of $A(12, 16)$ on row-major ordered triples 51                        |

| 2.14                 | Adjacency list (left) and CSR (right) representations of matrix <b>A</b>                    |

| from                 | Figure 2.7                                                                                  |

| 2.15                 | Operation $\mathbf{y} \leftarrow \mathbf{A}\mathbf{x}$ using CSR                            |

|                      | Operation $\mathbf{C} \leftarrow \mathbf{AB}$ using CSR 61                                  |

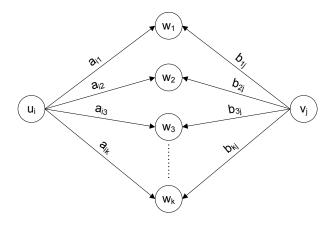

| 3.1                  | Graph representation of the inner product $\mathbf{A}(i,:) \cdot \mathbf{B}(:,j)$ 71        |

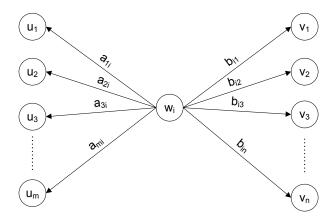

| 3.2                  | Graph representation of the outer product $\mathbf{A}(:,i) \cdot \mathbf{B}(i,:)$ 72        |

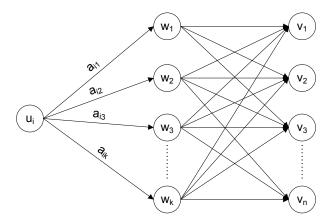

| 3.3                  | Graph representation of the sparse row times matrix product $\mathbf{A}(i, :$               |

| $) \cdot \mathbf{B}$ | 72                                                                                          |

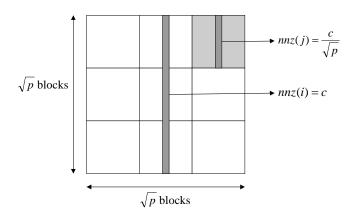

| 3.4                  | 2D Sparse Matrix Decomposition                                                              |

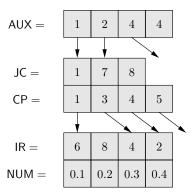

| 3.5                  | Matrix A in CSC format                                                                      |

| 3.6                  | Matrix A in Triples format                                                                  |

| 3.7                  | Matrix A in DCSC format                                                                     |

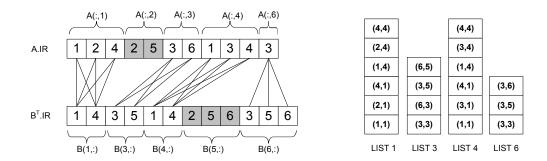

| 3.8                  | Nonzero structures of operands <b>A</b> and <b>B</b>                                        |

| 3.9                  | Cartesian product and the multiway merging analogy 79                                       |

| 3.10              | Pseudocode for hypersparse matrix-matrix multiplication algorithm                 |         |

|-------------------|-----------------------------------------------------------------------------------|---------|

|                   |                                                                                   | 81      |

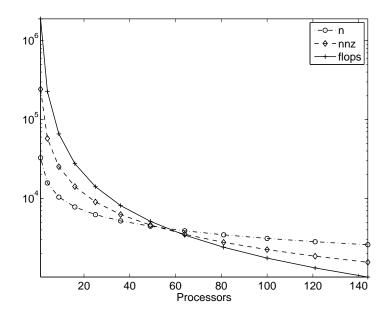

|                   | Trends of different complexity measures for submatrix multiplica-                 | 0.6     |

|                   | as p increases                                                                    | 83      |

|                   | Multiply sparse matrices column-by-column using a heap                            | 85      |

|                   | Subroutine to multiply $bval$ with the next element from the $i$ th list          |         |

|                   | insert it to the priority queue                                                   | 86      |

|                   | Pseudocode for heap assisted column-by-column algorithm                           | 8'      |

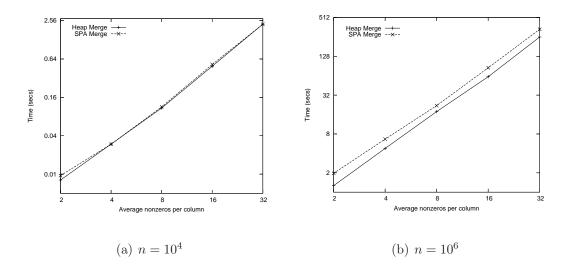

|                   | Performance of two column-wise algorithms for multiplying two                     |         |

|                   | n sparse matrices from Erdős-Rényi random graphs                                  | 89      |

|                   | Operation $\mathbf{C} \leftarrow \mathbf{AB}$ using block row Sparse 1D algorithm | 92      |

|                   | Circularly shift left by $s$ along the processor row                              | 9;      |

|                   | Circularly shift up by $s$ along the processor column                             | 9;      |

|                   | Operation $\mathbf{C} \leftarrow \mathbf{AB}$ using Sparse Cannon                 | 9;      |

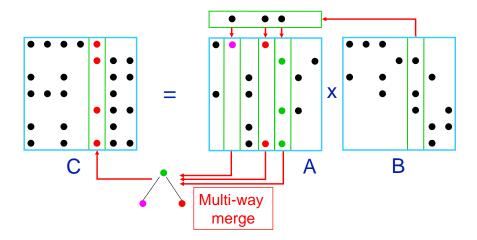

|                   | Sparse SUMMA Execution $(b = n/\sqrt{p})$                                         | 94      |

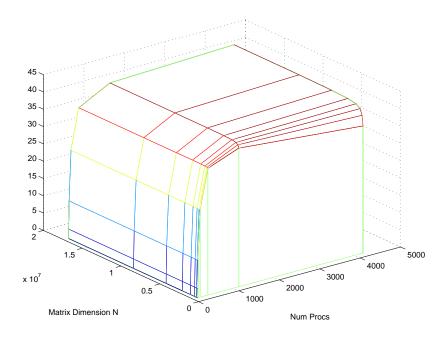

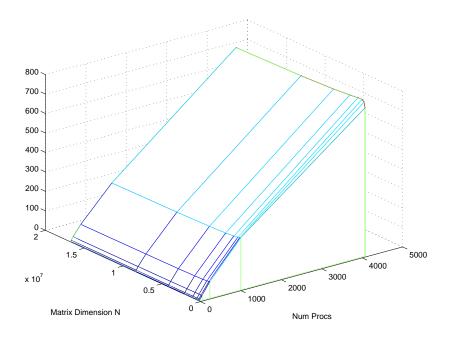

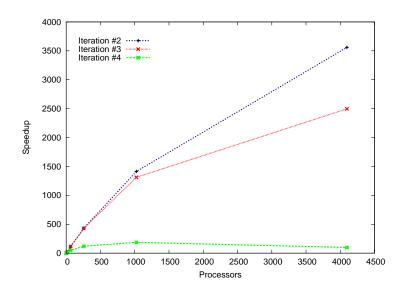

|                   | Modeled speedup of Synchronous Sparse 1D algorithm                                | 105     |

| 3.22              | Modeled speedup of synchronous Sparse Cannon                                      | 10      |

| 3.23              | Modeled speedup of asynchronous Sparse Cannon                                     | 10      |

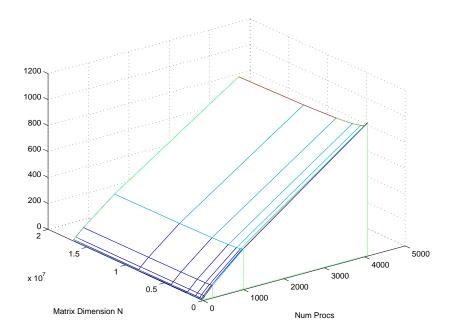

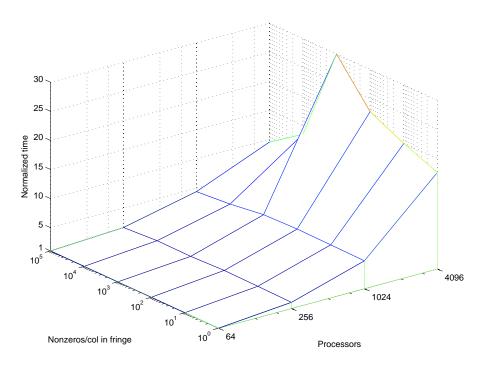

| 3.24              | Model of scalability of SpGEMM kernels                                            | 108     |

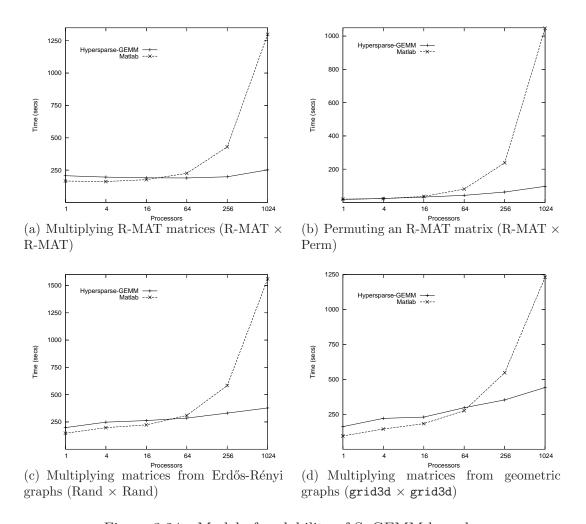

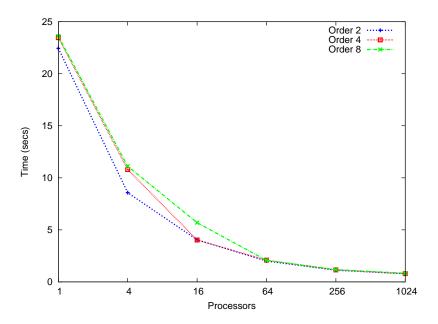

| 3.25              | Observed speedup of of synchronous Sparse SUMMA                                   | 11:     |

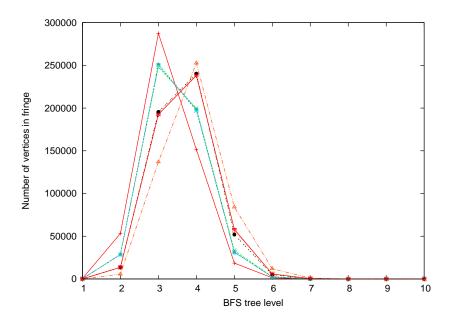

| 3.26              | Fringe size per level during breadth-first search                                 | 114     |

| 3.27              | Weak scaling of R-MAT times a tall skinny Erdős-Rényi matrix .                    | 11'     |

| 3.28              | Strong scaling of multiplication with the restriction operator from               |         |

| the r             | ight                                                                              | 11      |

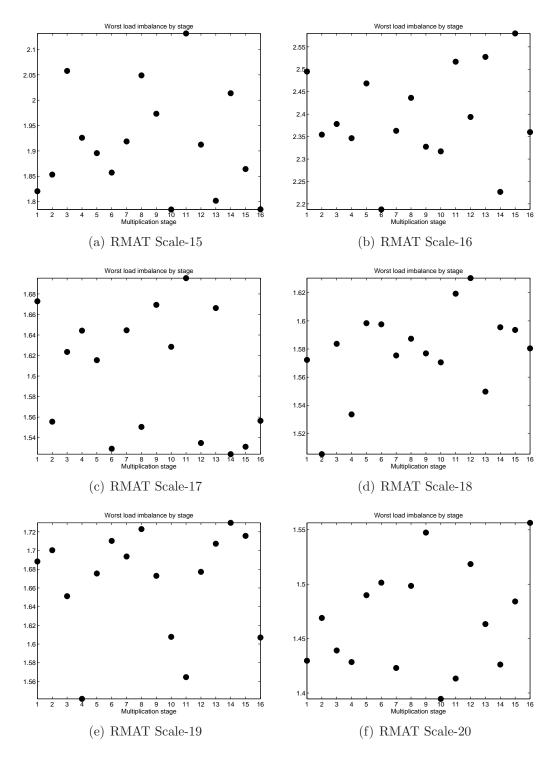

| 3.29              | Load imbalance per stage for multiplying two RMAT matrices on                     |         |

| $256  \mathrm{p}$ | processors using Sparse Cannon                                                    | 125     |

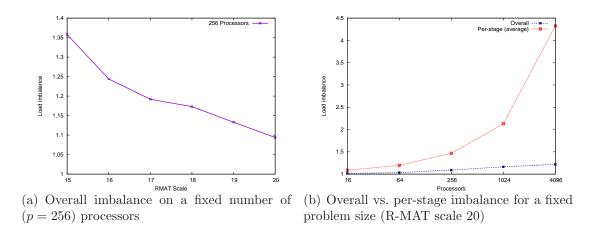

| 3.30              | Load imbalance during parallel multiplication of two RMAT matrices                | 123     |

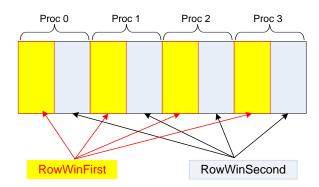

| 3.31              | The split distribution of matrix $\mathbf{A}$ on a single processor row           | 12      |

| 3.32              | Partial C++ code partial for asynchronous SpGEMM using one-                       |         |

| sided             | l communication and split prefetching for overlapping communica-                  |         |

| tion              | with computation                                                                  | 120     |

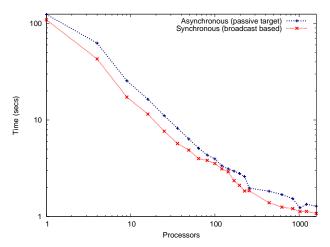

|                   | Performances of the asynchronous and synchronous implementa-                      |         |

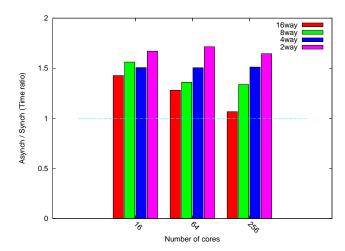

|                   | of the Sparse SUMMA                                                               | 12'     |

| 3.34              | Performance comparison of the asynchronous and synchronous im-                    |         |

|                   | entations usign different number of cores per node                                | 12      |

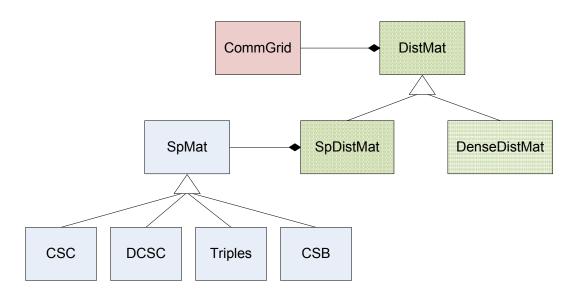

| 4.1               | Software architecture for matrix classes                                          | 143     |

| 4.2               |                                                                                   | 14      |

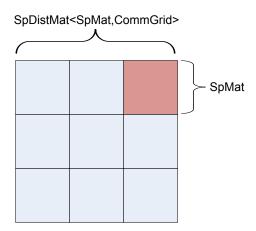

| 4.3               | Distributed sparse matrix class and storage                                       | <br>14' |

| 5.1 Parallel strong scaling of the distributed-memory betweenness                        | cen-    |

|------------------------------------------------------------------------------------------|---------|

| trality implementation (smaller input sizes)                                             | 153     |

| 5.2 Parallel strong scaling of the distributed-memory betweenness                        |         |

| trality implementation (bigger input sizes)                                              | 154     |

| 5.3 The effect of batch processing on the performance of the distribu                    | ited-   |

| memory betweenness centrality implementation                                             |         |

| 5.4 Inflation code using the Combinatorial BLAS primitives                               |         |

| 5.5 MCL code using the Combinatorial BLAS primitives                                     | 158     |

| 5.6 Strong scaling of the three most expensive iterations while clus                     | ster-   |

| ing an R-MAT graph of scale 14 using the MCL algorithm implement                         | nted    |

| using the Combinatorial BLAS                                                             | 160     |

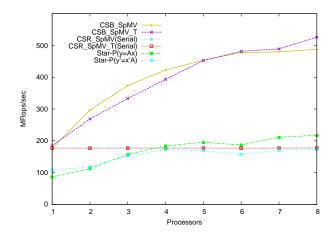

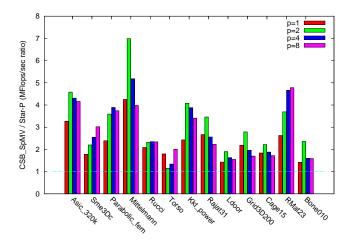

| 6.1 Average performance of $Ax$ and $A^{T}x$ operations on 13 difference                 | erent   |

| matrices from our benchmark test suite                                                   | 164     |

| 6.2 Parallel procedure for computing $y \leftarrow Ax$ , where the $n \times n$ ma       | atrix   |

| A is stored in CSR format.                                                               |         |

| 6.3 Serial procedure for computing $y \leftarrow A^{T} x$ , where the $n \times n$ ma    | atrix   |

| A is stored in CSR format.                                                               | 170     |

| 6.4 Pseudocode for the matrix-vector multiplication $y \leftarrow Ax$                    |         |

| 6.5 Pseudocode for the subblockrow vector product $y \leftarrow (A_{i\ell}A_{i,\ell+1})$ | 1 · · · |

| $A_{ir})x$                                                                               |         |

| 6.6 Pseudocode for the subblock-vector product $y \leftarrow Mx$                         | 185     |

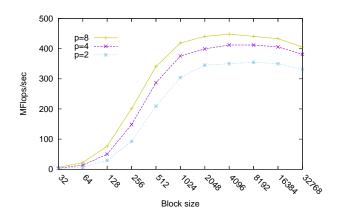

| 6.7 The effect of block size parameter $\beta$ on SpMV performance u                     | sing    |

| the Kkt_power matrix                                                                     | 196     |

| 6.8 Structural information on the sparse matrices used in our exp                        | peri-   |

| ments, ordered by increasing number of nonzeros                                          | 199     |

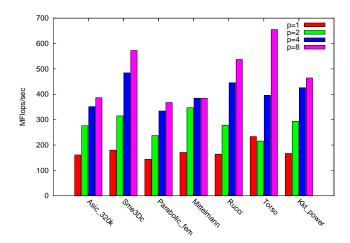

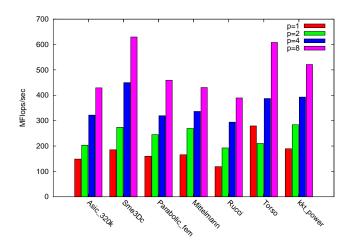

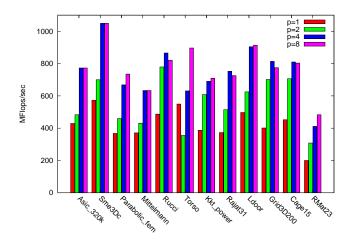

| 6.9 CSB_SPMV performance on Opteron (smaller matrices)                                   | 203     |

| 6.10 CSB_SPMV_T performance on Opteron (smaller matrices).                               | 204     |

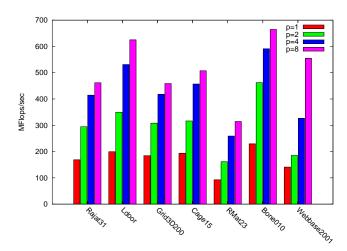

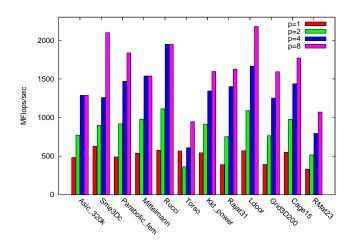

| 6.11 CSB_SPMV performance on Opteron (larger matrices)                                   | 205     |

| 6.12 CSB_SPMV_T performance on Opteron (larger matrices).                                | 206     |

| 6.13 Average speedup results for relatively smaller $(1-7)$ and larger                   | `       |

| 14) matrices. These experiments were conducted on Opteron                                |         |

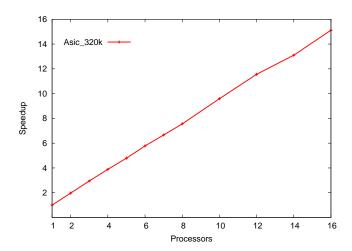

| 6.14 Parallelism test for CSB_SPMV on Asic_320k obtained by an                           | rtifi-  |

| cially increasing the flops per byte                                                     | 207     |

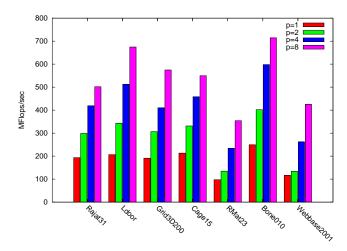

| 6.15 CSB_SPMV performance on Harpertown                                                  |         |

| 6.16 CSB_SPMV performance on Nehalem                                                     |         |

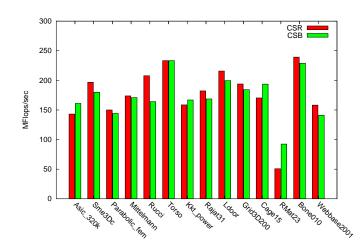

| 6.17 Serial performance comparison of SpMV for CSB and CSR                               |         |

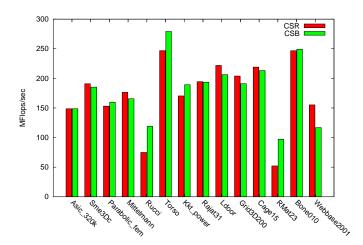

| $6.18$ Serial performance comparison of SpMV_T for CSB and CSR.                          |         |

| 6.19 Performance comparison of parallel CSB_SPMV with Star-P.                            | 213     |

| 7.1      | FW algorithm in the standard notation                                       | 222 |

|----------|-----------------------------------------------------------------------------|-----|

| 7.2      | FW algorithm in linear algebra notation                                     | 223 |

| 7.3      | Pseudocode for recursive in-place APSP                                      | 224 |

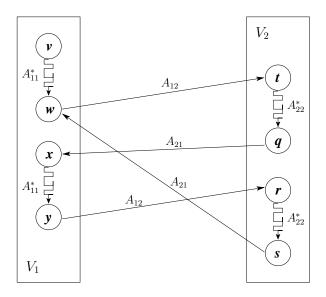

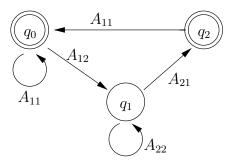

| 7.4      | An example path in $A_{11}^*$                                               | 226 |

| 7.5      | Minimum-state DFA for the path expressions in $A_{11}^*$ , starting state   |     |

| is $q_0$ |                                                                             | 227 |

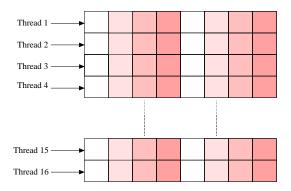

| 7.6      | Stride-1 access per thread (row-major storage)                              | 234 |

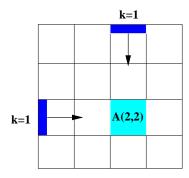

| 7.7      | A shapshot from the execution of the iterative algorithm                    | 237 |

| 7.8      | Log-log plot of absolute running times                                      | 241 |

| 7.9      | Comparison of different GPU implementations on $8800~\mathrm{GTX}$ settings | 242 |

| A.1      | Strategy 1                                                                  | 278 |

| A.2      | Strategy 2                                                                  | 278 |

| A.3      | Strategies for matching the Post calls issued by multiple processors        | 278 |

# List of Tables

| 1.1           | High-performance libraries and toolkits for parallel graph analysis | 6   |

|---------------|---------------------------------------------------------------------|-----|

| 2.1           | RAM Complexities of Key Primitives on Unordered and Row-            |     |

| Ord           | ered Triples                                                        | 35  |

| 2.2           | I/O Complexities of Key Primitives on Unordered and Row-Ordered     |     |

| Trip          | les                                                                 | 36  |

| 2.3           | RAM Complexities of Key Primitives on Row-Major Ordered Triples     |     |

|               | CSR                                                                 | 53  |

| 2.4           | I/O Complexities of Key Primitives on Row-Major Ordered Triples     |     |

| and           | CSR                                                                 | 54  |

| 4.1           | Summary of the current API for the Combinatorial BLAS $$            | 139 |

| 7.1           | GPU timings on GeForce 8800 Ultra (in milliseconds)                 | 238 |

| 7.2           | Speedup on 8800 Ultra w.r.t. the best CPU implementation            | 239 |

| 7.3           | Observed exponents and constants for the asymptotic behaviour of    |     |

| our           | APSP implementations with increasing problem size                   | 240 |

| 7.4           | Performance comparison of our best (optimized recursive) GPU        |     |

| imp           | lementation with parallel Cilk++ code running on Neumann, using     |     |

|               | 6 cores                                                             | 240 |

| 7.5           | Comparisons of our best GPU implementation with the timings         |     |

| _             | orted for Han et al. 's auto generation tool Spiral                 | 244 |

|               | Scalability of our optimized recursive GPU implementation. We       |     |

|               | aked core and memory clock rates using Coolbits                     | 245 |

| 7.7           | Scalability of our iterative GPU implementation. We tweaked core    |     |

|               | memory clock rates using Coolbits                                   | 245 |

| 7.8           | 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                             |     |

| $cod\epsilon$ | es), values in MFlops/Watts×sec (or equivalently MFlops/Joule) .    | 248 |

| B.1 | Serial timings on Intel Core 2 Duo (in milliseconds) | 279 |

|-----|------------------------------------------------------|-----|

| B.2 | Serial timings on Opteron (in milliseconds)          | 280 |

# Chapter 1

# Introduction and Background

Come, Come, Whoever You Are

Wonderer, worshipper, lover of leaving. It doesn't matter.

Ours is not a caravan of despair.

Come, even if you have broken your vow a thousand times

Come, yet again, come, come.

Mevlana Celaleddin Rumi

This thesis provides a scalable high-performance software library, the Combinatorial BLAS, to be used for graph analysis and data mining. It targets parallel computers and its main toolkit is composed of sparse linear algebraic operations.

In this chapter, I will try to give the motivation behind this work. Most of these motivations are accompanied by historical background and references to recent trends. The first section is a personal interpretation of the parallel computing world as of early 2010. Section 1.2 reviews the state of the art of parallel graph computations in practice. The following two sections, Sections 1.3 and 1.4, summarize the justifications of the two main ideas behind this thesis:

the use of primitives and of sparse matrices. The final section summarizes the contributions and provides an outline of this thesis.

## 1.1 The Landscape of Parallel Computing

It is no news that the economy is driving the past, present, and future of computer systems. It was the economy that drove the "killer micro" [45] and stalled innovative supercomputer design in the early 1990s. It is the economy that is driving GPUs to get faster and forcing a unification of GPU/CPU architectures today. It will be the economy that will drive energy efficient computing and massive parallelism. This is partially due to a number of fundamental physical limitations on sequential processing, such as the speed of light and the dissipation of heat [156].

Although the literature contains several taxonomies of parallelism [85, 120, 176], one can talk about two fundamental types of parallelism available for exploitation in software: data parallelism and task parallelism. The former executes the same instruction on a relatively large data set. For example, elementwise addition of two vectors has lots of data parallelism. Task parallelism, on the other hand, is achieved by decomposing the application into multiple independent tasks that can be executed as separate procedures. A multi-threaded web server pro-

vides a good example for task parallelism, where multiple requests of different kinds are handled in parallel. In reality, most applications use a combination of data and task parallelism, and therefore, fall somewhere in the middle of the spectrum. Although it is possible to rewrite some applications that were previously written in the data parallel fashion in a task parallel fashion, and vice versa, this is not always possible.

In general, one can speak about a relationship between the current parallel architectures and types of available parallelism. For example, massively multithreaded architectures [91, 129] are better than others when dealing with large amounts of task parallelism. On the other side, GPUs [1, 2] excel in data parallel computations. However, as most computations cannot be hard-classified as having solely task parallelism or solely data parallelism, an ultimate direct mapping of applications to architectures is unlikely to emerge.

From the late 1990s to the late 2000s, the supercomputing market was mostly dominated by clusters made from commercial off-the-shelf processors. After this decade of relative stability in parallel computing architectures, we are now experiencing disruptions and divergences. Different application have different resource requirements, leading to diversity and heterogeneity in parallel computing architectures. On the other hand, the economic of scale dictate that a handful general-purpose architectures that can be manufactured with low cost will domi-

nate the HPC market. While building custom architectures that perfectly match the underlying problem might be tempting for the HPC community, commodity architectures have the advantage of achieving a much lower cost per unit. Special purpose supercomputers, such as Anton [182], which is used to simulate molecular dynamics of biological systems, will still find applications where the reward exceeds the cost. For broader range of applicability, however, supercomputers that feature a balanced mixture of commodity and custom parts are likely to prevail.

Examples of currently available high-performance computing systems include the following:

- Distributed memory multiprocessors (such as the Cray XT4 and XT5) and beowulf clusters that are primarily programmed using MPI. This class of machines also include the RISC-based distributed-memory multi-processors such as the IBM BlueGene [193],

- ccNUMA and multicore architectures that are programmed either explicitly through pthreads or through concurrency platforms like Cilk/Cilk++ [138],

OpenMP and Intel Building Blocks [167],

- 3. Massively multithreaded shared memory machines such as the Cray XMT [91] and the Sun Niagara [129], and

4. GPU or IBM Cell accelerated clusters. The largest scale example of the latter (as of March 2010) is the Roadrunner system deployed at Los Alamos National Laboratory [22].

Regardless of which architure(s) will prevail in the end, the economic trends favor more parallelism in computing because building a parallel computer using large number of simple processors has proved to be more efficient, both financially and in terms of power, than using a small number of complex processors [181]. The software world has to deal with this revolutionary change in computing. It is safe to say that the software industry has been caught off-guard by this challenge. Most programmers are not fundamentally trained to think "in parallel". Many tools, such as debuggers and profilers, that are taken for granted when writing sequential programs, were (and still are) lacking for parallel software development. In the last few years, there have been improvements towards making parallel programming easier, including parallel debuggers [9, 199], concurrency platforms [138, 167], and various domain specific libraries. Part of this thesis strives to be a significant addition to the latter group of parallel libraries.

One of the most promising approaches for tackling the software challenge in parallel computing is the top-down, application-driven, approach where common algorithmic kernels in various important application domains are identified. In the inspiring Berkeley Report [13], these kernels are called "dwarfs" (or "motifs").

This thesis is mostly concerned about the close interaction between two of those dwarfs: graph traversal and sparse linear algebra.

## 1.2 Parallel Graph Computations

This section surveys working implementations of graph computations, rather than describing research on parallel graph algorithms. We also focus on frameworks and libraries instead of parallelization of stand-alone applications. The current landscape of software for graph computations is summarized in Table 1.1.

Table 1.1: High-performance libraries and toolkits for parallel graph analysis

| Library/Toolkit    | Parallelism | Abstraction   | Offering   | Scalability |

|--------------------|-------------|---------------|------------|-------------|

| PBGL [108]         | Distributed | Visitor       | Algorithms | Limited     |

| GAPDT $[105]$      | Distributed | Sparse Matrix | Both       | Limited     |

| MTGL [30]          | Shared      | Visitor       | Algorithms | Unknown     |

| SNAP [145]         | Shared      | Various       | Both       | Good        |

| Combinatorial BLAS | Distributed | Sparse Matrix | Kernels    | Good        |

The Parallel Boost Graph Library (PBGL) [108] is a parallel library for distributed memory computing on graphs. It is a significant step towards facilitating rapid development of high performance applications that use distributed graphs as their main data structure. Like sequential Boost Graph Library [184], it has a dual focus on efficiency and flexibility. It heavily relies on generic program-

ming through C++ templates. To the user, it offers complete algorithms instead of tools to implement the algorithms. Therefore, its applicability is limited for users who need to experiment with new algorithms or instrument the existing ones. Lumsdaine et al.[143] observed poor scaling of PBGL for some large graph problems.

We believe that the scalability of PBGL is limited due to two main reasons. The graph is distributed by vertices instead of edges, which corresponds to a one-dimensional partitioning in the sparse matrix world. In Chapter 3, we show that this approach is unscalable. We also believe that the *visitor* concept is too low-level for providing scalability in distributed memory because it makes the computation data driven and obstructs opportunies for optimization.

The Graph Algorithms and Pattern Discovery Toolbox (GAPDT) [105] provides several tools to manipulate large graphs interactively. It is designed to run sequentially on MATLAB [104] or in parallel on STAR-P [179], a parallel dialect of MATLAB. Although its focus is on algorithms, the underlying sparse matrix infrastructures of MATLAB and STAR-P also exposes necessary kernels (linear algebraic building blocks, in this case). It targets the same platform as PBGL, namely distributed-memory machines. Differently from PBGL, it uses operations on distributed sparse matrices for parallelism. It provides an interactive environment instead of compiled code, which makes it unique among all the other

approaches we survey here. Similar to PBGL, GAPDT's main weakness is its limited scalability due to the one-dimensional distribution of its sparse matrices.

A number of approaches have been tried in order to mitigate the poor scalability. One architectural approach is to tolerate latency by using massive multithreading. This idea, known as *interleaved multithreading* [135, 201], relies on CPUs that can switch thread contexts on every cycle. Currently, a limited number of architectures are capable of performing true hardware multithreading. Cray XMT(formerly MTA) [91], IBM Cyclops64 [10], and Sun Niagara [129] based servers are among the important examples. The first two exclusively target the niche supercomputing market, therefore limiting their large scale deployment prospects. In contrast, Sun Niagara processors are used in Sun's business servers that run commercial multithreaded applications. With its impressive performace per watt for high throughput applications [134], Niagara may make massive hardware multithreading affordable and widespread as long as it maintains its status as a competitive server platform for commercial applications.

All three massively multithreaded architectures, namely XMT, Cyclops64, and Niagara, tolerate the data access latencies by keeping lots of threads on the fly. Cyclops64 is slightly different than others in the way it manages thread contexts. In Cyclops64, each thread context has its own execution hardware, whereas in MTA/XMT the whole execution pipeline is shared among threads. Niagara is

somewhere in between in the sense that a group of threads (composed of four threads) shares a processing pipeline but each group has a different pipeline from other groups. Niagara differs from the other two also by having large on-die caches, which are managed by a simple cache coherence protocol. Interleaved multithreading, although very promising, has at least one more obstacle in addition to finding a big enough market. The large number of threads that are kept on the fly puts too much pressure on the bandwidth requirements of the interconnect. In the case of MTA-2, this was solved by using a modified Cayley graph whose bisection bandwidth scales linearly with the number of processors. The custom interconnect later proved to be too expensive, and for the next generation XMT, Cray decided to use a 3D torus interconnect instead. This move made the XMT system more economically accessible, but it also sacrificed scalability for applications with high bandwidth requirements [144].

The MultiThreaded Graph Library (MTGL) [30] was originally designed to facilitate the development of graph applications on massively multithreaded machines of Cray, namely MTA-2 and XMT. Later, it was extended to run on the mainstream shared-memory and multicore architectures as well [23]. The MTGL is a significant step towards an extendible and generic parallel graph library. It will certainly be interesting to quantify the abstraction penalty paid due to its

generality. As of now, only preliminary performance results are published for MTGL.

The Small-world Network Analysis and Partitioning (SNAP) [145] framework contains algorithms and kernels for exploring large-scale graphs. It is a collection of different algorithms and building blocks that are optimized for small-world networks. It combines shared-memory thread level parallelism with state-of-the-art algorithm engineering for high performance. The graph data can be represented in a variety of different formats depending on the characteristics of the algorithm that operates on it. Its performance and scalability is high for the reported algorithms, but a head-to-head performance comparison with PBGL and GAPDT is not available.

Both MTGL and SNAP are great toolboxes for graph computations on multithreaded architectures. For future extensions, MTGL relies on the visitor concept it inherits from the PBGL, while SNAP relies on its own kernel implementations. Both software architectures are maintainable as long as the target architectures remain the same.

Algorithms on massive graphs with billions of vertices and edges require hundreds of gigabytes of memory. For a special purpose supercomputer such as XMT, memory might not be a problem; but commodity shared-memory architectures have limited memory. Thus, MTGL or SNAP will likely to find limited use in com-

modity architectures without either distributed memory or out-of-core support. Experimental studies show that an out-of-core approach [8] is two orders of magnitude slower than an MTA-2 implementation for parallel breadth-first search [20]. Given that many graph algorithms, such as clustering and betweenness centrality, are computationally intensive, out-of-core approaches are infeasible. Therefore, distributed memory support for running graph applications of general purpose computers is essential. Neither MTGL or SNAP seem easily extendible to distributed memory.

#### 1.3 The Case for Primitives

Large scale software development is a formidable task that requires an enormous amount of human expertise, especially when it comes to writing software for parallel computers. Writing every application from scratch is an unscalable approach given the complexity of the computations and the diversity of the computing environments involved. Raising the level of abstraction of parallel computing by identifying the algorithmic commonalities across applications is becoming a widely accepted path to solution for the parallel software challenge [13, 44]. Primitives both allow algorithm designers to think on a higher level of abstraction, and help to avoid duplication of implementation efforts.

Achieving good performance on modern architectures requires substantial programmer effort and expertise. Primitives save programmers from implementing the common low-level operations. This often leads to better understanding of the mechanics of the computation in hand because carefully designed primitives can usually handle seemingly different but algorithmically similar operations. Productivity of the application-level programmer is also dramatically increased as he or she can now concentrate on the higher-level structure of the algorithm without worrying about the low level details. Finally, well-implemented primitives often outperform hand-coded versions. In fact, after a package of primitives proves to have widespread use, it is usually developed and tuned by the manifacturers for their own architectures.

### 1.3.1 A Short Survey of Primitives

Primitives have been successfully used in the past to enable many computing applications. The Basic Linear Algebra Subroutines (BLAS) for numerical linear algebra are probably the canonical example [136] of a successful primitives package. The BLAS became widely popular following the success of LAPACK [12]. The BLAS was originally designed for increasing modularity of scientific software, and LINPACK used it to increase the code sharing among projects [78]. LINPACK's use of the BLAS encouraged experts (preferably the vendors themselves)

implement its vector operations for optimal performance. Other than the efficiency benefits, it offered portability by providing a common interface for these subroutines. It also indirectly encouraged structured programming.

Later, as computers started to have deeper memory hierarchies and advances in microprocessors made memory access more costly than performing floating-point operations, BLAS Level 2 [81] and Level 3 [80] specifications were developed, in late 1980s. They emphasize blocked linear algebra to increase the ratio of floating-point operations to slow memory accesses. Although BLAS 2 and 3 had different tactics for achieving high performance, both followed the same strategy of packaging the commonly used operations and having experts provide the best implementations through performing algorithmic transformations and machine-specific optimizations. Most of the reasons for developing the BLAS package about four decades ago are valid for the general case for primitives today.

Google's MapReduce programming model [75], which is used to process massive data on clusters, is also of similar spirit. The programming model allows the user to customize two primitives: map and reduce. Although two different customized map operations are likely to perform different computations semantically, they perform similar tasks algorithmically as they both apply a (user-defined) function to every element of the input set. A similar reasoning applies for the reduce operation.

Guy Blelloch advocates the use of prefix sums (scan primitives) for implementing a wide range of classical algorithms in parallel [32]. The data-parallel language NESL is primarily based on these scan primitives [33]. Scan primitives have also been ported to manycore processors [117] and found widespread use.

### 1.3.2 Graph Primitives

In contrast to numerical computing, a scalable software stack that eases the application programmer's job does not exist for computations on graphs. Some of the primitives we surveyed can be used to implement a number of graph algorithms. Scan primitives are used for solving the maximum flow, minimum spanning tree, maximal independent set, and (bi)connected components problems efficiently. On the other hand, it is possible to implement some clustering and connected components algorithms using the MapReduce model, but the approaches are quite unintuitive and the performance is unknown [64]. Our thesis fills a crucial gap by providing primitives that can be used for traversing graphs. By doing so, the Combinatorial BLAS can be used to perform tightly-coupled, such as shortest paths based and diffusion based, computations on graphs.

We consider the shortest paths problem on dense graphs in Chapter 7. By using an unorthodox blocked recursive elimination strategy together with a highly optimized matrix-matrix multiplication, we achieve up to 480 times speedup over

a standard code running on a single CPU. The conclusion of that pilot study is that carefully chosen and optimized primitives, such as the ones found in the combinatorial BLAS, are the key to achieve high performance.

## 1.4 The Case for Sparse Matrices

The connection between graphs and sparse matrices was first exploited for computation five decades ago in the context of Gaussian elimination [160]. Graph algorithms have always been a key component in sparse matrix computations [65, 101]. In this thesis, we turn this relationship around and use sparse matrix methods to efficiently implement graph algorithms [103, 105]. Sparse matrices seemlessly raise the level of abstraction in graph computations by replacing the irregular data access patterns with more structured matrix operations.

The sparse matrix infrastructures of the Matlab, Star-P, Octave and R programming languages [94] allow for work-efficient implementations of graph algorithms. Star-P is a parallel dialect of Matlab that includes distributed sparse matrices, which are distributed across processors by blocks of rows. The efficiency of graph operations results from the efficiency of sparse matrix operations. For example, both Matlab and Star-P follow the design principle that the storage of a sparse matrix should be proportional to the number of nonzero elements

and the running time for a sparse matrix algorithm should be proportional to the number of floating point operations required to obtain the result. The first principle ensures storage efficiency for graphs while the second principle ensures work efficiency.

Graph traversals, such as breadth-first search and depth-first search, are the natural tools for designing graph algorithms. Traversal-based algorithms visit vertices following the connections (edges) between them. When translated into actual implementation, this traditional way of expressing graph algorithms poses performance problems in practice. Here, we summarize these challenges, which are examined in detail by Lumsdaine et al. [143], and provide a sparse matrix perspective for tackling these challenges.

Traditional graph computations suffer from poor locality of reference due to their irregular access patterns. Graphs computations in the language of linear algebra, on the other hand, involve operations on matrix blocks. Matrix operations give opportunities for the implementer to restructure the computation in a way that would exploit the deep memory hierarchies of modern processors.

Implementations for parallel computers also suffer from unpredictable communication patterns because they are mostly data driven. Consider an implementation of parallel breadth-first search in which the vertices are assigned to processors. The owner processor finds the adjacency of each vertex in the current frontier, in order to form the next frontier. The adjacent vertices are likely to be owned by different processors, resulting in communication. Since the next frontier is not known in advance, the schedule and timing of this communication is also not known in advance. On the other hand, sparse linear algebra operations have fixed communication schedules that are built into the algorithm. Although sparse matrices are no panacea for irregular data dependencies, the operations on them can be restructured to provide more opportunities for optimizing the communication schedule such as overlapping communication with computation and pipelining.

Both in serial and parallel settings, the computation time is dominated by the latency of fetching the data (from slow memory in serial case and from remote processor's memory in parallel case) to local registers, due to fine grained data accesses of graph computations. Massively multithreaded architectures tolerate this latency by keeping lots of outstanding memory requests on the fly. Sparse matrix operations have coarse-grained parallelism, which is much less affected by latency costs.

## 1.5 Definitions and Conventions

Let  $\mathbf{A} \in \mathbb{S}^{m \times n}$  be a sparse rectangular matrix of elements from an arbitrary semiring  $\mathbb{S}$ . We use  $nnz(\mathbf{A})$  to denote the number of nonzero elements in  $\mathbf{A}$ . When the matrix is clear from context, we drop the parenthesis and simply use nnz. For sparse matrix indexing, we use the convenient Matlab® colon notation, where  $\mathbf{A}(:,i)$  denotes the ith column,  $\mathbf{A}(i,:)$  denotes the ith row, and  $\mathbf{A}(i,j)$  denotes the element at the (i,j)th position of matrix  $\mathbf{A}$ . For one-dimensional arrays,  $\mathbf{a}(i)$  denotes the ith component of the array. Sometimes, we abbreviate and use nnz(j) to denote the number of nonzeros elements in the jth column of the matrix in context. Array indices are 1-based throughout this thesis, except where stated otherwise. We use flops( $\mathbf{A} op \mathbf{B}$ ), pronounced "flops", to denote the number of nonzero arithmetic operations required by the operation  $\mathbf{A} op \mathbf{B}$ . Again, when the operation and the operands are clear from context, we simply use flops. To reduce notational overhead, we take each operation's complexity to be at least one, i.e. we say  $O(\cdot)$  instead of  $O(\max(\cdot, 1))$ .

For testing and analysis, we have extensively used three main models: the R-MAT model, the Erdős-Rényi random graph model, and the regular 3D grid model. We have frequently used other matrices for testing, which we will explain in detail in their corresponding chapters.

## 1.5.1 Synthetic R-MAT Graphs

The R-MAT matrices represent the adjacency structure of scale-free graphs, generated using repeated Knonecker products [56, 140]. R-MAT models the behavior of several real-world graphs such as the WWW graph, small world graphs, and citation graphs. We have used an implementation based on Kepner's vectorized code [16], which generates directed graphs. Unless otherwise stated, R-MAT matrices used in our experiments have an average of degree of 8, meaning that there will be approximately 8 n nonzeros in the adjacency matrix. The parameters for the generator matrix are a = 0.6, and b = c = d = 0.13. As the generator matrix is 2-by-2, R-MAT matrices have dimensions that are powers of two. An R-MAT graph with **scale** l has  $n = 2^l$  vertices.

# 1.5.2 Erdős-Rényi Random Graphs

An Erdős-Rényi random graph G(n,p) has n vertices, each of the possible  $n^2$  edges in the graph exists with fixed probability p, independent of the other edges [88]. In other words, each edge has an equally likely chance to exist. A matrix modeling the Erdős-Rényi graph G(n,p) is expected to have with  $n^2/p$  nonzeros, independently and identically distributed (i.i.d.) across the matrix. Erdős-Rényi random graphs can be generated using the sprand function of MAT-LAB.

## 1.5.3 Regular 3D Grids

As the representative of regular grid graphs, we have used matrices arising from graphs representing the 3D 7-point finite difference mesh (grid3d). These input matrices, which are generated using the MATLAB Mesh Partitioning and Graph Separator Toolbox [103], are highly structured block diagonal matrices.

## 1.6 Contributions

This thesis presents the combinatorial BLAS, a parallel software library that consists of a set of sparse matrix primitives. The combinatorial BLAS enables rapid parallel implementation of graph algorithms through composition of primitives. The development of this work has four main contributions.

The first contribution is the analysis of important combinatorial algorithms to identify the linear-algebraic primitives that serve as the workhorses of these algorithms. Early work on identifying primitives was explored in the relevant chapters [92, 168] of an upcoming book on Graph Algorithms in the Language of Linear Algebra [127]. In short, the majority of traditional and modern graph algorithms can be efficiently written in the language of linear algebra, except for algorithms whose complexity depends on a priority queue data structure. Although we will not be duplicating those efforts, non-exclusive list of graph algorithms that

are represented in the language of matrices, along with detailed pseudocodes, can be found in various chapters of this thesis.

The second contribution is the design, analysis, and implementation of key sparse matrix primitives. Here we take both theory and practice into account by providing practically useful algorithms with rigorous theoretical analysis. Chapter 2 provides details on implementing key primitives using sparse matrices. It surveys a variety of sequential sparse matrix storage formats, pinpointing their advantages and disadvantages for the primitives at hand. Chapter 3 presents novel algorithms for the least studied and the most important primitive in the combinatorial BLAS: Generalized sparse matrix-matrix multiplication (SpGEMM). The work in this chapter mainly targets scalability on distributed memory architectures.

The third contribution is software development and performance evaluation. The implementation details and performance enhancing optimizations for the SpGEMM primitive is separately analyzed in the last two sections of Chapter 3. These sections also report on the performance of the SpGEMM primitive on various test matrices. Chapter 4 explains the interface design for the combinatorial BLAS in detail. The whole combinatorial BLAS library is evaluated using two important graph algorithms, in terms of both performance and ease-of-use, in Chapter 5. Chapter 6 (like Chapter 3) provide another detailed example of op-

timizing primitives, this time sparse matrix-vector and sparse matrix-transposevector operations on multicore architectures.

The first three contributions are incidentally typical components of a research project in combinatorial scientific computing [119], except that the roles of problems and solutions are swapped. In other words, we are solving a combinatorial problem using matrix methods instead of solving a matrix problem using combinatorial methods.

The last contribution is our pilot studies on emerging architectures. In the context of this thesis, the contributions in Chapters 6 and 7, apart from being important in themselves, should also be seen as seed projects evaluating the feasibility of extending our work to a complete combinatorial BLAS implementation on GPU's and shared-memory systems.

# Chapter 2

# Implementing Sparse Matrices for Graph Algorithms

#### Abstract

We review and evaluate storage formats for sparse matrices in the light of the key primitives that are useful for implementing graph algorithms on them. We present complexity results of these primitives on different sparse storage formats both in the RAM model and in the I/O model. RAM complexity results were known except for the analysis of sparse matrix indexing. On the other hand, most of the I/O complexity results presented are new. The paper focuses on different variations of the triples (coordinates) format and the widely used compressed sparse formats (CSR/CSC). For most primitives, we provide detailed pseudocodes for implementing them on triples and CSR/CSC.

# 2.1 Introduction

The choice of data structure is one of the most important steps in algorithm design and implementation. Sparse matrix algorithms are no exception. The representation of a sparse matrix not only determines the efficiency of the algorithm that operates on it, but also influences the algorithm design process.

Given this bidirectional relationship, this chapter reviews and evaluates existing sparse matrix data structures with key primitives in mind. In the case of array-based graph algorithms, these primitives are sparse matrix-vector multiplication (SpMV), sparse matrix-matrix multiplication (SpGEMM), sparse matrix indexing/assignment (SpRef/SpAsgn), and sparse matrix addition (SpAdd). The administrative overheads of different sparse matrix data structures, both in terms of storage and processing, are also important and are exposed throughout the chapter.

One of the traditional ways to analyze the computational complexity of a sparse matrix operation is by counting the number of floating point operations performed. This is similar to analyzing algorithms according to their RAM complexities [7]. As memory hierarchies became dominant in computer architectures, the I/O complexity (also called the cache complexity) of a given algorithm became as important as its RAM complexity. Aggarwal and Vitter [6] roughly defines the I/O complexity of an algorithm as the number of block memory transfers it makes between the fast and slow memories. Cache performance is especially important for sparse matrix computations due to their irregular nature and low ratio of flops to memory access. Another approach to hiding the memory-processor speed gap is to use massively multithreaded architectures such as Cray's XMT [91]. However, these architectures have limited availability and high costs at present.

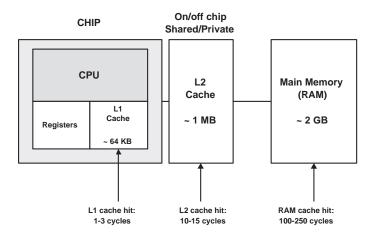

In many popular I/O models, only two levels of memory are considered for simplicity: a fast memory, and a slow memory. The fast memory is called cache and the slow memory is called disk, but the analysis is valid at different levels of memory hierarchy with appropriate parameter values. Both levels of memories are partitioned into blocks of size L, usually called the cache line size. The size of the fast memory is denoted by Z. If data needed by the CPU is not found in the fast memory, a cache miss occurs, and the memory block containing the needed data is fetched from the slow memory. One exception to these two-level I/O models is the uniform memory hierarchy of Alpern et al. [11], which views the computer's memory as a hiearchy of increasingly large memory modules. Figure 2.1 shows a simple memory hierarchy with some typical latency values as of 2006. Meyer et al. provide a contemporary treatment of algorithmic implications of memory hiearchies [150].

We present the computational complexity of algorithms in the RAM model as well as the I/O model. However, instead of trying to come up with the most I/O efficient implementations, we analyze the I/O complexities of the most widely used implementations, which are usually motivated by the RAM model. There are two reasons for this approach. First, I/O optimality is still an open problem for some of the key primitives presented in this chapter. Second, I/O efficient

implementations of some key primitives turn out to be suboptimal in the RAM model with respect to the amount of work they do.

We use  $scan(\mathbf{A}) = \lceil nnz(\mathbf{A})/L \rceil$  as an abbreviation for the I/O complexity of examining all the nonzeros of matrix  $\mathbf{A}$  in the order that they are stored.

Now, we state two crucial assumptions that are used throughout this chapter.

**Assumption 1.** A sparse matrix with dimensions  $m \times n$  has  $nnz \geq m, n$ . More formally,  $nnz = \Omega(n, m)$

Assumption 1 simplifies the asymptotic analysis of the algorithms presented in this chapter. It implies that when both the order of the matrix and its number of nonzeros are included as terms in the asymptotic complexity, only nnz is pronounced. While this assumption is common in numerical linear algebra (it is required for full rank), in some parallel graph computation it may not hold. In this chapter, however, we use this assumption in our analysis. In Chapter 3 (Section 3.2.1), we present an SpGEMM algorithm specifically designed for hypersparse matrices, with nnz < n, m.

**Assumption 2.** The fast memory is not big enough to hold data structures of O(n) size, where n is the matrix dimension.

In most settings, especially for sparse matrices representing graphs,  $nnz = \Theta(n)$ , which means that O(n) data structures are asymptotically in the same order

Figure 2.1: A typical memory hierarchy (approximate values as of 2006, partially adapted from Hennessy and Patterson [120], assuming a 2 Ghz processor)

as the whole problem. Assumption 2 is also justified when the fast memory under consideration is either the L1 or L2 cache. Out-of-order CPUs can generally hide memory latencies from L1 cache misses, but not L2 cache misses [120]. Therefore, it is more reasonable to treat the L2 cache as the fast memory and RAM (main memory) as the slow memory. The largest sparse matrix that fills the whole machine RAM (assuming the triples representation that occupies 16 bytes per nonzero, and a modern system with 1 MB L2 cache and 2 GB of RAM) has  $2^{31}/16 = 2^{27}$  nonzeros. Such a square sparse matrix, with an average of 8 nonzeros per column, has dimensions  $2^{24} \times 2^{24}$ . A single dense vector of double-precision floating point numbers with  $2^{24}$  elements require 128 MB of memory, which is clearly much larger than the size of the L2 cache.

The rest of this chapter is organized as follows. Section 2.2 describes the key sparse matrix primitives. Section 2.3 reviews the triples/ coordinates representation, which is natural and easy to understand. The triples representation generalizes to higher dimensions [15]. Its resemblence to database tables will help us expose some interesting connections between databases and sparse matrices. Section 2.4 reviews the most commonly used compressed storage formats for general sparse matrices, namely compressed sparse row (CSR) and compressed sparse column (CSC). Section 2.5 discusses some other sparse matrix representations proposed in the literature, followed by a conclusion. We introduce new sparse matrix data structures in Chapters 3 and 6. These data structures, DCSC and CSB, are both motivated by parallelism.

We explain sparse matrix data structures progressively, starting from the least structured and most simple format (unordered triples) and ending with the most structured formats (CSR and CSC). This way, we provide motivation on why experts prefer to use CSR/CSC formats by comparing and contrasting them with simpler formats. For example, CSR, a dense collection of sparse row arrays, can also be viewed as an extension of the triples format enhanced with row indexing capabilities. Furthermore, many ideas and intermediate data structures that are used to implement key primitives on triples are also widely used with implementations on CSR/CSC formats.

# 2.2 Key Primitives

Most of the sparse matrix operations have been motivated by numerical linear algebra. Some of them are also useful for graph algorithms:

- 1. Sparse matrix indexing and assignment (SpRef/SpAsgn)

- 2. Sparse matrix-dense vector multiplication (SpMV)

- 3. Sparse matrix addition and other pointwise operations (SpAdd)

- 4. Sparse matrix-sparse matrix multiplication (SpGEMM)

SpRef is the operation of storing a submatrix of a sparse matrix in another sparse matrix ( $\mathbf{B} \leftarrow \mathbf{A}(\mathbf{p}, \mathbf{q})$ ), and SpAsgn is the operation of assigning a sparse matrix to a submatrix of another sparse matrix ( $\mathbf{B}(\mathbf{p}, \mathbf{q}) \leftarrow \mathbf{A}$ ). It is worth noting that SpAsgn is the only key primitive that mutates its sparse matrix operand in the general case<sup>1</sup>. Sparse matrix indexing can be quite powerful and complex if we allow  $\mathbf{p}$  and  $\mathbf{q}$  to be arbitrary vectors of indices. Therefore, this chapter limits itself to row-wise ( $\mathbf{A}(i,:)$ ), column-wise ( $\mathbf{A}(:,j)$ ), and element-wise ( $\mathbf{A}(i,j)$ ) indexing, as they find more widespread use in graph algorithms. SpAsgn also requires the matrix dimensions to match. For example, if  $\mathbf{B}(:,i) = \mathbf{A}$  where  $\mathbf{B} \in \mathbb{S}^{m \times n}$ , then  $\mathbf{A} \in \mathbb{S}^{1 \times n}$ .

<sup>&</sup>lt;sup>1</sup>While  $\mathbf{A} = \mathbf{A} \oplus \mathbf{B}$  or  $\mathbf{A} = \mathbf{A}\mathbf{B}$  may also be considered as mutator operations, these are just special cases when the output is the same as one of the inputs

```

\begin{aligned} \mathbf{C} : \mathbb{R}^{S(m \times n)} &= \text{InnerProduct-SpGEMM}(\mathbf{A} : \mathbb{R}^{S(m \times k)}, \mathbf{B} : \mathbb{R}^{S(k \times n)}) \\ 1 & \text{ for } i \leftarrow 1 \text{ to } m \\ 2 & \text{ do for } j \leftarrow 1 \text{ to } n \\ 3 & \text{ do } \mathbf{C}(i,j) \leftarrow \mathbf{A}(i,:) \cdot \mathbf{B}(:,j) \end{aligned}

```

Figure 2.2: Inner product formulation of matrix multiplication

```

\begin{aligned} \mathbf{C} : \mathbb{R}^{S(m \times n)} &= \text{OuterProduct-SpGEMM}(\mathbf{A} : \mathbb{R}^{S(m \times k)}, \mathbf{B} : \mathbb{R}^{S(k \times n)}) \\ 1 \quad \mathbf{C} \leftarrow 0 \\ 2 \quad \text{for } l \leftarrow 1 \text{ to } k \\ 3 \qquad \qquad \mathbf{do} \ \mathbf{C} \leftarrow \mathbf{C} + \mathbf{A}(:, l) \cdot \mathbf{B}(l, :) \end{aligned}

```

Figure 2.3: Outer-product formulation of matrix multiplication

SpMV is the most widely used sparse matrix kernel since it is the workhorse of iterative linear equation solvers and eigenvalue computations. A sparse matrix can be multiplied by a dense vector either on the right ( $\mathbf{y} \leftarrow \mathbf{A}\mathbf{x}$ ) or on the left ( $\mathbf{y}^{\mathsf{T}} \leftarrow \mathbf{x}^{\mathsf{T}}\mathbf{A}$ ). This chapter concentrates on the multiplication on the right. It is generally straightforward to reformulate algorithms that use multiplication on the left so that they use multiplication on the right. Some representative graph computations that use SpMV are page ranking (an eigenvalue computation), breadth-first search, the Bellman-Ford shortest paths algorithm, and Prim's minimum spanning tree algorithm.

SpAdd,  $\mathbf{C} \leftarrow \mathbf{A} \oplus \mathbf{B}$ , computes the sum of two sparse matrices of dimensions  $m \times n$ . SpAdd is an abstraction that is not limited to a particular summation

operator. In general, any pointwise binary scalar operation between two sparse matrices falls into this primitive. Examples include the MIN operator that returns the minimum of its operands, logical AND, logical OR, ordinary addition, and subtraction.

SpGEMM computes the sparse product  $\mathbf{C} \leftarrow \mathbf{AB}$ , where the input matrices  $\mathbf{A} \in \mathbb{S}^{m \times k}$  and  $\mathbf{B} \in \mathbb{S}^{k \times n}$  are both sparse. It is a common operation for operating on large graphs, used in graph contraction, peer pressure clustering, recursive formulations of all-pairs-shortest-path algorithms, and breadth-first search from multiple source vertices. Chapter 3 presents novel ideas for computing SpGEMM.

The computation for matrix multiplication can be organized in several ways. One common formulation uses inner products, shown in Figure 2.2. Every element of the product  $\mathbf{C}(i,j)$  is computed as the dot product of a row i of  $\mathbf{A}$  and a column j of  $\mathbf{B}$ . Another formulation of matrix multiplication uses outer products (Figure 2.3). The product is computed as a sum of k rank-one matrices. Each rank-one matrix is the outer product of a column of  $\mathbf{A}$  with the corresponding row of  $\mathbf{B}$ .

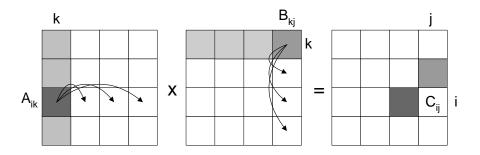

SpGEMM can also be organized so that  $\mathbf{A}$  and  $\mathbf{B}$  are accessed by row or columns, computing one row/column of the product  $\mathbf{C}$  at a time. Figure 2.5 shows the column-wise formulation where column j of  $\mathbf{C}$  is computed as a linear combination of the columns of  $\mathbf{A}$  as specified by the nonzeros in column j of  $\mathbf{B}$ .

```

\mathbf{C}: \mathbb{R}^{S(m \times n)} = \text{RowWise-SpGEMM}(\mathbf{A}: \mathbb{R}^{S(m \times k)}, \mathbf{B}: \mathbb{R}^{S(k \times n)})

1 for i \leftarrow 1 to m

2 do for l where \mathbf{A}(i, l) \neq 0

3 do \mathbf{C}(i, :) \leftarrow \mathbf{C}(i, :) + \mathbf{A}(i, l) \cdot \mathbf{B}(l, :)

```

Figure 2.4: Row-wise formulation of matrix multiplication

```

\begin{aligned} \mathbf{C} : \mathbb{R}^{S(m \times n)} &= \text{ColumnWise-SpGEMM}(\mathbf{A} : \mathbb{R}^{S(m \times k)}, \mathbf{B} : \mathbb{R}^{S(k \times n)}) \\ 1 & \text{ for } j \leftarrow 1 \text{ to } n \\ 2 & \text{ do for } l \text{ where } \mathbf{B}(l,j) \neq 0 \\ 3 & \text{ do } \mathbf{C}(:,j) \leftarrow \mathbf{C}(:,j) + \mathbf{A}(:,l) \cdot \mathbf{B}(l,j) \end{aligned}

```

Figure 2.5: Column-wise formulation of matrix multiplication

Figure 2.6 gives a diagram. Similarly, for the row-wise formulation, each row i of  $\mathbf{C}$  is computed as a linear combination of the rows of  $\mathbf{B}$  specified by nonzeros in row i of  $\mathbf{A}$  as shown in Figure 2.4.

# 2.3 Triples

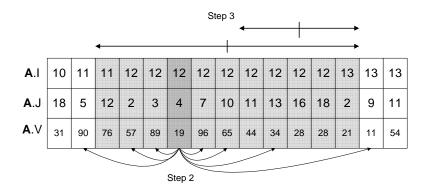

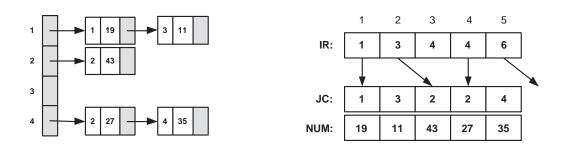

The simplest way to represent a sparse matrix is the *triples* (or *coordinates*) format. For each  $\mathbf{A}(i,j) \neq 0$ , the triple  $(i,j,\mathbf{A}(i,j))$  is stored in memory. Each entry in the triple is usually stored in a different array and the whole matrix  $\mathbf{A}$  is represented as three arrays  $\mathbf{A}.I$  (row indices),  $\mathbf{A}.J$  (column indices) and  $\mathbf{A}.V$  (numerical values), as illustrated in Figure 2.7. These separate arrays are

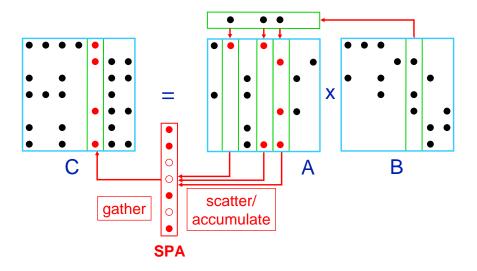

Figure 2.6: Multiplication of sparse matrices stored by columns. Columns of **A** are accumulated as specified by the non-zero entries in a column of **B** using a sparse accumulator or SPA. The contents of the SPA are stored in a column of **C** once all required columns are accumulated.

$$A = \begin{pmatrix} 19 & 0 & 11 & 0 \\ 0 & 43 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 27 & 0 & 35 \end{pmatrix}$$