INTERNATIONAL COMPUTER SCIENCE INSTITUTE

1947 Center St. • Suite 600 • Berkeley, California 94704-1198 • (510) 643-9153 • FAX (510) 643-7684

# T0 Engineering Data

Krste Asanović James Beck

$\mathrm{TR}\text{-}96\text{-}057$

December 1996

### Abstract

T0 (Torrent-0) is a single-chip fixed-point vector microprocessor designed for multimedia, human-interface, neural network, and other digital signal processing tasks. T0 includes a MIPS-II compatible 32-bit integer RISC core, a 1 Kbyte instruction cache, a high performance fixed-point vector coprocessor, a 128-bit wide external memory interface, and a byte-serial host interface. T0 implements the Torrent ISA described in a separate "Torrent Architecture Manual" technical report. This manual contains detailed information on the T0 vector microprocessor, including information required to build T0 into a system, instruction execution timings, and information on low level T0 software interfaces required for operating system support.

This work was supported by ONR URI Grant N00014-92-J-1617, ARPA contract number N0001493-C0249, NSF Grant No. MIP-9311980, and NSF PYI Award No. MIP-8958568NSF. Additional support was provided by ICSI.

ii

T0 Engineering Data. Version: 1.1.

# Contents

| 1        | Intr            | oducti | on                                           | 5  |

|----------|-----------------|--------|----------------------------------------------|----|

| <b>2</b> | CP              | U      |                                              | 7  |

|          | 2.1             | Opera  | ting Modes                                   | 7  |

|          | 2.2             | Emula  | ted instructions                             | 8  |

| 3        | $\mathbf{Syst}$ | tem Co | ontrol Coprocessor (CP0)                     | 9  |

|          | 3.1             | Host C | Communication Registers                      | 9  |

|          | 3.2             | Vector | Unit Interrupt Registers                     | 10 |

|          | 3.3             | Count  | er/Timer Registers                           | 11 |

|          | 3.4             | Excep  | tion Processing Registers                    | 12 |

|          |                 | 3.4.1  | Status Register                              | 12 |

|          |                 | 3.4.2  | Cause Register                               | 13 |

|          |                 | 3.4.3  | Exception Program Counter                    | 14 |

|          |                 | 3.4.4  | Bad Virtual Address                          | 14 |

|          | 3.5             | Proces | sor Revision Identifier                      | 15 |

| 4        | Vec             | tor Un | it Coprocessor 2                             | 16 |

|          | 4.1             | Vector | registers                                    | 16 |

|          | 4.2             | Vector | unit control registers                       | 16 |

|          |                 | 4.2.1  | VU Implementation and Revision Number (VCR0) | 17 |

|          |                 | 4.2.2  | Vector Length Register (VCR2)                | 18 |

|          |                 | 4.2.3  | VU Counter (VCR1)                            | 18 |

|          |                 | 4.2.4  | VU Condition Register (VCR4)                 | 18 |

|          |                 | 4.2.5  | VU Overflow Register (VCR8)                  | 19 |

|          |                 | 4.2.6  | VU Saturation Register (VCR12)               | 19 |

| 2 |                                                                          | T0 Engineering Data. Version:           | 1.1.                                                                                                       |

|---|--------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------|

| 5 | Inst                                                                     | ruction Encodings                       | 20                                                                                                         |

| 6 | Add                                                                      | ressing and Memory Protection           | <b>2</b> 4                                                                                                 |

| 7 | Res                                                                      | et, Interrupt, and Exception Processing | 25                                                                                                         |

|   | 7.1                                                                      | Reset                                   | 26                                                                                                         |

|   | 7.2                                                                      | Interrupts                              | 27                                                                                                         |

|   | 7.3                                                                      | Synchronous Exceptions                  | 28                                                                                                         |

| 8 | Pipe                                                                     | elines                                  | 29                                                                                                         |

|   | 8.1                                                                      | Instruction Fetch and Decode Pipeline   | 31                                                                                                         |

|   | 8.2                                                                      | CPU Execution Pipeline                  | 32                                                                                                         |

|   | 8.3                                                                      | VU Arithmetic Unit Execution Pipeline   | <b>3</b> 4                                                                                                 |

|   | 8.4                                                                      | VU Memory Unit Execution Pipeline       | 36                                                                                                         |

|   |                                                                          |                                         |                                                                                                            |

| 9 | Inst                                                                     | ruction Cache                           | 37                                                                                                         |

| 9 | <b>Inst</b><br>9.1                                                       | ruction Cache<br>I-cache organization   |                                                                                                            |

| 9 |                                                                          |                                         | 37                                                                                                         |

|   | 9.1<br>9.2                                                               | I-cache organization                    | 37                                                                                                         |

|   | 9.1<br>9.2<br>Inst                                                       | I-cache organization                    | 37<br>38<br><b>39</b>                                                                                      |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li></ul>              | I-cache organization                    | 37<br>38<br><b>39</b><br>39                                                                                |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li></ul>              | I-cache organization                    | 37<br>38<br><b>39</b><br>39<br>39                                                                          |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li></ul>              | I-cache organization                    | 37<br>38<br><b>39</b><br>39<br>39<br>40                                                                    |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li></ul>              | I-cache organization                    | <ul> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>42</li> </ul>                         |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li><li>10.2</li></ul> | I-cache organization                    | <ul> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>42</li> </ul>             |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li><li>10.2</li></ul> | I-cache organization                    | <ul> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>42</li> <li>43</li> </ul> |

|   | <ul><li>9.1</li><li>9.2</li><li>Inst</li><li>10.1</li><li>10.2</li></ul> | I-cache organization                    | <ul> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>42</li> <li>42</li> <li>43</li> </ul> |

| T0 | Eng         | ineering Data. Version: 1.1.             | 3  |

|----|-------------|------------------------------------------|----|

|    |             | 10.3.4 Vector Flag Register Data Hazards | 51 |

|    | 10.4        | CP0 Timing and Hazards                   | 53 |

|    | 10.5        | Instruction Cache Miss Timings           | 54 |

| 11 | Pin         | Out                                      | 56 |

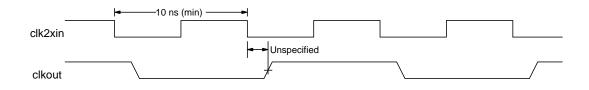

| 12 | Cloo        | cking                                    | 57 |

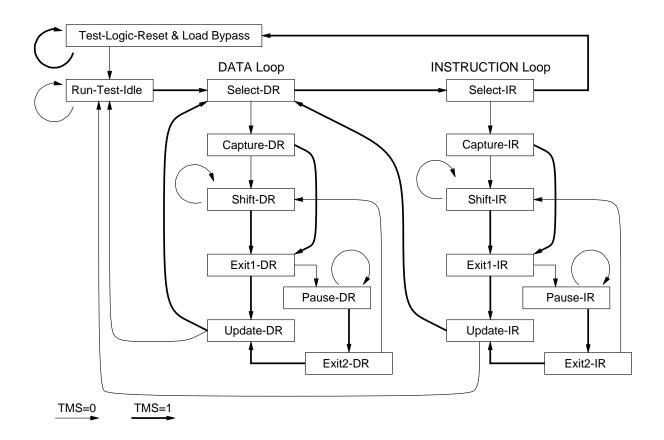

| 13 | SIP         |                                          | 58 |

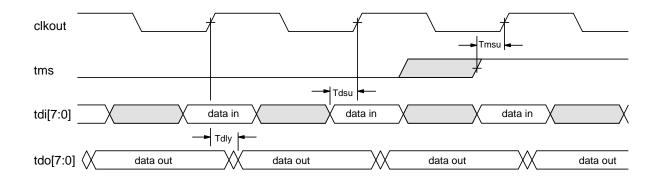

|    | 13.1        | Signal Pins                              | 58 |

|    | 13.2        | SIP Protocol                             | 58 |

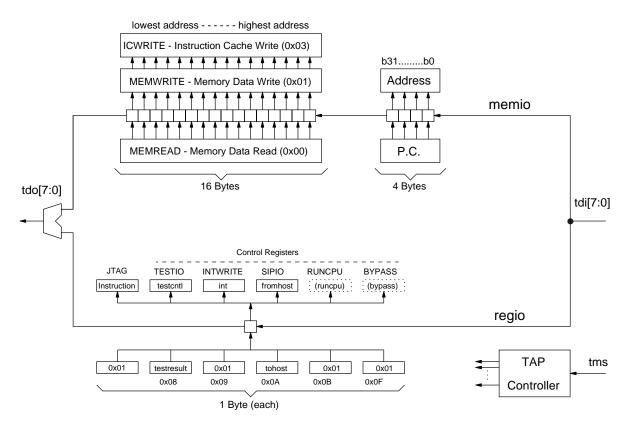

|    | 13.3        | SIP Shift Registers                      | 60 |

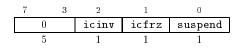

|    | 13.4        | SIP instructions                         | 61 |

|    |             | 13.4.1 BYPASS                            | 61 |

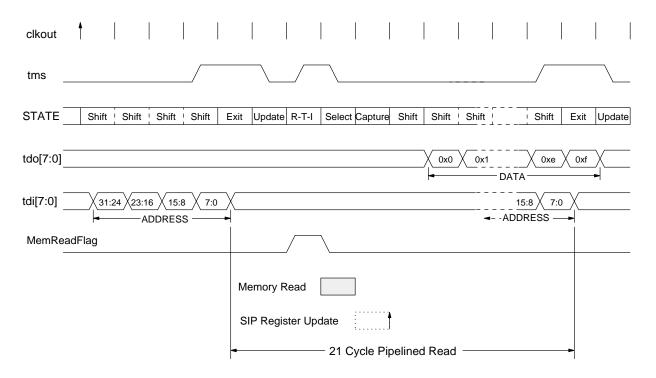

|    |             | 13.4.2 MEMREAD                           | 61 |

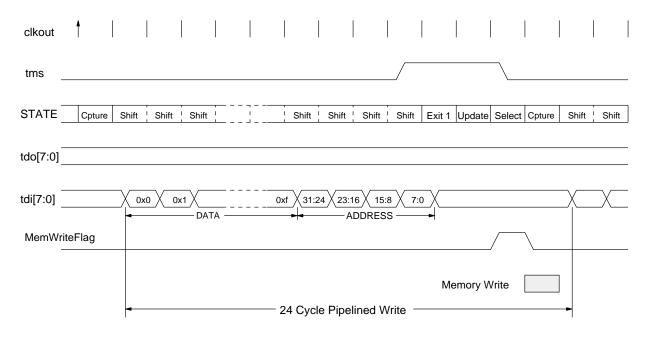

|    |             | 13.4.3 MEMWRITE                          | 63 |

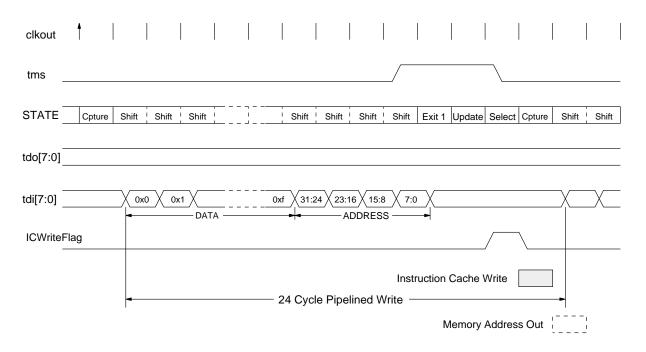

|    |             | 13.4.4 ICWRITE                           | 64 |

|    |             | 13.4.5 TESTIO                            | 65 |

|    |             | 13.4.6 SIPIO                             | 66 |

|    |             | 13.4.7 INTWRITE                          | 66 |

|    |             | 13.4.8 RUNCPU                            | 66 |

|    | 13.5        | SIP Single Step                          | 67 |

| 14 | Res         | et                                       | 68 |

| 15 | Exte        | ernal Interrupts                         | 68 |

| 16 | <b>TO</b> ] | Hardware Performance Monitor             | 69 |

|    | 16.1        | Scalar Unit HPM information              | 69 |

$\mathbf{71}$

| 16.2 Vector Unit HPM information        | 70 |

|-----------------------------------------|----|

| 16.3 Further Sources of HPM Information | 70 |

|                                         |    |

## 17 Memory Interface

## 1 Introduction

T0<sup>1</sup> is a vector microprocessor, the first implementation of the Torrent ISA. The Torrent Architecture Manual describes the Torrent ISA. This document is T0 specific and provides the engineering data required to build a T0 chip into a system, timing information for T0 instruction execution, and information on low level T0 software interfaces required for operating system support.

The overall structure of T0 is shown in Figure 1. The main components are a MIPS-II compatible RISC CPU, an instruction fetch unit with an instruction cache, a system coprocessor (CP0), a vector unit coprocessor (CP2), a 128-bit wide single cycle external memory interface, and a system interface port (SIP). In addition, T0 has two fast external interrupt pins, an internal counter/timer, and facilities for non-intrusive hardware performance monitoring.

T0 is a single chip microprocessor implemented in a  $1.0\mu m$  CMOS technology with a maximum clock frequency of 45 MHz. T0 can be run at lower clock rates to accomodate slower memory subsystems. The CPU is a MIPS-II compatible 32-bit integer datapath. The CPU is used for general scalar computation, and to support the vector unit by providing address generation and loop control. The instruction fetch unit manages a 1 KB instruction cache. The cache is direct-mapped with 64 lines each holding 4 instructions. The fast external memory interface together with a prefetching algorithm reduce instruction cache miss penalties. The maximum cache miss penalty is 3 cycles, and the minimum is 0 cycles. The system coprocessor is implemented as coprocessor 0. CP0 provides exception handling, a 32-bit counter/timer, instruction cache management, and SIP I/O registers.

The vector unit (VU) is added to the base MIPS-II architecture as coprocessor 2. The VU is a vector register machine and contains 16 vector registers. Fifteen of these registers, vr1-vr15, are general purpose and hold 32 elements each 32 bits wide. There is also a zero register, vr0, that is hardwired to return the value 0. There are two vector fixed point arithmetic functional units (VP0 and VP1), each with 8 separate datapaths and capable of completing up to 8 32-bit arithmetic or logical operations per cycle. The datapaths in VP0 can perform up to 8 16-bit×16-bit multiplies per cycle. VP1 does not include a multiplier, but otherwise the arithmetic units are identical. The arithmetic functional units can execute "arithmetic pipeline" instructions that chain up to 6 arithmetic and logical operations within a single instruction. There is a single vector memory functional unit (VMP), capable of sustaining up to 8 operand transfers per cycle. The external memory interface supports up to 4 GB of single cycle memory over a 128-bit data bus. Although T0 issues only one instruction per cycle, it overlaps parallel and pipelined execution in multiple functional units to sustain a computational rate of 720 MOP/s<sup>-2</sup> concurrently with a memory bandwidth of 360 M operands/s (720 MB/s).

The system interface port (SIP) has a single control signal and an 8b data path in each direction. Functions accessed through SIP include chip testing, interrupt signalling, instruction cache invalidation, instruction single step, and DMA. Peak DMA rates over SIP to and from T0 memory are 30 MB/s and 34 MB/s respectively at 45 MHz.

<sup>&</sup>lt;sup>1</sup>T0 is an abbreviation of Torrent-0.

<sup>&</sup>lt;sup>2</sup>Up to 4.3 GOP/s using "arithmetic pipeline" instructions.

Figure 1: T0 Structure.

Figure 2: T0 CPU registers.

T0 has a fully pipelined CPU that completes up to one instruction per cycle. T0 has the single MIPS architected branch delay slot. There is a two cycle load-use delay, but both delay slots are fully interlocked.

A hardware multiplier is provided that takes 18 cycles for a 32-bit×32-bit  $\rightarrow$  64-bit integer multiply. There is a hardware integer divider that takes 33 cycles to perform a 32-bit/32-bit divide returning both a 32-bit integer quotient and a 32-bit remainder. Integer multiplies and divides can proceed in parallel with other instructions provided the hi and 10 registers are not read.

All other CPU instructions apart from branches, loads, multiplies and divides, have single cycle latencies and are fully bypassed so that their results may be used in the following cycle.

In the Torrent architecture, vector memory accesses are unordered with respect to the CPU accesses, and with respect to each other. The MIPS-II SYNC instruction is used to guarantee the order of memory accesses. T0 processes all memory instructions in order, and the SYNC instruction has the effect of waiting for the current memory instruction to complete. This can be used to synchronize T0 memory accesses and host memory accesses over SIP, and also to wait for any pending vector memory address errors.

## 2.1 Operating Modes

T0 has two operating modes: *user* mode and *kernel* mode. The current operating mode is stored in the KUC bit in the CP0 **status** register. The CPU normally operates in user mode until an exception forces a switch into kernel mode. The CPU will then normally execute an exception handler in kernel mode before executing a Restore From Exception (RFE) instruction to return to user mode.

### 2.2 Emulated instructions

Several instructions in the MIPS-II instruction set are not implemented directly by T0. These instructions are trapped and can be emulated in software by the trap handler.

The misaligned load/store instructions, Load Word Left (LWL), Load Word Right (LWR), Store Word Left (SWL), and Store Word Right (SWR), are not implemented. A trap handler can emulate the misaligned access. Compilers for T0 should avoid generating these instructions, and should instead generate code to perform the misaligned access using multiple aligned accesses.

T0 is not designed to operate as part of a shared memory multiprocessor and so the multiprocessor synchronisation instructions, Load Linked (LL) and Store Conditional (SC), are not implemented.

The MIPS-II trap instructions, TGE, TGEU, TLT, TLTU, TEQ, TNE, TGEI, TGEIU, TLTI, TLTIU, TEQI, TNEI, are not implemented. The trap handler can perform the comparison and if the condition is met jump to the appropriate exception routine, otherwise resuming user mode execution after the trap instruction. Alternatively, these instructions may be synthesized by the assembler, or simply avoided by the compiler.

The floating point coprocessor is not present on T0. All MIPS-II coprocessor 1 instructions are trapped and can be emulated. For higher performance, compilers for T0 can directly generate calls to software floating point code libraries rather than emit coprocessor instructions. This will require a modified MIPS calling convention.

## 3 System Control Coprocessor (CP0)

The system control coprocessor on T0 contains a number of registers used for host communication, the counter/timer, and exception handling. These registers are read and written using the MIPS standard MFC0 and MTC0 instructions respectively. User mode can access the system control coprocessor only if the cu[0] bit is set in the status register. Kernel mode can always access CP0, regardless of the setting of the cu[0] bit. CP0 control registers are listed in Table 1.

| Number | Register   | Description                                 |

|--------|------------|---------------------------------------------|

| 0      | fromhost   | SIP input register.                         |

| 1      | tohost     | SIP output register.                        |

| 2      | vuepc      | Vector unit exception program counter.      |

| 3      | vubadvaddr | Vector unit bad virtual address.            |

| 4-7    |            | unused.                                     |

| 8      | badvaddr   | Bad virtual address.                        |

| 9      | count      | Counter/timer register.                     |

| 10     |            | unused.                                     |

| 11     | compare    | Timer compare register.                     |

| 12     | status     | Status register.                            |

| 13     | cause      | Cause of last exception.                    |

| 14     | epc        | Exception program counter.                  |

| 15     | prid       | Processor revision/implementation register. |

| 16-31  |            | unused.                                     |

Table 1: T0 CP0 control registers.

#### 3.1 Host Communication Registers

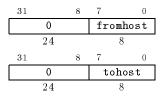

Figure 3: Fromhost and Tohost Register Formats.

There are two registers used for communicating and synchronizing with an external system over SIP. The **fromhost** register is an 8-bit read only register that contains a value written by the host system over SIP. The **tohost** register is an 8-bit read/write register that contains a value that can be read by the host system over SIP. The **tohost** register is cleared after reset to simplify host-T0 synchronization. Their format is shown in Figure 3.

## 3.2 Vector Unit Interrupt Registers

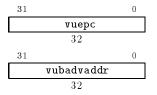

Figure 4: Vector Unit Exception PC and Bad Virtual Address Registers.

The vector memory functional unit can generate an asynchronous interrupt when it encounters an address error on any element of a vector memory instruction. The ip5 bit of the cause register is a sticky bit that is set by any vector address error, and can only be cleared by explicitly writing to the cause register. If both the im5 and iec bits of the status register are set, an interrupt will be generated whenever ip5 is set. Refer to Section 7 for further details on interrupt handlng.

The **vupec** register holds the program counter of the last vector memory instruction that had an address error and the **vubadvaddr** register holds the effective virtual address that caused the fault. These registers are updated on any vector address error, even if vector address error interrupts are not enabled. The **vuepc** register always points to the actual instruction that caused the fault, even if the instruction was in a branch delay slot.

Any vector address error stops execution of the current vector memory instruction, and leaves the state of the vector registers and the vector flag registers undefined. Execution cannot be restarted after a vector address error, and so this interrupt is usually considered fatal to the running process.

### 3.3 Counter/Timer Registers

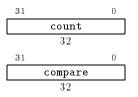

Figure 5: Count and Compare Registers.

T0 includes a counter/timer facility provided by the two coprocessor 0 registers count and compare. Both registers are 32 bits wide and are both readable and writeable. Their format is shown in Figure 5.

The count register contains a value that increments once every clock cycle. The count register is normally only written for initialization and test purposes. A timer interrupt is flagged in ip7 in the cause register when the count register reaches the same value as the compare register. The interrupt will only be taken if both im7 and iec in the status register are set. The timer interrupt flag in ip7 can only be cleared by writing the compare register. The compare register is usually only read for test purposes.

The count register is shadowed read-only in coprocessor 2 control register space as the vcount register.

### 3.4 Exception Processing Registers

A number of CP0 registers are used for exception processing.

### 3.4.1 Status Register

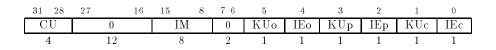

Figure 6: T0 Status Register Format

The status register is a 32-bit read/write register formatted as shown in Figure 6. The status register keeps track of the processor's current operating state.

The CU field has a single bit for each coprocessor indicating if that coprocessor is usable. Bits 29 and 31, corresponding to coprocessor's 1 and 3, are permanently wired to 0 as these coprocessors are not available in T0. Coprocessor 0 is always accessible in kernel mode regardless of the setting of bit 28 of the status register. Both bit 28 and bit 30 may be on simultaneously.

The IM field contains interrupt mask bits. Timer interrupts are disabled by clearing im7 in bit 15. SIP interrupts are disabled by clearing im6 in bit 14. Vector address error interrupts are disabled by clearing im5 held in bit 13. External interrupt 0 is disabled by clearing im4 in bit 12. External interrupt 1 is disabled by clearing im3 in bit 11. The other bits within the IM field are not used on T0 and should be written with zeros. Table 7 includes a listing of interrupt bit positions and descriptions.

The KUc/IEc/KUp/IEp/KUo/IEo bits form a three level stack holding the operating mode (kernel=0/user=1) and global interrupt enable (disabled=0/enabled=1) for the current state, and the two states before the two previous exceptions.

When an exception is taken, the stack is shifted left 2 bits and zero is written into KUc and IEc. When a Restore From Exception (RFE) instruction is executed, the stack is shifted right 2 bits, and the values in KUo/IEo are unchanged.

#### 3.4.2 Cause Register

| 31 | 30 | $29 \ 28$ | $27 \ 16$ | 15 | 8 | 7 | 6 2     | 1 0 |

|----|----|-----------|-----------|----|---|---|---------|-----|

| BD | 0  | CE        | 0         | IP |   | 0 | ExcCode | 0   |

| 1  | 1  | 2         | 12        | 8  |   | 1 | 5       | 2   |

Figure 7: T0 Cause Register Format

The cause register is a 32-bit register formatted as shown in Figure 7. The cause register contains information about the type of the last exception. Only the ip5 bit can be written, all other bits are read only.

The ExcCode field contains an exception type code. The values for ExcCode are listed in Table 2. The ExcCode field will typically be masked off and used to index into a table of software exception handlers.

| ExcCode | Mnemonic | Description                             |

|---------|----------|-----------------------------------------|

| 0       | Hint     | Host interrupt over SIP.                |

| 1       | Vint     | Vector unit address error interrupt.    |

| 2       | Tint     | Timer interrupt.                        |

| 4       | AdEL     | Address or misalignment error on load.  |

| 5       | AdES     | Address or misalignment error on store. |

| 6       | AdEF     | Address or misalignment error on fetch. |

| 8       | Sys      | Syscall exception.                      |

| 9       | Вр       | Breakpoint exception.                   |

| 10      | RI       | Reserved instruction exception.         |

| 11      | CpU      | Coprocessor Unusable.                   |

| 12      | Ov       | Arithmetic Overflow.                    |

| 18      | VUE      | Vector Unit exception.                  |

Table 2: T0 Exception Types.

If the Branch Delay bit (BD) is set, the instruction that caused the exception was executing in a branch delay slot and epc points to the immediately preceding branch instruction. Otherwise, epc points to the faulting instruction itself.

If the exception was a coprocessor unusable exception, then the Coprocessor Error field (CE) contains the coprocessor number. This field is undefined for any other exception.

The IP field indicates which interrupts are pending. Field ip7 in bit 15 flags a timer interrupt. Field ip6 in bit 14 flags an interrupt from the host over SIP. Flag ip5 in bit 13 flags a vector unit address error. Flag ip4 in bit 12 follows the external interrupt 0 pin, and flag ip3 in bit 11 follows the external interrupt 1 pin. The other IP bits are unused in T0 and should be ignored when read. Table 7 includes a listing of interrupt bit positions and descriptions.

#### 3.4.3 Exception Program Counter

Figure 8: EPC Register.

Epc is a 32-bit read only register formatted as shown in Figure 8. When an exception occurs, epc is written with the virtual address of the instruction that caused the exception, or if the instruction was executing in a branch delay slot, the address of the branch instruction immediately preceding the branch delay slot.

#### 3.4.4 Bad Virtual Address

Figure 9: BadVAddr Register.

Badvaddr is a 32-bit read only register formatted as shown in Figure 9. When a scalar memory address error generates an AdEL or AdES exception, badvaddr is written with the faulting virtual address. The value in badvaddr is undefined for other exceptions.

### 3.5 Processor Revision Identifier

| 31 | 16 | 15 | 8   | 7 | 0  |

|----|----|----|-----|---|----|

| 0  | 0  |    | Imp |   | ev |

| 16 |    | 8  |     |   | 8  |

Figure 10: Processor Revision Identifier Register Format.

The prid register is a 32-bit read only register that contains the implementation and revision number of the CPU. These values can be used by configuration and diagnostic software.

The prid register format is shown in Figure 10. Bits 15–8 define the implementation number, and bits 7–0 define the revision number. Bits 31–16 are reserved and return 0 on T0. The implementation number can be used by user software to detect changes in instruction set or performance. The revision number identifies mask revisions of T0.

Implementation field values are given in Table 3.

| Imp. Number | CPU      |

|-------------|----------|

| 0           | Τ0       |

| 1-255       | reserved |

Table 3: CPU Implementation types.

## 4 Vector Unit Coprocessor 2

## 4.1 Vector registers

T0 implements 16 vector registers, \$vr0-\$vr15. Vector registers \$vr1-\$vr15 are general purpose and each contain 32 32b elements. Vector register \$vr0 is hardwired to a vector containing 32 elements with value 0. Reads of \$vr0 return 0, and writes to \$vr0 are ignored. Instructions that attempt to use the unimplemented vector registers, \$vr16-\$vr31, cause a reserved instruction exception.

T0 has two vector arithmetic functional units, VP0 and VP1, and a single vector memory functional unit, VMP. Each functional unit can produce up to 8 results per clock cycle.

## 4.2 Vector unit control registers

The vector unit control registers are listed in Table 4. Any CFC2/CTC2 instruction that attempts to access an unimplemented vector control register will receive an illegal instruction exception.

| Number | Register | Description             |

|--------|----------|-------------------------|

| vcr0   | vrev     | Implementation/revision |

| vcr1   | vcount   | Counter                 |

| vcr2   | vlr      | Vector length           |

| vcr4   | vcond    | Vector condition flags  |

| vcr8   | vovf     | Vector overflow flags   |

| vcr12  | vsat     | Vector saturation flags |

Table 4: Vector unit control registers.

#### 4.2.1 VU Implementation and Revision Number (VCR0)

| 31 | 16 | 15  | 8 | 7   | 0 |

|----|----|-----|---|-----|---|

| 0  |    | Imp |   | Rev |   |

| 16 |    | 8   |   |     | 8 |

Figure 11: VU Implementation and Revision Register Format.

The **vrev** register is a 32-bit read only register that contains the implementation and revision number of the VU. These values can be used by configuration and diagnostic software.

The **vrev** register format is shown in Figure 11. Bits 15-8 define the implementation number, and bits 7-0 define the revision number. The implementation number can be used by user software to detect changes in instruction set or performance. The revision number identifies mask revisions of T0.

Implementation field values are given in Table 5.

| Imp. Number | Vector Unit |

|-------------|-------------|

| 0           | Τ0          |

| 1-255       | reserved    |

Table 5: VU Implementation types.

#### 4.2.2 Vector Length Register (VCR2)

| 31 | 8 | $7 \ 0$ |   |

|----|---|---------|---|

| 0  |   | vlr     |   |

| 24 |   | 8       | • |

Figure 12: Vector Length Register Format.

The length of a vector operation is specified in an 8-bit vector length register, vlr. If a vector instruction is issued when the value in vlr is 0, no operations are performed. If a vector instruction is issued when the value in vlr is greater than 32, a vector length error exception is raised.

Reads or writes of the vector length register do not affect vector instructions in progress.

### 4.2.3 VU Counter (VCR1)

Figure 13: Vector Count Register Format.

The VU count register, vcount, is a 32-bit read-only register that holds a cycle counter. It shadows the count register in coprocessor 0. The count value is incremented once per clock cycle regardless of host SIP activity, instruction cache misses, or interlocks.

#### 4.2.4 VU Condition Register (VCR4)

Figure 14: Vector Condition Register Format.

The VU condition register, vcond, is a 32-bit read/write register as shown in Figure 14.

The vcond register is only altered by vector set less than instructions, vector set equal instructions, and CTC2 writes of vcond. After execution of a vector comparison instruction, each bit of vcond holds the result of the comparison for each element of the destination vector register. Bit x holds the result of the comparison for element x.

#### 4.2.5 VU Overflow Register (VCR8)

| 31 |      | 0 |

|----|------|---|

|    | vovf |   |

|    | 32   |   |

Figure 15: Vector Overflow Register Format.

The VU overflow register, vovf, is a 32-bit read/write register as shown in Figure 15. The vovf register contains 32 sticky bits holding the overflow status for signed integer adds and subtracts.

The **vovf** register is only altered by vector signed add (ADD.yy) and vector signed subtract (SUB.yy) instructions, and control to coprocessor writes of **vovf**. If any result of a ADD.yy or SUB.yy instruction overflows, the corresponding bit of **vovf** is set. Bit x holds the overflow status of element x. The overflow bits can only be reset by a CTC2 write of **vovf**.

#### 4.2.6 VU Saturation Register (VCR12)

Figure 16: Vector Saturation Register Format.

The VU saturation register, vsat, is a 32-bit read/write register as shown in Figure 16. The vsat register contains 32 sticky bits holding the saturation status for fixed point adds (FXADD.yy), subtracts (FXSUB.yy), and multiplies (FXMUL.yy).

The vsat register is only altered by FXADD.yy, FXSUB.yy, and FXMUL.yy instructions, and CTC2 writes of vsat. If any result of a FXADD.yy, FXSUB.yy, or FXMUL.yy instruction saturates, the corresponding bit of vsat is set. Bit x holds the saturation status of element x. The saturation bits can only be reset by a CTC2 write of vsat.

## 5 Instruction Encodings

Figures 17, 18, and 19 detail the opcode decoding for T0. A key to the symbols appears below.

- \* Opcodes marked with an asterisk cause a reserved instruction exception.

- $\xi$  Opcodes marked with a xi are illegal but do not cause a reserved instruction exception.

- $\Phi$  Opcodes marked with a phi cause a coprocessor 1 unusable exception.

- $\delta$  Opcodes marked with a delta cause a coprocessor 2 unusable exception if the CpU2 bit in the status register is clear, otherwise they cause a reserved instruction exception.

- $\sigma$  Opcodes marked with a sigma cause a reserved instruction exception if opers (bit 10) is set.

- $\rho$  Opcodes marked with a rho cause a reserved instruction exception if the register number in rd doesn't match a coprocessor 2 control register as listed in Table 4.

- $\Theta$  Opcodes marked with a theta cause a coprocessor 3 unusable exception.

Figure 17: T0 CPU Instruction Encodings.

Figure 18: T0 Coprocessor 0 Instruction Encodings.

Figure 19: T0 Vector Instruction Encodings.

Figure 20: T0 virtual address space.

In kernel mode, the processor can access any address in the entire 4 GB virtual address space. In user mode, instruction fetches or scalar data accesses to the *kseg* segment are illegal and cause a synchronous exception. The AdEF exception is generated for an illegal instruction fetch, and AdEL and AdES exceptions are generated for illegal scalar loads and stores respectively. In user mode, vector data memory accesses to the *kseg* segment cause an asynchronous vector unit address interrupt to be flagged in **ip5** in the **cause** register. For both scalar and vector stores, no data memory will be written at the faulting address. A faulting vector memory operation will cause the state of the vector unit to become undefined.

There is no memory translation hardware on T0. Virtual addresses are directly passed as physical addresses to the external memory system. The external memory system may simply ignore unused high order address bits, in which case each physical memory address will be shadowed multiple times in the virtual address space.

On each memory cycle, T0 outputs information regarding the type (instruction/data, kernel/user, read/write) of each memory access as well as the physical memory address. This information can be used by an external memory protection system to provide finer grain memory protection. For example, user memory access may be restricted to a single shadow of the real physical memory. The external memory protection system can signal faults by interrupting T0.

## 7 Reset, Interrupt, and Exception Processing

There are three possible sources of disruption to normal program flow: reset, interrupts (asynchronous exceptions), and synchronous exceptions. Reset and interrupts occur asynchronously to the executing program and can be considered to occur *between* instructions. Synchronous exceptions occur *during* execution of a particular instruction. Synchronous exceptions for an instruction are checked at the start of the CPU Mp stage.

If more than one of these classes of event occurs on a given cycle, reset has higher priority, and all interrupts have priority over all synchronous exceptions. The tables below show the priorities of different types of interrupt and synchronous exception.

The flow of control is transferred to one of four separate reset, interrupt, and exception vectors, as shown in Table 6. Reset and the external interrupts have separate vectors. All other exceptions share a common vector with different exceptions distinguished by different values in the exccode field of the status register.

| Vector Address | Cause                               |

|----------------|-------------------------------------|

| 0x0000_1000    | Reset                               |

| 0x0000_1100    | Exceptions and internal interrupts. |

| 0x0000_1200    | External interrupt 0.               |

| 0x0000_1300    | External interrupt 1.               |

Table 6: T0 Reset, Exception, and Interrupt Vectors.

### 7.1 Reset

When the external reset is deasserted, the PC is reset to  $0x0000\_1000$  with kuc set to 0, and iec set to 0. The effect is to start execution at the reset vector in kernel mode with interrupts disabled. The tohost register is also set to zero to allow synchronization with the host system. The vector unit is idle. All other state is undefined.

A typical reset sequence is shown in Figure 21.

Figure 21: Example reset sequence.

#### 26

## 7.2 Interrupts

The five interrupts possible on T0 are listed in Table 7 in order of decreasing priority.

| Vector           | ExcCode   | Mnemonic | IM/IP index | Description            |

|------------------|-----------|----------|-------------|------------------------|

| Highest Priority |           |          |             |                        |

| 0x0000_1100      | 0         | Hint     | 6           | Host SIP interrupt.    |

| 0x0000_1100      | 1         | Vint     | 5           | Vector unit interrupt. |

| 0x0000_1100      | 2         | Tint     | 7           | Timer interrupt.       |

| 0x0000_1200      | undefined |          | 4           | External interrupt 0.  |

| 0x0000_1300      | undefined |          | 3           | External interrupt 1.  |

| Lowest Priority  |           |          |             |                        |

#### Table 7: T0 Interrupts.

All T0 interrupts are level triggered. For each interrupt there is an IP flag in the cause register that is set if that interrupt is pending, and an IM flag in the status register that enables the interrupt when set. In addition there is a single global interrupt enable bit, iec, that disables all interrupts if cleared. A particular interrupt can only occur if both IP and IM for that interrupt are set and iec is set, and there are no higher priority interrupts.

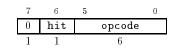

The host SIP flag IP6 follows the intfromhost bit within the int register in the SIP interface. This can be written by the host system over the SIP interface using the SIP INTWRITE instruction. Usually a protocol over the SIPIO registers within the interrupt handler informs the host that it can clear the interrupt flag.

The vector unit interrupt flag IP5 is set by any vector memory instruction address error. The instruction that caused the vector address error is killed, and the vector unit state becomes undefined. The flag bit is sticky and remains set unless explicitly cleared by a MTCO write to the cause register.

The timer interrupt flag IP7 is set when the value in the count register matches the value in the compare register. The flag can only be cleared as a side-effect of a MTC0 write to the compare register.

The two external interrupt flags, IP4 and IP3, are inverted clocked copies of the external input pads extintb[0] and extintb[1]. These provide a fast way to signal interrupts from external hardware.

When an interrupt is taken, the PC is set to the appropriate vector, and the KU/IE stack in the **status** register is pushed two bits to the left, with KUc and IEc both cleared to 0. This starts the interrupt handler running in kernel mode with further interrupts disabled. For internal interrupts the **exccode** field in the **cause** register is set to indicate the type of interrupt. The value in **exccode** is undefined for external interrupts.

The epc register is loaded with a restart address. If the instruction that took the interrupt was executing in a branch delay slot, the bd bit will be set and epc will point to the preceding branch, otherwise bd will be clear and epc will point to the instruction itself. The epc address can be used to restart execution after servicing the interrupt.

## 7.3 Synchronous Exceptions

Synchronous exceptions are listed in Table 8 in order of decreasing priority.

| ExcCode          | Mnemonic              | Description                             |

|------------------|-----------------------|-----------------------------------------|

| Highest Priority |                       |                                         |

| 6                | AdEF                  | Address or misalignment error on fetch. |

| 11               | CpU                   | Coprocessor Unusable.                   |

| 10               | RI                    | Reserved instruction exception.         |

| 8                | $\operatorname{Sys}$  | Syscall exception.                      |

| 9                | Bp                    | Breakpoint exception.                   |

| 12               | Ov                    | Arithmetic Overflow.                    |

| 18               | VUE                   | Vector Unit exception.                  |

| 4                | $\operatorname{AdEL}$ | Address or misalignment error on load.  |

| 5                | AdES                  | Address or misalignment error on store. |

| Lowest Priority  |                       |                                         |

Table 8: T0 Synchronous Exceptions.

After a synchronous exception, the PC is set to 0x0000\_1100. The stack of kernel/user and interrupt enable bits held in the status register is pushed left two bits, and both kuc and iec are set to 0.

The epc register is set to point to the instruction that caused the exception, unless that instruction is in a branch delay slot in which case it points to the preceding branch instruction. The bd bit in the cause register is set if the exception occured in a branch delay slot. The exccode field in the cause register is set to indicate the type of exception.

If the exception was a coprocessor unusable exception (CpU), the **ce** field in the **cause** register is set to the coprocessor number that caused the error. This field is undefined for other exceptions.

The overflow exception (Ov) can only occur for scalar ADDI, ADD, and SUB instructions.

The vector unit exception (VUE) only occurs for vector length errors. For VINS.S and VEXT.S instructions, the index register rd will contain the faulting length. For VEXT.V instructions, it is necessary to examine both the index register rd and the vlr register to determine the cause of the fault. For all other instructions, the vlr register will contain the faulting length.

If the exception was an address error on a scalar load or store (AdEL/AdES), the badvaddr register is set to the faulting address. The value in badvaddr is undefined for other exceptions.

28

## 8 Pipelines

Each T0 instruction is destined for execution in one of four pipelined execution units: the CPU, the vector memory functional unit (VMP), or one of the two vector arithmetic functional units (VP0 and VP1). The CPU pipeline is also used to process exceptions and interrupts for any vector instruction. Figure 22 illustrates the overall pipeline structure of T0.

All instructions first pass through the instruction fetch  $(\mathbf{F})$  and instruction decode  $(\mathbf{D})$  stages, before being dispatched to the appropriate execution unit.

The CPU has an additional 4 pipeline stages: execute  $(\mathbf{X})$ , memory access  $(\mathbf{M})$ , memory data align  $(\mathbf{N})$ , and result write-back  $(\mathbf{W})$ . The CPU can complete one integer instruction per cycle.

The vector memory functional unit has 8 parallel pipelines, segmented into 3 stages: register read  $(\mathbf{R})$ , memory access  $(\mathbf{M})$ , and register write-back  $(\mathbf{W})$ . The vector memory unit can complete up to 8 memory transfers per cycle.

Each of the two vector arithmetic functional units has 8 parallel pipelines, segmented into 4 stages: register read (**R**), execute stage 1 (**X1**), execute stage 2 (**X2**), and register write-back (**W**). Each vector arithmetic unit can produce 8 results per cycle. Within each arithmetic unit pipeline there are 6 cascaded arithmetic and logical operators. These can be combined in the arithmetic pipeline instructions to perform up to 6 cascaded arithmetic and logical operations in one cycle down the pipeline.

Each clock cycle is divided into two phases, p and n (clock low and clock high respectively). Pipe phases are written as  $\mathbf{Fp}$ ,  $\mathbf{Fn}$ ,  $\mathbf{Dp}$ ,  $\mathbf{Dn}$ , etc. The following sections describe the actions performed for each pipe phase in T0.

Figure 22: T0 Pipelines.

## 8.1 Instruction Fetch and Decode Pipeline

## Fp

• New program counter is selected and instruction's physical address is fed into the instruction cache decoders.

## $\mathbf{Fn}$

- Instruction cache returns indexed instruction and generates hit/miss signal.

- If memory port is free, send out instruction physical address to start prefetch of cache line.

## Dp

- Register specifiers sent to CPU register file read port decoders. Note must first decode whether this is a coprocessor operation to mux *rd* instead of *rs* into first read port decoder.

- Check for reserved instructions. Flag reserved instruction exception if necessary.

- Check for SYSCALL and BREAK instructions and flag appropriate exception.

- Perform dependency check on register operands. Calculate bypass control for CPU. Interlock if data hazard on vector operations.

- Check for structural hazard in vector units. Interlock execution if there is no suitable free vector unit.

- Decode CPU instruction. Calculate control for CPU datapath.

## $\mathbf{D}\mathbf{n}$

- Register file returns CPU registers. Sign-extend immediate and perform register bypassing.

- CPU ALU and address generator starts execution.

- Dispatch instruction to appropriate execution unit.

### 8.2 CPU Execution Pipeline

Хр

- Check for structural hazard on memory port. Interlock if this is a load/store and memory port is in use.

- Branch comparator evaluates early. If branch, select program counter in concurrent **Fp** phase.

- Complete execution of CPU ALU operation and address generator.

- If vector-scalar, or scalar-vector, operation, scalar operand sent to vector unit.

- If vector fixed-point operation, configuration register passed to vector control unit.

### Хn

- If load/store send physical address to external memory.

- Check ALU result for integer overflow. Flag arithmetic overflow exception if necessary.

- ALU results forwarded to **Dn** stage.

- Check for any enabled interrupts, and check all exceptions for this instruction. Raise exception flags as necessary for this instruction.

#### $\mathbf{M}\mathbf{p}$

- If any exception flags raised, take exception by killing instructions following in pipeline, jamming PC to exception vector in concurrent  $\mathbf{Fp}$  phase, and updating exception handling state.

- First phase of external memory access.

### $\mathbf{M}\mathbf{n}$

• Second phase of external memory access returns value into vector memory unit latches.

### Np

• Load data is aligned, and zero/sign-extended in vector memory unit.

## $\mathbf{N}\mathbf{n}$

- Load data is passed over scbus to scalar unit and forwarded to Dn stage for bypassing.

- Register write address passed to register file write port decoder.

## Wp

• Write back result to register file.

### $\mathbf{W}\mathbf{n}$

• This pipe stage intentionally left blank.

## 8.3 VU Arithmetic Unit Execution Pipeline

## $\mathbf{R}\mathbf{p}$

• Register specifiers passed to vector regfile address decoders.

### $\mathbf{Rn}$

- Vector register file reads next vector operands.

- Scalar value received from CPU.

- Configuration register information received from CPU.

- Instruction control lines decoded.

## X1p

- Mux vector-vector, vector-scalar, or scalar-vector operands into pipeline.

- Begin multiplier evaluation.

- Begin logic unit evaluation.

- Begin left shifter evaluation.

## X1n

- Complete multiplier evaluation.

- Complete logic unit evaluation.

- Complete left shifter evaluation.

- Sign-extend and mux adder inputs.

- Start adder evaluation.

## X2p

• Complete adder evaluation.

#### $\mathbf{34}$

## X2n

- Evaluate conditional move condition.

- Evaluate right shifter and sticky bit logic.

- Mux clipper input.

- Start clipper evaluation.

## Wp

- Complete clipper evaluation.

- Write clipper output to vector register file.

- Pass condition/overflow/saturation flags to CPU.

## $\mathbf{W}\mathbf{n}$

• Write condition/overflow/saturation flags in CPU.

## 8.4 VU Memory Unit Execution Pipeline

This section only describes scalar, contiguous and strided vector memory pipeline operations. Indexed operations have a more complicated pipeline scheme.

## Rp

- Register specifiers passed to vector regfile address decoders.

- $\bullet\,$  Memory address evaluated in concurrent CPU  $\mathbf{X}\mathbf{p}$  stage.

## $\mathbf{Rn}$

- Vector register file reads next vector operands.

- Scalar store or scalar insert value received from CPU.

## $\mathbf{M}\mathbf{p}$

• Mux store and vector extract operands out to memory crossbar.

## $\mathbf{Mn}$

- Complete drive of store data out to memory.

- Receive load data back from memory.

- Mux load data or vector extract data through crossbar.

## Wp

- Sign or zero extend load data.

- Write vector load data to vector register file.

## Wn

• Send scalar load data or scalar extract value to CPU.

### 36

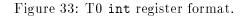

Figure 23: T0 Instruction Cache Read.

Note that the top four bits of the instruction address are ignored for the purposes of cache tag matching. To avoid cache aliasing, the maximum program size must be limited to 256 MB. Alternatively, explicit cache invalidate instructions can be issued before moving between aliased instruction addresses.

## 9.2 I-cache miss processing

On an I-cache miss a complete 16 byte line is read from external memory. In the worst case, the I-cache has a miss penalty of 3 cycles. When a miss is detected for an instruction during the F stage, the cache fetch state machine begins a 3 state miss service loop.

In the first miss cycle, the address of the cache line containing the missing instruction is output on the address bus. During the second miss cycle, the external memory returns the line containing the missing instruction. The third miss cycle is used to write back the new line into the instruction cache, and to forward the fetched instruction to the CPU decode stage.

To help reduce miss penalties, T0 also implements a simple prefetching scheme. Whenever the memory port is not busy with a host SIP access, a CPU load/store, a vector load/store, or a vector extract, the instruction address being fetched internally from the cache is also prefetched from the external memory. The prefetch address is output during the normal F cycle. If there is a miss, the fetch engine can omit the first cycle of the normal miss service loop thus reducing the cache miss penalty to 2 cycles.

To further reduce miss penalties, the fetch stage operates autonomously and can service miss requests while the D stage is interlocked or stalled on the memory pipeline. If instruction i is interlocked in the D stage, the F stage can service a miss on the instruction i + 1. In this case the miss penalty may be completely hidden behind the interlock stall. If the D stage is stalled waiting for a vector memory instruction to finish, the concurrent F stage I-cache miss servicing will only steal a single memory cycle from the ongoing vector memory access and can hide the rest of the 3 cycle miss latency behind the memory stall.

## **10** Instruction Timings

This section gives timing information for T0 instruction execution. T0 is fully interlocked with no architecturally visible hazards, except for the MIPS standard branch delay slot and the MIPS standard integer multiplier/divider hazards. T0 issues at most one instruction per cycle. All of T0 memory is constructed from pipelined SRAM, and hence there is no data cache, and no DRAM paging or refresh penalties. T0 has an instruction cache with miss penalties described below.

The timing information is separated into control hazards, structural hazards, and data hazards.

## 10.1 Control Hazards

The only control hazard on T0 is the single architected branch delay slot. The instruction following a branch is always executed, except after a not-taken branch likely instruction.

The MIPS-II branch likely instructions ensure that the branch delay slots can always be filled. If no independent instruction can be moved down from the preceding basic block to fill a normal branch delay slot, the instruction at the target of the branch can be moved into the delay slot and the branch changed to a branch likely.

## 10.2 Structural Hazards

A structural hazard occurs when an instruction cannot issue because one of the resources it requires for execution is in use by a previously issued instruction. There are three sources of such resource conflicts on T0: the memory pipeline, the two vector arithmetic pipelines, and the internal scalar bus (scbus). The memory pipeline is also used by the SIP port to read and write T0 memory, and by the instruction fetch unit for instruction cache refills.

Note that there are no structural hazards on the scalar multiplier/divider. There are data hazards that must be obeyed to correctly retrieve results, see Section 10.3.1.

In the following, the times that instructions occupy a resource are given in cycles. If an instruction occupies a resource for a single cycle, then a following instruction that requires the same resource can issue in the next cycle in a fully pipelined manner.

### 10.2.1 Memory Pipeline Structural Hazards

The memory pipeline handles external SIP memory requests, instruction cache refills, as well as scalar and vector memory operations. SIP memory accesses have highest priority, instruction cache refills have the next highest priority, and scalar and vector memory pipeline operations have the lowest priority. If there is a memory instruction in progress when a SIP access or instruction cache refill occurs, the complete vector unit will stall (the vector arithmetic units must also stall to preserve chaining). The CPU will only stall if the memory instruction in progress was a scalar load/store or a scalar insert/extract. If there are no memory requests on a given cycle, the instruction fetch unit prefetches the next instruction cache line.

SIP memory requests take one cycle in the memory pipeline. Section 13 contains detailed timing information of this access relative to SIP state machine activity.

Instruction cache refills take one cycle in the memory pipeline. This refill cycle is not required if there was an instruction prefetch during the fetch cycle that missed in the instruction cache.

Scalar load/store and scalar insert/extract instructions take one cycle in the memory pipeline.

Scalar sync instructions take one cycle in the memory pipeline. These are added to perform memory synchronization, and ordinarily a scheduler should not move other instructions across a sync.

Vector extracts run at different rates depending on the alignment of the extract index. If the extract index is a multiple of 8 (0, 8, 16, 24), then values can be read and written within the same datapath over a special bypass path without using the memory crossbar, and so can proceed at the rate of 8 32-bit elements per cycle. Otherwise, the extract must transfer elements using the memory crossbar which is limited to moving at most 4 32-bit elements per cycle. If the extract index is not a multiple of 4 and the vector to be extracted crosses an alignment boundary of 4 elements, then a further misalignment cycle is also required.

Contiguous vector memory instructions transfer up to 16 bytes per cycle between the memory data bus and 8 ports of the vector register file. Byte load/stores move up to 8 bytes per cycle; these are constrained by the number of ports on the vector register file. Halfword load/stores move 16 bytes per cycle, as 8 2-byte values. Word load/stores move 16 bytes per cycle, as 4 4-byte values.

Contiguous vector memory stores occupy the vector memory pipeline for a number of cycles equal to the number of naturally aligned blocks of memory that are written, where a block is 8 bytes for contiguous byte stores and 16 bytes for contiguous halfword and word stores.

Contiguous vector memory loads have a more complicated behaviour. The number of cycles is at least the number of naturally aligned blocks of memory that are read. However, the number of cycles is also bounded by the number cycles taken to write the vector register file. The vector register file can accept up to 8 operands per cycle, but all operands on the same register file row must be available before a register row write takes place. Register rows are 8 elements wide for byte and halfword loads, and 4 elements wide for word loads. For scheduling purposes, a simpler model for the cycle count can be used, just counting the number of memory blocks read. This figure will be at most 1 cycle too small.

The strided vector load/store instructions only load/store one operand per cycle. These take vlr cycles to complete.

The indexed vector loads load one operand per cycle but incur a 3 cycle latency to read the first address index. Indexed stores incur the same startup latency, but also require an extra cycle to read a group of 8 indices every 8 operands since there is only one vector register read port in the memory pipeline.

Table 9 summarizes the number of cycles that each memory pipeline operation occupies the pipeline.

| Operation                                         | Cycles in VMP                                                                                                                                   |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SIP MEMREAD, MEMWRITE, ICWRITE                    | 1                                                                                                                                               |

| I-cache refill                                    | 1                                                                                                                                               |

| Instruction                                       | Cycles in VMP                                                                                                                                   |

| lb, lbu, sb, lh, lhu, sh, lw, sw                  | 1                                                                                                                                               |

| sync                                              | 1                                                                                                                                               |

| vins.s, vext.s                                    | 1                                                                                                                                               |

| vext.v, index in $rd$ 8-aligned                   | [vlr/8]                                                                                                                                         |

| vext.v, index in $rd$ 4-aligned                   | $\lceil vlr/4 \rceil$                                                                                                                           |

| vext.v, index in $rd$ not 4-aligned               | $1 + \lceil v lr / 4 \rceil$                                                                                                                    |

| lbai.v, lbuai.v, sbai.v                           | $\lfloor \frac{\mathrm{rd} + (\mathrm{vlr} - 1)}{8} \rfloor - \lfloor \frac{\mathrm{rd}}{8} \rfloor + 1^{\dagger}$                              |

| lhai.v, lhuai.v, shai.v                           | $\lfloor \frac{\mathrm{rd}+2\times(\mathrm{vlr}-1)}{16}  floor - \lfloor \frac{\mathrm{rd}}{16}  floor + 1^{\dagger}$                           |

| lwai.v, swai.v                                    | $\lfloor \frac{\operatorname{rd} + 4 \times (\operatorname{vlr} - 1)}{16} \rfloor - \lfloor \frac{\operatorname{rd}}{16} \rfloor + 1^{\dagger}$ |

| lbst.v, lbust.v, lhst.v, lhust.v, lwst.v, sbst.v, | vlr                                                                                                                                             |

| shst.v, swst.v                                    |                                                                                                                                                 |

| lbx.v,lbux.v,lhx.v,lhux.v,lwx.v                   | 3 + vlr                                                                                                                                         |

| sbx.v, shx.v, swx.v                               | $2 + \lceil v lr/8 \rceil + v lr$                                                                                                               |

Table 9: Memory pipeline usage for T0 instructions. Vector instruction timing is affected by the vector length vlr, and vector contiguous load/store and vector extract timing is also affected by the alignment of the address or extract index in the rd register. <sup>†</sup> The model for contiguous loads has been simplified, and these can take an extra cycle in certain cases. See text for details.

### 10.2.2 Scalar Bus Structural Hazards

A single on-chip bus carries both coprocessor register values and vector indexed memory operation indices into the CPU. Indexed vector memory instructions occupy the scalar bus for their entire duration. Table 10 summarizes the scalar bus structural hazards.

| Instruction                         | Cycles on scbus                     |

|-------------------------------------|-------------------------------------|

| mfc0, cfc2                          | 1                                   |

| lbx.v, lbux.v, lhx.v, lhux.v, lwx.v | 3 + vlr                             |

| sbx.v, shx.v, swx.v                 | $2 + \lceil v lr / 8 \rceil + v lr$ |

Table 10: Scalar bus usage for T0 instructions. Vector instruction timing is affected by the vector length vlr.

## 10.2.3 Vector Arithmetic Structural Hazards

T0 has two vector arithmetic units VP0 and VP1. They are identical except that VP1 does not have a multiplier. All fxmul instructions must execute in VP0, but all other instructions can be executed in either pipeline. If both arithmetic units are free and a non-multiply instruction is decoded it will be issued to VP1 rather than VP0.

Each of the two vector arithmetic units completes 8 element operations per cycle. An arithmetic unit is busy for  $\lceil v lr/8 \rceil$  clock cycles when processing an arithmetic operation on a vector of length v lr.

### 10.3 Data Hazards

Instructions access memory in order of issue through a single memory pipeline, with memory access occurring in the same pipeline stage for all instructions, and so T0 has no data hazards on memory values. The only data hazards that can occur are on register values. Data hazards are of three types: Read-After-Write, Write-After-Read, and Write-After-Write.

A Read-After-Write (RAW) hazard is a true dependency, whereby an instruction must wait for one of its source registers to be written by a previous instruction. If the new instruction was not delayed, it would get an incorrect earlier value for its source operand.

A Write-After-Read (WAR) hazard is a false dependency, whereby an instruction cannot overwrite one of its destination registers until all previous instructions reading that register have obtained the original value. If the new instruction was not delayed, the old instructions would incorrectly get the new value for the register.

A Write-After-Write (WAW) hazard is a false dependency, whereby an instruction cannot overwrite one of its destination registers until all previous instructions that write the same register have finished. If the new instruction was not delayed, the old instructions would eventually finish and update the register, thus destroying the correct new value.

The following sections detail the data hazard timings for T0, with each section describing one group of registers: the CPU scalar registers including hi and lo, the vector length register vlr, the vector registers \$vr0-\$vr15, and the vector flag registers vcond, vovf, and vsat.

Data hazards occur between a pair of instructions, the instruction that first accesses a register and a second instruction that also wants to access the same register. In the tables that summarize data hazards, the first instruction to issue is listed in the rows and the second instruction in the columns. The values in the tables give the minimum number of delay cycles required between the two instructions to avoid the given data hazard on the given register. Except for the WAR hazard on the scalar multiplier/divider registers which must be scheduled, T0 has hardware interlocks that delay issue of a new instruction until all data hazards are resolved. Instruction scheduling is not required for correctness but only to improve performance. The number of delay cycles represents the minimum number of instructions that should be scheduled between dependent instructions to avoid an interlock. For example, scalar loads have two delay cycles. The sequence:

| lw t1, (a0) |   |     |          |           |        |

|-------------|---|-----|----------|-----------|--------|

| addiu t1, 1 | # | Тwо | hardware | interlock | cycles |

will incur two hardware interlock cycles. These interlock cycles may be usefully filled with two independent instructions as shown below:

lw t1, (a0)

addiu a0, 4 # Schedule other instructions in delay cycles.

slt t2, a0, a1

addiu t1, 1 # No interlock.

## 10.3.1 CPU Register Data Hazards

The result of most CPU instructions are available to the instruction issued in the next cycle. The only exceptions that cause RAW hazards are loads, scalar extracts, coprocessor register reads, and multiplies and divides.

Scalar memory loads (lb/lbu/lh/lhu/lw) have a latency of 3 cycles, and so 2 delay cycles. Reads from coprocessor registers (mfcO/cfc2) have 2 delay cycles. Scalar extracts from vector registers (vext.s) have 2 delay cycles. There are 17 delay cycles between the issue of an integer multiply (mult/multu) and the read of the result (mfhi/mflo). There are 32 delay cycles between the issue of an integer divide (div/divu) and the read of the result (mfhi/mflo). There is a single delay cycle between any mthi/mtlo instruction and any mfhi/mflo instruction, e.g., a mthi followed by a mflo will experience a single delay cycle even though the two instructions reference different registers.

To simplify the implementation, there is a false interlock on the scalar extract instruction **vext**.s: The scalar *rt* destination register of a **vext**.s instruction is interlocked as though it were a source register even though its value is not read.

All CPU ALU instructions read the register file early in the pipeline and write the register file late in the pipeline, so there are no WAR hazards for the general purpose registers.

The multiplier/divider registers are written early in the pipeline. A mfhi or mflo instruction cannot be followed by any instruction that changes the hi or lo registers (mthi/mtlo/mult/multu/div/divu). There is no hardware interlock for this WAR hazard, and there must be an intervening instruction for correct execution. Note there only needs to be a single instruction separating the read and write, not two as specified in the MIPS architecture.

There are no WAW hazards for the CPU general purpose registers or the multiplier/divider registers.

Tables 11–13 summarize the data hazards in the CPU registers.

| Reader           | Any GPR Read |

|------------------|--------------|

| Writer           |              |

| lb/lbu/lh/lhu/lw | 2            |

| mfc0/cfc2        | 2            |

| vext.s           | 2            |

Table 11: RAW hazards for CPU GPRs. Timings are given as number of delay cycles.

| Reader     | mfhi/mflo |

|------------|-----------|

| Writer     |           |

| mthi/mtlo  | 1         |

| mult/multu | 17        |

| div/divu   | 32        |

Table 12: RAW hazards for CPU hi/lo registers. Timings are given as number of delay cycles.

| Writer | mthi        | mtlo        | mult/multu/div/divu |

|--------|-------------|-------------|---------------------|

| Reader |             |             |                     |

| mfhi   | 1 mandatory | 0           | 1 mandatory         |

| mflo   | 0           | 1 mandatory | 1 mandatory         |

Table 13: WAR hazards for CPU hi/lo registers. Timings are given as number of delay cycles. There is no hardware interlock for these hazards and so the delay cycles are labeled *mandatory*. An instruction must be scheduled between the reader and writer for correct execution.

### 10.3.2 Vector Length Register Data Hazards

The current effective length of the vector registers is specified in the vector length register vlr, which is implemented as coprocessor 2 control register 2 and accessed with the MIPS standard ctc2/cfc2 instructions. This vector length is an implicit source operand of all vector instructions (other than scalar insert and extract). There are no RAW hazards on vlr for vector instructions; a ctc2 write of vlr will take effect on the next cycle. Scalar unit reads of vlr incur the same two cycle delay as any coprocessor register read.

There are no WAR or WAW hazards on vlr. Each vector functional unit copies the vector length at instruction issue, so the vector length register can be changed at any time without affecting ongoing vector operations.

### 10.3.3 Vector Register Data Hazards

The vector register file on T0 provides dedicated read and write ports for each operand of each vector functional unit, except that the vector memory pipeline uses the same read port for store indices and store data during indexed store operations. This removes register port access restrictions and so the only vector register hazards possible are due to RAW, WAR, or WAW dependencies on element values. T0 provides chaining with a fully multi-ported vector register file rather than by bypassing around functional units. This removes the need for a specified chain slot time, and also allows chaining of WAR and WAW hazards.

All vector arithmetic instructions behave identically as regards vector register data hazards, and so in the following they are referred to collectively as VALU instructions. All VALU instructions read vector source registers at the rate of 8 elements per cycle starting at element zero. They also write results to destination vector registers at the rate of 8 elements per cycle starting at element zero. Vector arithmetic instructions have a 3 cycle pipeline, with a 1/2 cycle to read vector registers, 2 cycles of execution, then a 1/2 cycle to write back vector register results. Dependent vector arithmetic instructions can be chained after 2 delay cycles.

Vector memory instructions have a wider range of behaviors depending on instruction class, data size, and address or extract index alignment. Contiguous vector loads and stores of bytes and halfwords can proceed at the rate of 8 elements per cycle, and so can be directly chained with arithmetic operations. Contiguous vector loads of bytes and halfwords have a single delay slot, plus an extra delay slot if the base address was not aligned.

Contiguous vector loads and stores of words can only transfer 4 elements per cycle. This prevents direct chaining with subsequent VALU instructions except towards the end of longer vectors. In this case the dependent VALU instructions can start when it is certain that the contiguous word memory operation can complete its vector register access before the VALU catches up.

Strided and indexed vector load/stores complete at the rate of one element per cycle. This prevents subsequent VALU instructions from chaining except for the last few cycles of long vectors when it is then certain that that strided or indexed operations will complete before the VALU instruction

### T0 Engineering Data. Version: 1.1.

catches up. Indexed operations have an extra start up penalty due to the time needed to first read index values into the address generator. Indexed stores share a single vector register read port between indices and store data, and so require an extra cycle every 8 cycles to read out the next group of 8 indices.

Scalar and vector extracts can read values from any position in a vector register depending on the value in a scalar index register. The index register value is not known at instruction issue time, and so the instruction dispatch unit must make the conservative assumption that values could be read from anywhere in the source vector register. These extract instructions cannot issue until all pending writes to the source vector register have completed.

Vector extract instructions write values at different rates depending on the extract index (see structural hazards above). When the extract index is 8-aligned, the vector extract instruction produces results at the rate of 8 elements per cycle and can be chained to arithmetic operations. When the extract index is not 8-aligned, values are produced at the rate of 4 elements per cycle and so direct chaining is not possible, except towards the end of long vectors as for contiguous word loads.

Scalar inserts into a vector register can potentially write to any location in its vector destination register depending on the value in a scalar index register. Since the index register value is not known at issue time, the instruction dispatch unit must make a conservative assumption and assume that it could write anywhere in the destination register. To prevent WAR and WAW hazards with previous vector arithmetic instructions, the insert instruction cannot issue until all ongoing arithmetic instructions have finished reading and writing their source and destination vector registers. To simplify the implementation the scalar insert instruction interlock logic does not compare vector register numbers and so will interlock until *all* ongoing vector arithmetic instructions complete, regardless of which vector registers they access.

The vector memory pipeline is one cycle shorter than the vector arithmetic pipelines. To avoid a WAW hazard, a vector memory pipeline operation cannot write the same destination vector register as an immediately preceding vector arithmetic instruction and is delayed for one cycle.

Tables 14–16 summarize the different hazard timings for the vector registers on T0.

| Reader<br>Writer                                  | VALU (vt/vd),<br>s_ai.v (vd),<br>s_st.v (vd),<br>l_x.v (vt indices),<br>s_x.v (vt indices) | <b>s_x.v</b><br>( <i>vd</i> data) | $\begin{array}{l} \texttt{vext.v} (vd), \\ \texttt{vext.s} (vd) \end{array}$ |

|---------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------|