## SYNCHRONIZATION AND ANTI-SYNCHRONIZATION OF CHUA'S OSCILLATORS VIA A PIECEWISE LINEAR COUPLING CIRCUIT

Damon A. Miller and Kristie L. Kowalski

Department of Electrical and Computer Engineering Western Michigan University

#### **ABSTRACT**

A chaotic associative memory may be constructed by coupling a network of Chua's circuits via piecewise linear conductances. Synchronization and anti-synchronization states are used to represent binary memory patterns. The chaotic network dynamics enable the memory to wander among patterns which have non-zero correlations with the input pattern. This paper describes two discrete circuits which may be used as the basis for implementing the coupling element as proposed in Jankowski et. al. [1995]. Initial coupling experiments support the proposed design approaches.

#### 1. INTRODUCTION

Chua's circuit is a nonlinear electronic chaotic oscillator. This circuit is easily constructed [1] and has been employed in a variety of applications [2], e.g. communication systems [3]. The chaotic associative memory architecture proposed in [4] uses a network of Chua's oscillators coupled via piecewise linear conductances. To the best of our knowledge this architecture has been studied only through simulation. An electronic implementation of this circuit offers the opportunity to investigate this architecture as a physical system. The only missing piece needed to build this memory is the piecewise linear coupling element. The basis for two designs of this circuit element are presented in this paper. One design has been built and partially tested. Initial experimental coupling results are consistent with the required circuit functionality.

#### 1.1. Associative Memory Architecture

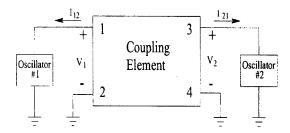

The associative memory architecture under consideration consists of a network of interconnected Chua's oscillators. The parameters of each oscillator are chosen to generate the "double scroll" attractor. The coupling element (described

Andrzej Lozowski

# Department of Electrical Engineering University of Louisville

Figure 1: Two coupled Chua's circuits

later) tends to force oscillators to become either synchronized or anti-synchronized. Binary patterns may be stored via specification of the coupling strengths between oscillators as determined by a Hebbian learning rule. Pattern retrieval is accomplished by coupling the input pattern to the network via a master free-running oscillator and observing the temporal response of each of the network oscillators. This response is characterized by temporary synchronization or anti-synchronization states which correspond to the stored patterns. The memory chaotically switches among those pattern memories which possess non-zero correlations with the input pattern. This form of coupling has also been used in a cellular neural network composed of locally coupled Lorenz systems [5].

## 1.2. Coupling Element Characteristics

In this paper we consider the interconnection of two Chua's oscillators using the coupling element proposed in [4] as shown in Figure 1. If N is the dimension of the stored binary patterns, the architecture requires N+1 oscillators (N for each memory pattern bit plus the master oscillator) coupled via N(N-1)/2+N coupling elements. Note that N of these coupling circuits are somewhat simplified since the N couplings to the master oscillator do not require both coupling currents (no current flows into the free-running master

This work was supported in part by a grant from the Michigan Space Grant Consortium.

oscillator). The coupling currents are [4]

$$I_{12} = g_{12} \\ \left[ V_2 + \operatorname{sign}(g_{12}) V_1 \left( \left| \frac{V_2}{V_1} \right| - \left| \frac{V_2}{V_1} + \operatorname{sign}(g_{12}) \right| \right) \right]$$

and

$$I_{21} = g_{21} \left[ V_1 + \operatorname{sign}(g_{21}) V_2 \left( \left| \frac{V_1}{V_2} \right| - \left| \frac{V_1}{V_2} + \operatorname{sign}(g_{21}) \right| \right) \right].$$

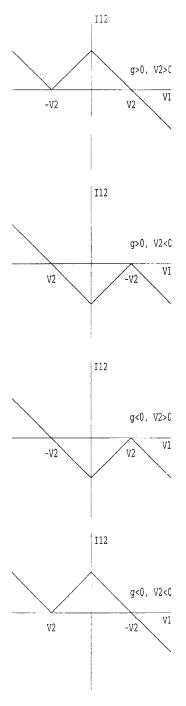

Figure 2 shows  $I_{12}$  for  $|g_{12}|=1$ . The conductance  $g=g_{12}=g_{21}$  determines the slopes of the linear segments and hence the coupling strength. For g<0,  $I_{12}=I_{21}$ , while for g>0,  $I_{12}=-I_{21}$  (not shown). Note that the current is zero when  $V_1$  is synchronized or anti-synchronized with  $V_2$  (i.e.  $|V_1|=|V_2|$ ). We have chosen to couple the voltages across the Chua's diodes in the oscillator circuits.

To illustrate the effect of this coupling element, consider the circuit of Figure 1 for g<0,  $V_2$  held at a constant positive voltage, and oscillator #1 replaced with a capacitor C. Figure 2 (g<0 and  $V_2>0$  case) indicates that  $I_{12}$  is, with the exception of one point, negative for  $V_1>-V_2$ . This discharges C and  $V_1$  approaches  $-V_2$ . For  $V_1< V_2$ , the coupling element provides a positive current, which tends to charge C, and thus  $V_1$  approaches  $-V_2$ . Hence the element forces  $V_1=-V_2$  as it should for g<0. Note that for  $V_1$  exactly equal to  $V_2$ , the coupling current is zero. This point is unstable as any negative perturbation of  $V_1$  will move  $V_1$  towards  $-V_2$ . The point  $V_1=-V_2$  is stable for this set of parameters.

## 2. COUPLING ELEMENT DESIGNS

We now consider two designs for the coupling circuit. First consider  $I_{12}$  as shown in Figure 2. The general shape of each of these curves is the same, consisting of (from left to right) a positive, a negative, and a positive region (note the definition of positive current in Figure 1). This characteristic may be generated by using piecewise linear characteristics with adjustable zero-crossing points. Since  $I_{12} = \pm I_{21}$ , an inverting or non-inverting unity gain current mirror may be used to produce  $I_{21}$  from  $I_{12}$ .

## 2.1. Voltage-Based Circuit

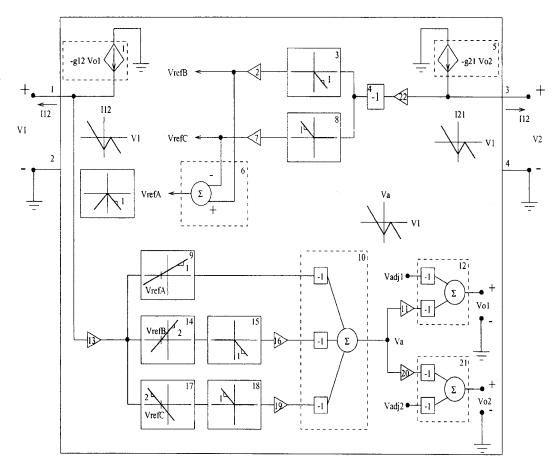

Figure 3 shows the block diagram of the coupling circuit for g < 0. This circuit requires additional circuitry for the g > 0 case. The strategy employed here is to generate an output voltage  $(V_{o1} \text{ and } V_{o2})$  with the same shape as the desired current characteristics but with slopes of  $\pm 1$ . This signal is used to produce the currents via voltage-controlled

Figure 2: Coupling element current  $I_{12}$

$<sup>^{1}</sup>$  sign (x) = -1 for x < 0, 1 otherwise

Figure 3: Block diagram of the voltage-based circuit implementation of the negative coupling circuit. Individual operational amplifier circuits are numbered from 1 to 22. Circuit voltage transfer functions are boxed. Non-boxed graphs show transfer functions for the  $V_2 > 0$  case.

|       |           | $V_{refA}$ | $V_{refB}$ | $V_{refC}$ |

|-------|-----------|------------|------------|------------|

| -g>0  | $V_2 > 0$ | $-V_2$     | $-V_2$     | 0          |

|       | $V_2 < 0$ | $V_2$      | 0          | $-V_2$     |

| g < 0 | $V_2 > 0$ | $-V_2$     | 0          | $V_2$      |

|       | $V_2 < 0$ | $V_2$      | $V_{2}$    | 0          |

Table 1: Required voltage references

current sources. Table 1 indicates the reference voltages required for each stage for both g>0 and g<0. Note that  $V_2$  is processed to produce these reference voltages. The individual circuit elements required are given in Table 2. The voltages  $V_{adj1}$  and  $V_{adj2}$  adjust the offset of the controlling voltages. Precision 1% resistors, high speed National Semiconductor LM6172 operational amplifiers, and 1N4148 switching diodes are used in this design.

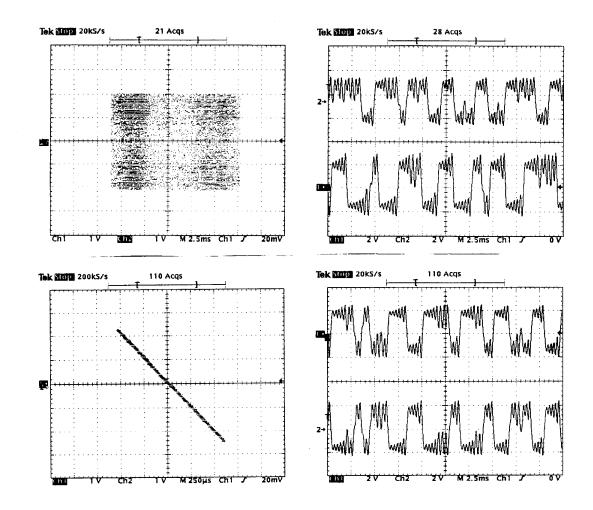

Figure 4 shows experimentally obtained waveforms for coupling two Chua's oscillators with the circuit of Figure 3. The uncoupled case corresponds to (1) removing the connection from the current sources to nodes 1 and 3, (2) connecting the current sources directly to the Chua's circuits, and (3) grounding nodes 1 and 3. This test indicates that the oscillators are not appreciably coupled if the two input voltages to the coupling circuit are equal. The coupled case corresponds to the situation of Figure 1. Note that antisynchronization is achieved.

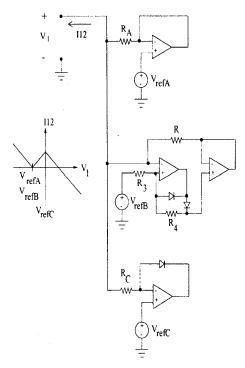

#### 2.2. Current-Based Circuit

The second design is based on producing  $I_{12}$  and then mirroring the resulting current to generate  $I_{21}$ . The basic circuit to generate  $I_{12}$  utilizes a parallel combination of several elements described in [8]. These elements are shown in Figure 5. By setting  $|g| = 1/R_A = (1/2)R_4/(R_3R) =$

Figure 4: XY and time domain plots of the voltages across the Chua's diodes for the uncoupled (top) and negatively coupled (bottom) cases for g = -1 mA/V.

| Circuit Type                        | Numbers     |

|-------------------------------------|-------------|

| Difference Amplifier [6]            | 6,9,14,17   |

| Improved Howland Current Source [7] | 1,5         |

| Improved Precision Rectifier [6]    | 3,8,15,18   |

| Inverting Amplifier [6]             | 4           |

| Summer [6]                          | 10,12,21    |

| Unity Gain Buffer                   | 2,7,11,13,  |

|                                     | 16.19.20.22 |

Table 2: Circuits required for the voltage-based implementation

$1/(2R_C)$  the desired characteristic is obtained. The voltage  $V_2$  is used to set the zero-crossing points of the three circuits via the reference voltages. This requires additional circuitry to connect either  $V_2, -V_2$ , or ground to these reference voltages as in Table 1.  $V_1$  acts as the excitatory input. This approach has not been fully investigated.

### 3. CONCLUSIONS

We have described a voltage and a current based circuit approach to the implementation of a piecewise linear circuit which enables synchronization and anti-synchronization of a pair of Chua's oscillators. Such a circuit may be used to realize the chaotic associative memory described in [4]. Initial experimental results confirm the overall design con-

Figure 5: Schematic of the current-based circuit to generate  $I_{12}$ . The transfer characteristic is for  $V_{REFA} = V_{REFB}$  and  $V_{REFC} = 0$ .

cepts. Further testing is required to verify complete circuit functionality.

The overall goal of our research is to produce an inexpensive and easily built circuit to enable construction of a reasonably sized chaotic associative memory with an eye towards an integrated circuit implementation. The circuit of Figure 3 requires far too many operational amplifiers to meet this need and thus this design may be regarded as a proof-of-concept rather than a practical implementation. The current-based approach should reduce the parts count considerably. Using analog switches to select desired circuit configurations might also lower the number of required components. We are currently designing a discrete component version of the coupling circuit.

## 4. ACKNOWLEDGMENTS

The authors would like to thank Josh Barr and Louise Barr for their work on this project and their assistance in preparing this paper.

#### 5. REFERENCES

- [1] M. P. Kennedy, "Three steps to chaos—part II: A Chua's circuit primer," *IEEE Transactions on Circuits and Systems—Fundamental Theory and Applications*, vol. 40, pp. 657–674, October 1993.

- [2] L. O. Chua, "Chua's circuit: Ten years later," IE-ICE Trans. Fundamentals, vol. E77-A, pp. 1811–1822, November 1994.

- [3] G. Kolumban and G. Kis, "Performance evaluation of FM-DCSK modulation scheme," in *Proc. of the 1998* Int. Symposium on Nonlinear Theory and its Applications (NOLTA'98), vol. 1, (Crans-Montana, Switzerland), pp. 81–84, 1998.

- [4] S. Jankowski, A. Londei, C. Mazur, and A. Lozowski, "Synchronization and association in a large network of coupled Chua circuits," *International Journal of Electronics*, vol. 79, pp. 823–828, December 1995.

- [5] A. Lozowski, T. J. Cholewo, S. Jankowski, and M. Tworek, "Chaotic CNN for image segmentation," in *Proceedings of the 4th International Workshop on Cellular Neural Networks (CNNA'96)*, (Seville, Spain), pp. 219–223, June 24–26 1996.

- [6] A. S. Sedra and K. C. Smith, Microelectronic Circuits. New York: Oxford University Press, 4th ed., 1998.

- [7] T. M. Frederiksen, *Inutitive Operational Amplifiers*. McGraw-Hill Series in Intutitive IC Electronics, New York: McGraw-Hill Book Company, revised ed., 1988.

- [8] L. O. Chua and S. Wong, "Synthesis of piecewise-linear networks," *Electronic Circuits and Systems*, vol. 2, pp. 102–108, July 1978.