# A CMOS IC Nonlinear Resistor for Chua's Circuit

José M. Cruz, Student Member, IEEE, and Leon O. Chua, Fellow, IEEE

Abstract—The first monolithic realization of the nonlinear element in Chua's circuit, now generally called Chua's diode [1], is reported. The element has been fabricated using a CMOS integrated circuit technology. It can be used as the basic nonlinear component for the experimental synthesis of a broad class of circuits, including Cellular Neural Networks, which exhibits an extremely rich variety of bifurcation, chaotic, and nonlinear wave phenomena.

## I. INTRODUCTION

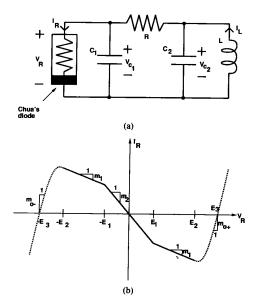

IFURCATION and chaotic phenomena can poten-Btially appear in many nonlinear electronic circuits and most practical circuits are nonlinear to some degree. For investigating complex dynamic phenomena it is advisable to use simple circuit prototypes in which bifurcation and chaotic behavior can be analyzed, simulated and easily verified. Chua's circuit, shown in Fig. 1(a), is the simplest autonomous circuit which exhibits bifurcation and chaotic phenomena. It contains the minimum number of linear storage elements (three) and a single one-port nonlinear resistor (Chua's diode [1]). The circuit has been the focus of extensive studies, with more than fifty papers published since it was discovered in 1984 [2], [3]. It is one of the very few physical systems in which a formal proof of the existence of chaos has been accomplished [4] and in which the theoretical, simulation and experimental results match precisely. These factors have made Chua's circuit a standard paradigm for studying chaotic phenomena.

The voltage-controlled driving-point characteristic of Chua's diode is shown in Fig. 1(b). For voltage signals less than  $E_1$  in absolute value the characteristic has a linear segment with negative slope  $m_2$ . For absolute voltages larger than the breakpoint  $E_1$  the characteristic has two linear segments of negative slope  $m_1$ , with  $|m_1| < |m_2|$ . The piecewise-linear behavior is valid in the nominal range  $(-E_2, E_2)$  in which the diode is normally operated. For voltages outside this range the slope of the characteristic increases monotonically ultimately becoming positive. For large absolute voltages the characteristic lies in the first and third quadrants of the I-V plane.

Until now, Chua's diode has not been available as an

Manuscript received May 7, 1992; revised September 18, 1992. This work was supported in part by a Fulbright/MEC Fellowship, by the National Science Foundation under Grant MIP-9001336, and by the Office of Naval Research under Grant N00014-89-J-1402. This paper was recommended by Associate Editor M. Hasler.

The authors are with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720. IEEE Log Number 9205010.

Fig. 1. (a) Chua's circuit. (b) Driving-point characteristic of Chua's diode.

off-the-shelf component; but has been synthesized using multiple discrete components, like resistors, op amps, diodes, etc. (see [5] for the first implementation and [1] for an extensive bibliography).

In this paper we present the first *monolithic* implementation of Chua's diode as a integrated circuit (IC) device.

This IC device allows us to hook up a chaotic Chua's circuit immediately, without any tuning. It will also facilitate the construction of an entire class of networks based on the same nonlinear element, and exhibiting complex dynamical behavior [6], [7].

This paper is structured as follows. In Section II we present the experimental driving-point characteristic of Chua's diode based on the new IC device. We use the device to build a Chua's circuit, and we show the experimental bifurcation and chaotic phenomena. In Section III we give simulated static and dynamic characteristics of the device. We give a numerical validation of the existence of the Double Scroll chaotic attractor in Chua's circuit when using the new device, and we compare these results with those obtained using an idealized piecewise-linear model of the diode. In Section IV we describe the internal structure of the device and its design in a 2-μm CMOS

technology. Finally, in Section V we give some conclusions.

## II. EXPERIMENTAL PERFORMANCE

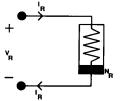

Fig. 2 shows a diagram of the Chua's diode integrated circuit implementation. It consists of the monolithic IC device powered by two floating batteries, with  $V_{\rm CC}=5$  V. The two-terminal Chua's diode can be used in any floating configuration; only the differential voltage  $V_R$  across it is relevant. This IC device has the minimum number of possible external terminals—four.

The experimental results which we present in this paper are for an IC Chua's diode with a fixed driving-point characteristic. The specification parameters of this characteristic (the slopes  $m_1$ , and  $m_2$ , the breakpoint  $E_1$ , and the limit  $E_2$ ) have been chosen to provide robustness for the experimental reproduction of bifurcation and chaotic phenomena in Chua's circuit. In particular, these specifications are  $m_2/m_1=1.9$ ,  $m_1=-0.4$  mA/V,  $E_1=0.7$  V, and  $E_2 \ge 2$  V. The measured values for these parameters for the actual fabricated device are given in Table I.

The device can provide an output power of up to 2.2 mW in the nominal operating range, and up to 5.5 mW if overdriven. The average total power drawn from the batteries is 28 mW. This is less than the typical quiescent supply power of a standard 741 op amp.

In addition to the fixed integrated circuit device, and using a similar internal structure, we have also designed and fabricated five programmable devices. They have additional external terminals which can be used to adjust independently the slopes  $m_1$  and  $m_2$  to  $\pm 50\%$  of the nominal values.

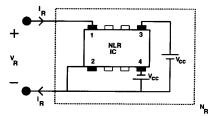

# 2.1. Driving-Point Characteristic

Fig. 3(a) gives the experimental driving-point characteristic of the diode in the nominal operating range. The breakpoints  $-E_1$  and  $E_1$  and the slopes  $m_1$  and  $m_2$  correspond to the nominal values. The maximum relative variation of the current  $I_R$  with respect to the ideal piecewise-linear characteristic is 7%. This driving-point characteristic has been measured to be valid from dc up to frequencies of 100 kHz.

Fig. 3(b) gives the experimental driving-point characteristic of the diode for an extended range. The curve remains in the second and the fourth quadrants of the I-V plane for differential voltages within the battery range  $(-V_{\rm CC}, +V_{\rm CC})$ . For larger absolute voltages the device acts as a passive resistor, as is expected by energy conservation.

## 2.2. Application to Chua's Circuit: Bifurcation Sequence

The functionality of our Chua's diode IC device can be demonstrated by using it experimentally to build Chua's circuit. Different set of values can be used for the linear elements as long as they give a dynamic range for  $V_R$  within the nominal operating range of the diode  $(-E_2, E_2)$ . If we also wish to center the frequency spectrum of Chua's circuit variables in the audio range, a

Fig. 2. Nonlinear IC device: Battery connection.

Fig. 3. Experimental driving-point characteristic of IC device: (a) nominal range (vertical scale: 250  $\mu$ A/division; horizontal scale: 400 mV/division) and; (b) extended range (vertical scale: 500  $\mu$ A/division; horizontal scale: 1 V/division).

TABLE I DC PARAMETERS OF THE IC DEVICE

| Parameter   | Value | Unit         |

|-------------|-------|--------------|

| $m_1$       | -0.41 | mA/V<br>mA/V |

| $m_2$       | -0.78 | mA/V         |

| $E_1^-$     | 0.7   | V            |

| $\hat{E_2}$ | 2.0   | V            |

| $E_3^z$     | 5.0   | V            |

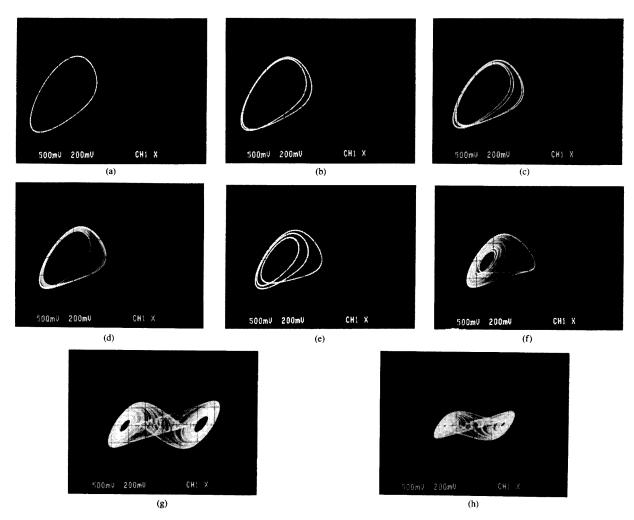

Fig. 4. Experimental  $V_{C2}$  versus  $V_{C1}$  Lissajous figures. Bifurcation sequence for decreasing values of the linear resistance. (Vertical scale: 200 mV/division; horizontal scale is 500 mV/division). (a)  $R=1826~\Omega$ , period one. (b)  $R=1809~\Omega$ , period two. (c)  $R=1782~\Omega$ , period four. (d)  $R=1765~\Omega$ , period n. (e)  $R=1741~\Omega$ , period-three window. (f)  $R=1710~\Omega$ , A Rössler-type chaotic attractor. (g)  $R=1641~\Omega$ , Double Scroll attractor. (h)  $R=1518~\Omega$ , Double Scroll attractor.

corresponding choice of component values is the following:  $C \sim 10^{-8}$  F,  $C_2 \sim 10^{-7}$  F,  $L \sim 10^{-2}$  H, and  $R \sim 10^3$   $\Omega$ . In our case the experimentally measured values of the linear elements used are  $C_1 = 10.02$  nF,  $C_2 = 100.5$  nF, L = 18.81 mH, and the linear resistance R is a variable potentiometer in the range 1-2 k $\Omega$ .

With this experimental circuit we have reproduced the well-known bifurcation and chaotic phenomena of Chua's circuit [4]. Fig. 4 gives the bifurcation sequence obtained when the linear resistor R is decreased from 1.83 to 1.51 k $\Omega$ . It shows first a periodic behavior emerging from a stable equilibrium point, then a period doubling sequence (period-two, period-four, and period n), a period-three window, a Rössler-type chaotic attractor, and finally, a Double Scroll attractor. As R is decreased further the Double Scroll shrinks. After some point the Double Scroll dies and a limit cycle associated with the external positive slope of the nonlinear element is observed.

## III. SIMULATED RESULTS

In this section we give the simulated results of the reported device. We use the circuit simulator Spice3e2 [8] considering all of the parasitic effects and using the transistor models provided by the MOSIS [9] silicon foundry (Orbit).

These simulated numerical results demonstrate the existence of the Double Scroll attractor in Chua's circuit when using the new device. We compare these results with those obtained using an ideal model of Chua's diode. This ideal model has an exact piecewise-linear dc characteristic with the nominal parameters of Table I, and without any reactive limitation due to parasitics.

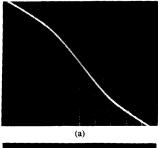

## 3.1. Driving-Point Characteristic

Fig. 5(a) gives the simulated driving-point characteristic for  $V_R$  in the nominal operating range  $(-E_2, E_2)$ . The

solid line represents the simulated characteristic of the actual device. The broken line represents the characteristic of an ideal piecewise-linear model given by

$$\begin{split} I_R &= f_R(V_R) = m_1 V_R \\ &+ \begin{cases} (m_2 - m_1) E_1, & V_R \ge E_1 \\ (m_2 - m_1) V_R, & -E_1 < V_R < E_1 \\ -(m_2 - m_1) E_1, & V_R \le -E_1 \end{cases} \end{split} \tag{1}$$

using the  $m_1$ ,  $m_2$ , and  $E_1$  values of Table I. The maximum deviation in the current for a given voltage occurs at  $V_R = \pm E_1$ . At both points the deviation in the current is 0.035 mA, corresponding to a maximum relative error of 7%, which agrees with the experimental results of the previous section and with the analysis to be presented in subsequent sections. This deviation is symmetrical and, like our experiments and simulations, does not have an appreciable effect on the bifurcation phenomena or on the shape of the attractors in Chua's circuit. The offset, however, can give rise to an asymmetric characteristic and produce a Double Scroll attractor with lobes of different sizes. The actual diode has a small systematic offset, imperceptible in the plot, of 4 mV (which corresponds to an  $I_R = 0.003$  mA for  $V_R = 0$  V). This offset is of the same order of magnitude as the expected random offset due to transistor mismatches in our technological process. The measured  $I_R$ - $V_R$  diode characteristic begins to exhibit high-frequency distortion and hysteresis only at frequencies above 100 kHz.

Fig. 5(b) shows that simulated characteristic for the extended range for the actual device. The shape of the curve outside the range  $(-E_2, E_2)$  is not relevant for the operation of Chua's circuit, and does not need to be defined in the ideal model. The shape coincides exactly with the experimental characteristic of Fig. 3(b) and  $I_R$  crosses through zero at  $V_R = \pm E_3 = \pm V_{CC}$ . The effects which cause this characteristic are discussed in Appendix III.

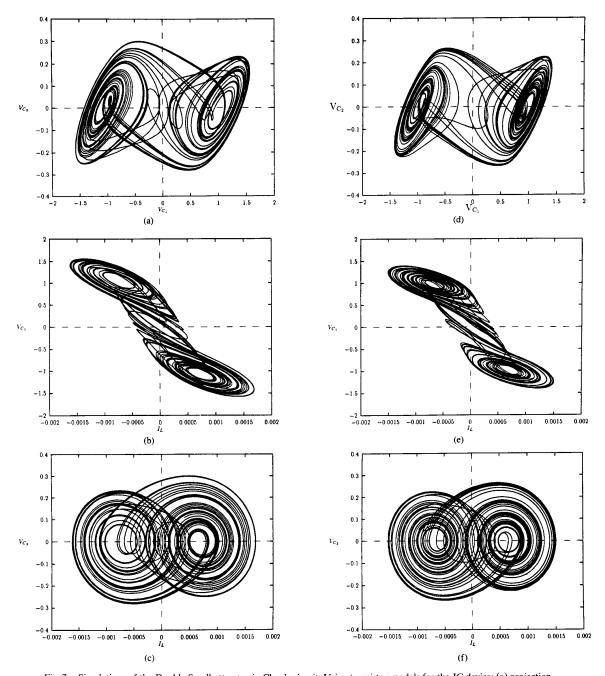

# 3.2. Application to Chua's Circuit

To further validate the suitability of the device we have compared the dynamic behavior of Chua's circuit using the fabricated diode with that obtained by using an idealized model of it. As an example we show the results for the Double Scroll chaotic attractor in Chua's circuit. Fig. 6 shows the transient response obtained by a transistorlevel simulation with Spice3e2 [8] by using the initial condition  $V_{C_1} = 0.1$  and  $V_{C_2} = 0$ . A long trajectory in the  $V_{C_1} - V_{C_2} - I_L$  three-dimensional space is used to represent the shape of the strange attractor. Fig. 7(a)-(c) shows the projections of the strange attractor obtained by a transistor-level simulation which includes all known parasitics of the new IC diode. Fig. 7(d)-(f) shows the projections of the strange attractor obtained by using the idealized piecewise-linear model of the diode (1) with no reactive limitation at all. Essentially identical attractors are obtained in each case.

Fig. 5. (a) Driving-point characteristic in the nominal range. Simulation using the IC device (solid line) and using the ideal piecewise-linear model (discontinuous line). (b) IC device simulation in the extended range  $(-V_{CC}, V_{CC})$ .

Fig. 6. Time-domain simulation of Chua's circuit using transistor models for the IC device. Waveforms of the state variables  $V_1(t)$ ,  $V_2(t)$ , and  $I_1(t)$ .

Fig. 7. Simulations of the Double Scroll attractor in Chua's circuit. Using transistor models for the IC device: (a) projection in the  $(V_{C2}, V_{C1})$  plane; (b) projection in the  $(V_{C1}, I_L)$  plane; (c) projection in the  $(V_{C2}, I_L)$  plane. Using an ideal piecewise-linear model for the IC device: (d) projection in the  $(V_{C2}, V_{C1})$  plane; (e) projection in the  $(V_{C1}, I_L)$  plane; (f) projection in the  $(V_{C2}, I_L)$  plane.

# IV. CIRCUIT DESIGN

In this section we describe the actual design procedure for the four-terminal device. We first present the internal structure of the device and outline the design considerations that have been taken into account for an implementation with a 2- $\mu$ m p-well double-poly double-metal CMOS technology. Then we discuss limitations and possible improvements. We conclude by comparing this implementation with others which have been proposed.

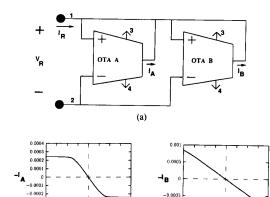

The device is based on only two operational transconductance amplifiers (OTA's), as indicated in Fig. 8(a). This

implementation, unlike previous ones, do not require additional elements like resistances or diodes, which are not appropriate for CMOS VLSI implementation. The problem is reduced to the design of two adequate transconductance amplifiers. The intrinsic nonlinear behavior of one of these amplifiers is used to generate the nonlinearity of the driving-point characteristic. This enables us to obtain high-frequency responses using a small silicon area [11]. These transconductance amplifiers, unlike standard op amps, have only one stage, do not require internal compensation [12] and the amplifier gains can be controlled externally, if desired, permitting programmability.

The driving-point characteristic given in (1) is obtained by using two amplifiers exhibiting transconductance characteristics given ideally by

$$f_{A}(V_{R}) = \begin{cases} m_{A}E_{1}, & V_{R} \ge E_{1} \\ m_{A}V_{R}, & -E_{1} < V_{R} < E_{1} \\ -m_{A}E_{1}, & V_{R} \le -E_{1} \end{cases}$$

(2)

$$f_B(V_R) = m_B V_R. (3)$$

The piecewise-linear characteristic  $f_A$  corresponds to OTA A and the linear characteristic  $f_B$  to OTA B. If the open loop output resistance of the OTA's are large enough (see Appendix I for requirements) the new parameters  $m_A$  and  $m_B$  should be set to

$$m_A = m_1 - m_2 = -0.41 \text{ mA/V} + 0.78 \text{ mA/V}$$

= 0.37 mA/V

$m_B = -m_1 = 0.41 \text{ mA/V}.$  (4)

In our design we try to obtain transfer characteristics for the amplifiers which are close to the ideal models of (2) and (3) and to minimize the effects of parasitic dynamics.

We have based our design on a simple input differential pair structure as it gives the maximum effective frequency response and minimal input noise. To minimize the offset and increase the output swing we use a symmetrical configuration with three current mirrors. These current mirrors contain cascode devices to increase the output resistance of the amplifiers in the nominal range of operation.

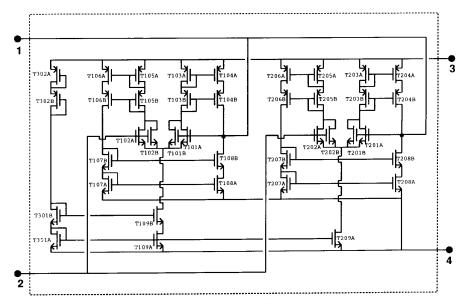

The complete schematic of the circuit is shown in Fig. 9. A large-signal analysis of this circuit is performed in Appendix II. The resulting driving-point characteristic is given by

$$I_{R} = f(V_{R}) = -m_{B}V_{R}\sqrt{1 - \left(\frac{V_{R}}{2\sigma}\right)^{2}}$$

$$-\begin{cases} m_{A}E_{1}, & V_{R} \geq \sqrt{2}E_{1} \\ m_{A}V_{R}\sqrt{1 - \left(\frac{V_{R}}{2E_{1}}\right)^{2}}, & -\sqrt{2}E_{1} < V_{R} < \sqrt{2}E_{1} \\ -m_{A}E_{1}, & V_{R} \leq -\sqrt{2}E_{1}. \end{cases}$$

(5)

The first term is due to OTA B and the second to OTA

(b) (c)

Fig. 8. Nonlinear resistor OTA-based structure with simulated dc characteristic of each OTA in positive feedback configuration.

A. The parameters  $m_A$  and  $m_B$  are the small-signal transconductances of the amplifiers at the origin; they are set to the ideal values given in (4). The new parameter  $\sigma$  has been set to 2.4, providing a quasilinear behavior of OTA B in the nominal range. Fig. 8(b) and (c) gives a plot with the current contribution of each amplifier in the nominal range. The limit current of OTA A is the same as in the ideal case  $(\pm m_A E_1)$ , but is not reached until  $|V_R| = \sqrt{2} E_1$ . At the voltages that we define as breakpoints  $(\pm E_1)$  the output current of OTA A is  $(1 - \sqrt{3/4})I_A$ . The maximum current difference between both the ideal function and the actual one (5) occurs at the breakpoints. The maximum relative error is given approximately by

$$\frac{\delta I}{I} = \frac{m_1 - m_2}{-m_2} \left( 1 - \sqrt{3/4} \right) = 6.2\% \tag{6}$$

which agrees with the experimental and simulated results obtained previously. Our experiments confirm that this small error has little noticeable effect on the bifurcation phenomena or on the shape of the attractors. This relative error could be reduced using linearization techniques of the differential pair to produce sharper corners at the expense of more circuitry, for example by modulating the value of the bias current [13]. However, the additional circuitry will inevitably increase the noise and reduce the frequency at which dynamic distortion (including hysteresis) begins to appear. These effects are detrimental to applications of the Chua diode.

The technological data for the process in which this device has been integrated are summarized in Table II. Using (13), (14), and (17) (see Appendix II) we obtain the main design equations for calculating the input transistor ratio sizes and bias currents:

$$\frac{W_A}{L_A} = \frac{1}{\mu_n C_{ox}} \frac{m_A}{E_1}$$

$$\frac{W_B}{L_B} = \frac{1}{\mu_n C_{ox}} \frac{m_A}{\sigma}$$

Fig. 9. Transistor schematic.

$$I_A = m_A E_1$$

$$I_B = m_B \sigma.$$

(7)

Additional design equations for transistor sizing are given by output swing requirements and to obtain enough headroom for the current sources. These equations are derived from large-signal conditions for maintaining all transistors out of the triode mode. For the final sizing we use computer simulations to consider corrections for bulk effect and channel length modulations [10].

Table III gives the drawn dimensions for the complete schematic shown in Fig. 9. For the differential pair input transistors we have used a relatively large area to reduce the flicker noise. Their values are  $W_A/L_A = 2 \times 30/6$ and  $W_B/L_B = 2 \times 15/6$ . For the current mirrors we have used unity current gain to maximize their frequency response. The W/L ratios of the current mirror transistors are as large as 100 in the case of OTA B. Throughout we have used transistor lengths greater than 4  $\mu$ m to reduce mismatch and flicker noise. We only use minimum length dimensions in the cascode devices as they do not contribute to the offset and noise. In the fixed IC device the bias currents are  $I_A = 0.235$  mA and  $I_B = 1.00$  mA. They are generated by the bias circuitry shown at the left of the schematic. The ratio  $m_2/m_1$  is to first order independent of variations in the process parameters  $\mu C_{\text{ox}}$  and  $V_{\text{th}}$ . The absolute values of  $m_2$  and  $m_1$  depend on these parameters but can, if desired, be compensated by simply adjusting the power supply voltages of the device. The larger the power supply voltage the more negative will be the slopes  $m_1$  and  $m_2$ , maintaining the ratio  $m_2/m_1$  constant.

This IC nonlinear device can be operated without dynamic distortion at higher frequencies than previous implementations. The hysteresis phenomena at frequencies above 100 kHz is caused caused mainly by a delay of

TABLE II TECHNOLOGICAL DATA

| Parameter                   | n-channel | p-channel | Unit                         |

|-----------------------------|-----------|-----------|------------------------------|

| V.,                         | 1.0       | 0.8       | v                            |

| $V_{ m th} \ \mu C_{ m ox}$ | 47        | 23        | $\frac{\mu A}{\sqrt{V}}/V^2$ |

| γ                           | 1.06      | 0.45      | $\sqrt{\mathbf{V}}$          |

| $\dot{\Delta}L$             | 0.54      | 0.42      | $\mu$ m                      |

| $\Delta W$                  | 0.07      | 0.17      | $\mu$ m                      |

TABLE III

MASK DEVICE DIMENSIONS

| Device                                                                                                                                        | W ( μm) | L ( μm) |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|

| $T_{101A}, T_{101B}, T_{102A}, T_{102B}$                                                                                                      | 30      | 6       |

| $T_{103A}$ , $T_{104A}$ , $T_{105A}$ , $T_{106A}$ , $T_{107A}$ , $T_{108A}$                                                                   | 280     | 4       |

| $T_{103B}, T_{104B}, T_{105B}, T_{106B}, T_{107B}, T_{108B}$                                                                                  | 280     | 2       |

| $T_{109A}$                                                                                                                                    | 100     | 6       |

| $T_{109B}^{109A}$                                                                                                                             | 100     | 2       |

| $T_{201A}^{109B}, T_{201B}, T_{202A}, T_{202B}$                                                                                               | 15      | 6       |

| $T_{201A}^{201B}, T_{201B}^{201B}, T_{202B}^{202B}, T_{203A}^{2001B}, T_{204A}^{2001B}, T_{206A}^{2001B}, T_{207A}^{2001B}, T_{208A}^{2001B}$ | 400     | 4       |

| $T_{203B}^{203A}, T_{204B}^{204A}, T_{205B}^{205A}, T_{206B}^{206A}, T_{207B}^{207A}, T_{208B}^{208A}$                                        | 400     | 2       |

|                                                                                                                                               | 476     | 6       |

| $T_{209A}$                                                                                                                                    | 50      | 10      |

| $T_{301A}$                                                                                                                                    | 100     | 10      |

| $T_{301B} \ T_{302A}, T_{302B}$                                                                                                               | 20      | 10      |

about 5 ns when the current mirrors of OTA A switch off at the breakpoint  $E_1$  crossing. An improvement can be achieved by using common current mirrors for both OTA's. In this case all of the current mirror transistors are always in saturation mode and only a transistor of the input differential pair of OTA A can switch off.

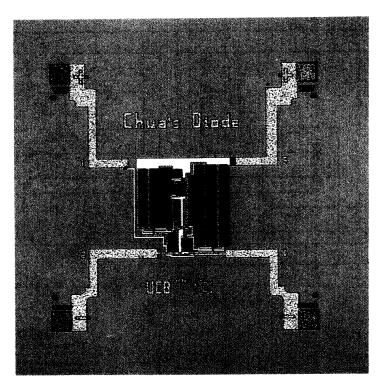

Fig. 10 shows the chip micrograph of the integrated Chua's diode. The device has four external terminals (the minimum possible) and provides a fixed driving-point characteristic. We have used the same orientation for all the transistors to reduce mismatch. The input differential pairs have been laid out in a common centroid configura-

Fig. 10. Chip micrograph.

tion to minimize input offset due to threshold voltage variations. The IC device occupies an area of about  $0.5\,\mathrm{mm^2}$ , and the total die size including the bonding pads is  $1.3\times1.3\,\mathrm{mm}$ . This chip has been encapsulated in 8-pin DIP package (only the four corner terminals are used, as was indicated in Fig. 2). This package is 0.3-in wide and 0.1-in interlead. It can be hooked into standard breadboards or opamp sockets. A photograph of the packaged chip is shown in Fig. 11, and that of the Chua's circuit incorporating this chip is shown in Fig. 12.

# V. Conclusions

In this paper we have presented an IC implementation of the nonlinear resistor in Chua's circuit. It is integrated in a 2- $\mu$ m CMOS process. This is the first monolithic implementation of such a resistor, and eliminates the need for several discrete components. The small silicon area required (less than a square millimeter) makes the implementation cheap. It also open the possibility of integrating in a single chip large Cellular Neural Networks [7] made of coupled Chua's circuits to reproduce wave propagation phenomena [6] and spatio-temporal chaos.

Presently we are developing a version of the device to be powered by a single 9-V battery. The use of one voltage source instead of two is possible by integrating additional circuitry generating a low impedance intermediate voltage at node 2 from the voltages at terminals 3

Fig. 11. Photograph of the packaged chip.

and 4, which are then connected to the single voltage source.

We plan to make the device available as the first off-the-shelf Chua's diode. We hope that this chip will make it easier for researchers to build and explore simple circuits exhibiting a wide spectrum of complex dynamic phenomena.

# APPENDIX I EFFECT OF FINITE OUTPUT RESISTANCE

To account for the finite value of the output resistance of the amplifiers, (4) should be replaced by the following:

$$m_1 = \frac{1 - m_B r_{o_B}}{r_{o_R}} + \frac{1}{r_{o_R}} + \frac{1}{r_{o_A}}$$

(8)

$$m_2 = \frac{1 - m_A r_{o_A}}{r_{o_A}} + \frac{1 - m_B r_{o_B}}{r_{o_B}} + \frac{1}{r_{o_B}} + \frac{1}{r_{o_A}}$$

(9)

where  $r_{o_A}$  and  $r_{o_B}$  are the small signal output resistances of OTA A and OTA B. This can introduce nonlinear distortion due to the fact that  $r_{o_A}$  and  $r_{o_B}$  are in general not constant but depend nonlinearly on the output current (and on the output voltage itself when in feedback configuration). To prevent this nonlinear phenomenon from affecting the driving-point characteristic in the nominal range we have designed the amplifier such that  $r_{o_A}(V_R), r_{o_A}(V_R) \gg 1/m_1, 1/m_2$  for  $V_R \in (-E_2, E_2)$ . In this

$$m_1 \approx -m_B$$

$$m_2 \approx -m_A - m_B. \tag{10}$$

# APPENDIX II DESIGN EQUATIONS

In the nominal range, all transistors are in the saturation or in the cut-off mode. For an MOS transistor in saturation we consider the following formula which neglects the bulk effect and channel modulation effects:

$$I = \frac{\mu C_{\text{ox}}}{2} \frac{W_A}{L_A} (V_{\text{GS}} - V_{\text{th}})^2.$$

(11)

The differential current of the differential pair of OTA A as function of the input differential voltage  $V_R$  and the bias current  $I_A$  is then given by

Fig. 12. Chua's circuit using the Chua's diode IC.

The maximum and minimum value of  $\Delta I$  are  $\pm I_4$ . As with the ideal model, we define the breakpoint  $E_1$  as

$$E_1 = \frac{I_A}{m_A} = \sqrt{\frac{I_A}{\mu C_{\text{ox}} \frac{W_A}{L_A}}}$$

(14)

Equation (12) is rewritten as

$$g_A(V_R)$$

$$= \begin{cases} m_{A}E_{1}, & V_{R} \geq \sqrt{2}E_{1} \\ m_{A}V_{R}\sqrt{1 - \left(\frac{V_{R}}{2E_{1}}\right)^{2}}, & -\sqrt{2}E_{1} < V_{R} < \sqrt{2}E_{1} \\ -m_{A}E_{1}, & V_{R} \leq -\sqrt{2}E_{1}. \end{cases}$$

(15)

$$g_{A}(V_{R}) = \begin{cases} I_{A}, & V_{R} \geq \sqrt{\frac{2I_{A}}{\mu C_{ox} \frac{W_{A}}{L_{A}}}} \\ \sqrt{\mu C_{ox} \frac{W_{A}}{L_{A}} I_{A}} V_{R} \sqrt{1 - \mu C_{ox} \frac{W_{A}}{L_{A}} \frac{1}{4I_{A}} V_{R}^{2}} - \sqrt{\frac{2I_{A}}{\mu C_{ox} \frac{W_{A}}{L_{A}}}} < V_{R} < \sqrt{\frac{2I_{A}}{\mu C_{ox} \frac{W_{A}}{L_{A}}}} \\ -I_{A}, & V_{R} \leq -\sqrt{\frac{2I_{A}}{\mu C_{ox} \frac{W_{A}}{L_{A}}}} \end{cases}$$

(12)

The slope of the function at the origin is denoted as in the ideal piecewise-linear model by  $m_A$  and is given by

$$m_A = g_A'(0) = \sqrt{\mu C_{\text{ox}} \frac{W_A}{L_A} I_A}$$

(13)

The output current at the breakpoint is then given by

$$g_A(E_1) = I_A(1 - \sqrt{3/4}).$$

(16)

For OTA B the same equation (15) applies, but replac-

ing the slope  $m_A$  and the breakpoint  $E_1$  by

$$m_B = \sqrt{\mu C_{\text{ox}} \frac{W_B}{L_B} I_B}$$

$$\sigma = \frac{I_B}{m_B} = \sqrt{\frac{I_B}{\mu C_{\text{ox}} \frac{W_B}{L_B}}}.$$

(17)

#### APPENDIX III

# CHARACTERISTIC OUTSIDE THE NOMINAL RANGE

Outside the nominal operating range the following effects occur:

First, the nonlinear distortion of amplifier B is appreciable for  $|V_R| > E_2$ . Gain compression causes the slope of Chua's diode characteristic to become less negative as  $|V_R|$  increases. This effect is dominant in the range  $|V_R| \in (2 \text{ V}, 3 \text{ V})$ .

Second, for voltages near the power supply rails the output resistance of the OTA's drop dramatically as their output transistors enter in their triode region. The approximation in (10) is no longer valid.

Let us consider the case of large positive voltages  $V_R$ . For large input voltages the differential pair is switched off, and there is no current flowing through the lower current mirror. All of the output current of the OTA flows though the upper current mirror. However, as the output voltage increases the transistors enter the triode mode and the output current decreases to zero when  $V_R = V_{CC}$ . The slope of the curve at that point is given by

$$m_{o+} = f_R'(V_{CC}) = \sqrt{\mu_p C_{ox} \frac{W_{104A}}{L_{104A}} I_A} + \sqrt{\mu_p C_{ox} \frac{W_{204A}}{L_{204A}} I_B}$$

(18)

It can be related to  $m_1$  and  $m_2$  by using (10), (13), and (17):

$$m_{o+} = m_A \sqrt{\frac{\mu_p}{\mu_n} \frac{\frac{W_{104A}}{L_{104A}}}{\frac{W_A}{L_A}}} + m_B \sqrt{\frac{\mu_p}{\mu_n} \frac{\frac{W_{204B}}{L_{204B}}}{\frac{W_B}{L_B}}}$$

$$= +1.87m_A + 3.16m_B \tag{19}$$

$$m_{o+} = -1.29m_1 - 1.87m_2 = +1.99 \text{ mA/V}.$$

(20)

Similarly for  $V_R = -V_{CC}$  we obtain

$$m_{o-} = f_R'(-V_{CC})$$

$$= \sqrt{\mu_n C_{ox} \frac{W_{108A}}{L_{108B}} I_A} + \sqrt{\mu_n C_{ox} \frac{W_{208A}}{L_{208A}} I_B}. \quad (21)$$

It can be related to  $m_1$  and  $m_2$  by

$$m_{o-} = m_A \sqrt{\frac{\frac{W_{108A}}{L_{108A}}}{\frac{W_A}{L_A}}} + m_B \sqrt{\frac{\frac{W_{208B}}{L_{208B}}}{\frac{W_B}{L_B}}}$$

$$= +2.64m_A + 4.47m_B \qquad (22)$$

$$m_{o-} = -1.83m_1 - 2.64m_2 = +2.81 \text{ mA/V} \qquad (23)$$

Third, for  $V_R$  outside the supply voltages range the positive slope of the device increases even more as one of the p-n junctions of the output transistors becomes forward biased, causing a positive exponential component which depends on  $|V_R-V_{\rm CC}|$ . For values  $|V_R-V_{\rm CC}|$  of about 0.8 V, the very large positive slope finally becomes limited by the nonzero series resistance of the batteries.

# APPENDIX IV PROGRAMMABLE DEVICES

We have also integrated a chip containing Chua's diodes with programmable characteristics. In them the currents  $I_A$  and  $I_B$  are controlled by additional external terminals. The control of these currents gives two degrees of freedom in the three dimensional space formed by  $m_1$ ,  $m_2$ , and  $E_1$ , which are the main parameters of the device.

$$m_1 = K_1 \sqrt{I_B}$$

$m_2 = K_1 \sqrt{I_B} + K_2 \sqrt{I_A}$

$E_1 = K_3 \sqrt{I_A}$ . (24)

The proportionality constants are derived from (4), (13), (14), and (17). They are given by

$$K_{1} = \sqrt{\mu_{n}C_{\text{ox}}\frac{W_{B}}{L_{B}}}$$

$$K_{2} = \sqrt{\mu_{n}C_{\text{ox}}\frac{W_{A}}{L_{A}}}$$

$$K_{3} = \sqrt{\frac{1}{\mu_{n}C_{\text{ox}}\frac{W_{A}}{L_{A}}}}.$$

(25)

The currents  $I_A$  and  $I_B$  are controlled by voltages across diode-connected transistors, allowing linear incremental control of  $m_1$ ,  $m_2$ , and  $E_1$ .

The valid range of operation of the amplifier also depends on the control currents. That range is maximum around the nominal values of Table I. For lower control current  $I_B$  the harmonic distortion of OTA B increases. For large control currents  $I_A$  or  $I_B$  the decrease in the output swing of the amplifiers limits the valid range of operation.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. R. Brodersen for providing the silicon integration resources (MOSIS), Dr.

M. P. Kennedy for useful discussions, and K. S. Halle for building a demonstration circuit using the new IC device.

#### REFERENCES

- [1] M. P. Kennedy, "Robust op amp realization of Chua's circuit," Frequenz, vol. 46, no. 3-4, pp. 66-80, Mar.-Apr. 1992. T. Matsumoto, "A chaotic attractor from Chua's circuit," IEEE

- Trans. Circuits Syst., vol. CAS-31, pp. 1055-1058, 1984.

- L. O. Chua, "The genesis of Chua's circuit," Archn für Elektronik und Übestragungstechnik, vol. 46, no. 4, pp. 250–257, 1992. L. O. Chua, M. Komuro, and T. Matsumoto, "The Double Scroll

- family-Parts I and II," IEEE Trans. Circuits syst., vol. CAS-33, pp. 1073-1118, 1986.

- G. Q. Zhong and F. Ayrom, "Experimental confirmation of chaos from Chua's circuit," *Int. J. Circuit Theory Appl.*, vol. 13, no. 11, pp. 93-98, 1985

- V. Perez-Munuzuri, V. Perez-Villar, and L. O. Chua, "Propagation failure in linear arrays of Chua's circuits," Int. J. Bifurcation and Chaos, vol. 2, no. 2, pp. 403-406, June 1992.

- Leon O. Chua and Lin Yang, "Cellular neural networks: Theory," IEEE Trans. Circuits Syst., vol. 35, pp. 1257-1272 Oct. 1988.

- [8] B. Johnson, T. Quarles, A. R. Newton, D. O. Pederson, and A. Sangiovanni-Vincentelli, "SPICE Version 3e User's Manual," Dept. EECS, Univ. of California at Berkeley, April 1991

- C. Tomovich, Ed., "MOSIS User Manual. Release 3.1," The MO-SIS Service, Univ. of Southern California, Los Angeles, 1991.

- [10] D. A. Hodges, P. R. Gray, and R. B. Broderson, "Potential of MOS technologies for analog integrated circuits," IEEE J. Solid-State Circuits, vol. SC-13, pp. 285-293, June 1978.

- [11] J. M. Cruz and L. O. Chua, "A CNN chip for connected component detection," IEEE Trans. Circuits Syst., vol. 38, pp. 812-817, July 1991.

- [12] E. Sanchez-Sinencio, J. Ramirez-Angulo, B. Linares-Barranco, and A. Rodriguez-Vazquez, "Operational transconductance amplifierbased nonlinear function syntheses," IEEE J. Solid-State Circuits, vol. 24, pp. 1576-1586, Dec. 1989.

- [13] A. Nedungadi and T. R. Viswanathan, "Design of linear CMOS transconductance Elements," IEEE Trans. Circuits Syst., CAS-31, pp. 891-894, 1984.

José M. Cruz (S'88) was born in Sevilla, Spain. He received the B.S. degree in physics from the University of Sevilla in 1987, and the Master of Engineering degree (with distinction) from the Katholieke Universiteit Leuven, Belgium, in 1990. Since 1990 he is with the Department of Electrical Engineering and Computer Sciences of the University of California at Berkeley, where he is working towards the Ph. D. degree.

In 1987 and 1988 he was a research and teaching assistant at the University of Sevilla.

He has been with the National Center of Microelectronics of Spain and,

from 1989 to 1990, with the E.S.A.T. Laboratory of the K.U. Leuven, Heverlee, Belgium. His current research interests are in the integrated design of nonlinear and neural networks.

Mr. Cruz is a Fulbright Fellow.

Leon O. Chua (S'60-M'62-SM'70-F'74) received the S.M. degree from the Massachusetts Institute of Technology in 1961 and the Ph.D. degree from the University of Illinois, Urbana, in 1964. He was also awarded a Doctor Honoris Causa from the Ecole Polytechnique Federale-Lausanne, Switzerland, in 1983, an Honorary Doctorate from the University of Tokushima, Japan, in 1984, and an Honorary Doctorate from the Technische Universitat Dresden in 1992.

He is presently a professor of Electrical Engineering and Computer Sciences at the University of California, Berkelev. Professor Chua's research interests are in the areas of general nonlinear network and system theory. He has been a consultant to various electronic industries in the areas of nonlinear network analysis, modeling, and computer-aided design. He is the author of Introduction to Nonlinear Network Theory (New York: McGraw-Hill, 1969), and a coauthor of the books Computer-Aided Analysis of Electronic Circuits: Algorithms and Computational Techniques (Englewood Cliffs, NJ: Prentice-Hall, 1975), Linear and Nonlinear Circuits (New York: McGraw-Hill, 1987), and Practical Numerical Algorithms for Chaotic Systems (New York: Springer-Verlag, 1989). He has published many research papers in the area of nonlinear networks and systems. He served as Editor of the IEEE Transactions on Circuits and Systems from 1973 to 1975 and as the President of the IEEE Society on Circuits and Systems in 1976. He is presently the editor of the International Journal of Bifurcation and Chaos and a deputy editor of the International Journal of Circuit Theory and Applications.

Professor Chua is the holder of five U.S. patents. He is also the recipient of several awards and prizes, including the 1967 IEEE Browder J. Thompson Memorial Prize Award, the 1973 IEEE W. R. G. Baker Prize Award, the 1974 Frederick Emmons Terman Award, the 1976 Miller Research Professorship from the Miller Institute, the 1982 Senior Visiting Fellowship at Cambridge University, England, the 1982/83 Alexander von Humboldt Senior U.S. Scientist Award at the Technical University of Munich, W. Germany, the 1983/84 Visiting U.S. Scientist Award at Waseda University, Tokyo, from the Japan Society for Promotion of Science, the IEEE Centennial Medal in 1985, the 1985, the 1985 Myril B. Reed Best Paper Prize, and both the 1985 and 1989 IEEE Guillemin-Cauer Prize. In the fall of 1986, he was awarded a Professor Invité International Award at the University of Paris-Sud from the French Minstry of Education.